在学习Verilog硬件编程语言时,写完一个module,仍需要进行仿真下看是否运算结果正确,像高级语言中可以打印在Windows上,单片机编程时可以用串口打出来数据一样,我们仍需要验证我们写的对不对。

如果你对你的硬件水平非常自信,那可以编程完后直接弄出RTL电路来,看是否真确。

如果电路看不懂,那就可以用波形图进行仿真。

准备工具:

一个正确无误的module(最好别有Warnning)、工程下建立一个.vwf文件(that‘s all)。

下面我们拿例子说话:

这是一个8-3优先编码器,最高位优先级最高。

然后打开我们的.vwf

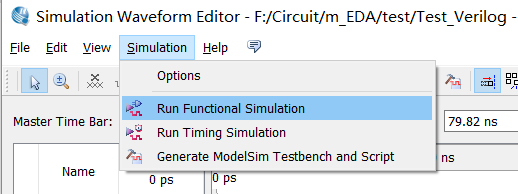

然后:

咱看下结果:

符合代码吧,从左到右第四位数是0,那么编码为3.

我们再看一个时序图的仿真案例:

1339

1339

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?