数字集成电路:MOS管器件章(一)

在学习数字集成电路的过程中,相信很多小伙伴,尤其是偏数字方向的小伙伴们常常会被浩如烟海的概念和令人头皮发麻的公式绕晕,而对底层器件的学习较为忽视,觉得现代数字设计不就是写写代码,写写脚本,底层的东西不怎么需要懂。事实上,对底层器件的把握,是对芯片设计指标优化的基础,忽视底层构建系统,在遇到问题和需要细致分析时往往会比较乏力。本节以伯克利开源课程EE141的材料为基础,尽量用形象的语言和描述来描述一个底层MOS管的工作原理,而非简单的罗列公式,希望能够帮助大家温故知新。

从一个MOS管说起

在现代集成电路工艺中,金属氧化物半导体,即MOS管已经成为了最主流的集成电路构建基本单元,对于设计者而言,明白一个基础单元的工作原理可以称得上是集成电路设计中的第一性原理。

晶体管的三维结构

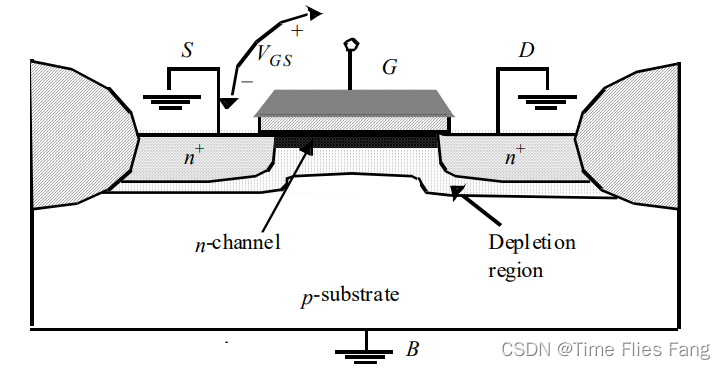

下图是一个NMOS的剖面图,我们可以看出,MOS管是一个四端器件,其结构是在P衬底上加工两个N掺杂区,两片N掺杂区分别用金属引出,成为源极(S)和漏极(D)。同时,在硅衬底上加工一层薄薄的二氧化硅,又称为栅氧层,起到绝缘的作用,在这层栅氧层上加工多晶硅(poly),即成为了栅极(G),最后一端是在衬底体端(Bulk)。

由于两片N掺杂区的形成,在没有外部控制电压的时候,N掺杂区与P衬底之间会形成像二极管中的PN结,在空间上被称为耗尽层 Depletion Region。MOS管神奇的地方在于,如果在GS之间添加控制电压Vgs,由于绝缘层的存在,栅极此刻相当于一个电容器,并且由于同性相斥,会将正电荷向衬底的底部推,而同时吸引负电荷,即自由电子,来到栅极电极板附近,当Vgs越来越高时,在靠近栅极的区域,原本P衬底中的多子正电荷逐渐减少,取而代之的是自由电子,半导体物理理论推导表明,当Vgs大于某个阈值电压之后,将形成一个充满自由电子的区域,这个区域的多子与衬底的掺杂是相反的,因此我们称这片区域为反型层,反型层形成之前,DS之间是不导通的,只有在形成反型层后DS间才存在可以导通的自由电子,而Vgs又可以控制反型层的形成,这也是数字电路中MOS管开关效应的基本原理。

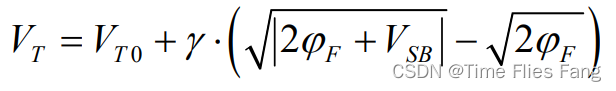

我们写出阈值电压VT的公式,这里我们忽略其他变量,只看VSB,这是晶体管体端和源端之间的压差,不难理解,如果体端是正电位,对要被吸引到栅极附近的自由电荷是吸引作用,或者说是阻碍自由电子前往栅极,因此需要更大的VT才能形成导电沟道。这一特性可以用来调控MOS管VT的大小,而事实上VT的大小又会影响门电路的延时,功耗等一系列性能参数,所以说数字标准库单元中常见的HVT, RVT, LVT就是通过调控VSB来调控阈值电压大小,进而调节延时功耗等参数的。

源漏导通状态下的MOS管

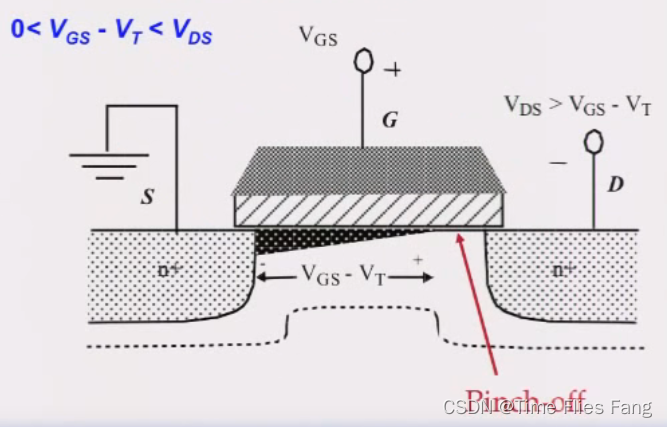

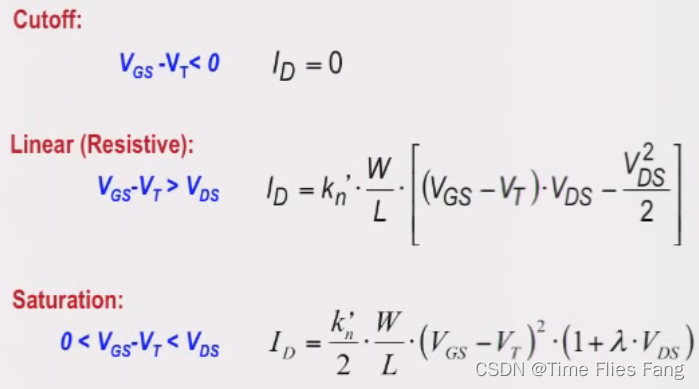

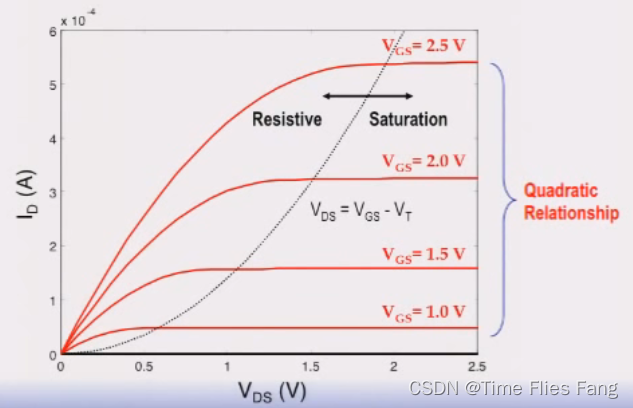

形成了导电沟道之后,如果我们在漏源之间添加电压,自由电子就可以定向流动,形成电流,直觉上看,Vds线性增大,Ids也应该线性增大才对,但是MOS管有另一个特性,如下图所示,当Vds大到一定程度时,在靠近D端的导电沟道会越来越窄,乃至完全消失,形成一个夹断的状态。出现这个现象的原因也很好理解,VGD之间已经小于VT了,无法再形成有效的导电沟道,且越靠近D端,这一现象越明显。在数学上表达,就是VGD<VT,或者教材中更常用的VDS > VGS - VT。此时由于VGS仍大于VT,导电沟道仍然存在,且电流仍然能够从S到D,只不过持续增大VDS时,大部分能量都要用来克服夹断,电流就不再能线性地增大了。此时MOS管所在的工作区被称为饱和区,导电沟道未被夹断的工作区由于Ids随着Vds近似线性增大,所在的工作区被称为线性区,而在VGS<VT,即导电沟道未形成时,所在的工作区被称为截断区

我们用三条公式和一张图就可以把上述的定义搞清楚:k’n是跨导参数,W/L是晶体管的宽长比,一般晶体管的长度都是最小特征尺寸,因此宽度可以决定晶体管的导电能力,除了这两项以外,Id还跟VGS-VT以及VDS有关系,在不同的工作区遵循不同的建模关系。

MOS管仅仅如此吗?

上述内容,相信认真学习了电类相关专业本科课程的同学即使不是了如指掌,也应该是较为熟悉,似乎并不是很难,然而,现实世界总是复杂而多变的,随着工艺节点的进步,人们渐渐发现,这种在长沟道假设下简单的建模正在失效,取而代之的,是更加复杂的短沟道模型,本节将介绍短沟道模型产生的原因与变化。

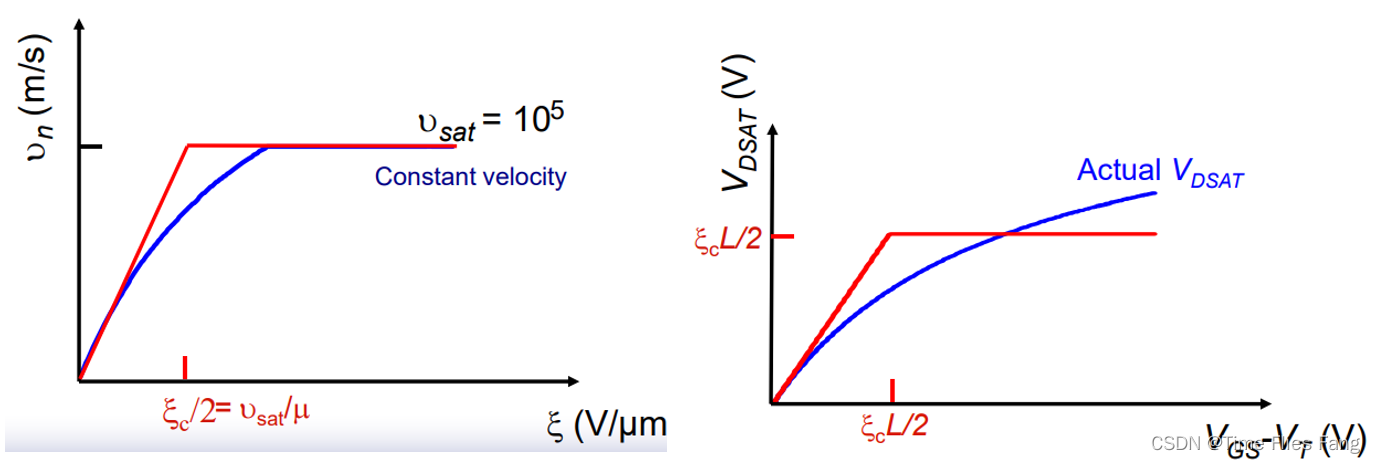

短沟道效应:速度饱和

简单来讲,短沟道效应出现的原因来源于速度饱和的物理现象,当电场强度不断增大时,载流子的流动速度并不会像想象中的那样也无限增大,而是会趋向于一个饱和值,这跟载流子与介质之间的碰撞有关系。随着工艺制程提高,沟道长度越来越短,在电压不变的情况下,电场强度却在增强,因此速度饱和现象也越来越明显,之前的建模也就不再适用,我们把这种现象称之为短沟道效应,短沟道模型跟长沟道模型的不同点主要体现在两方面:

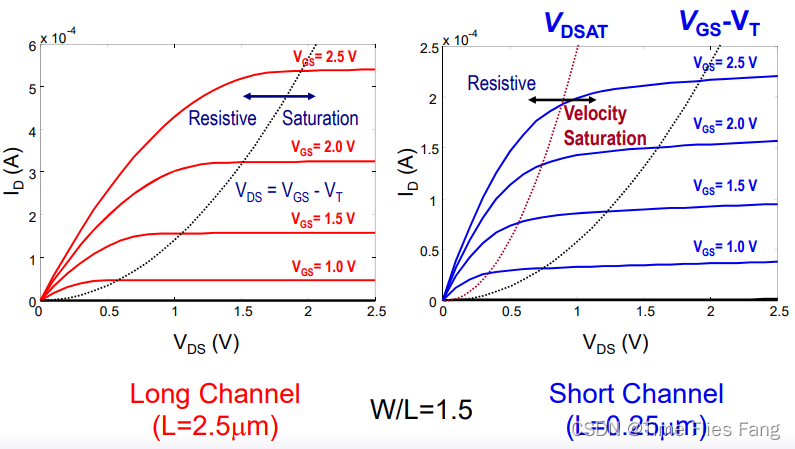

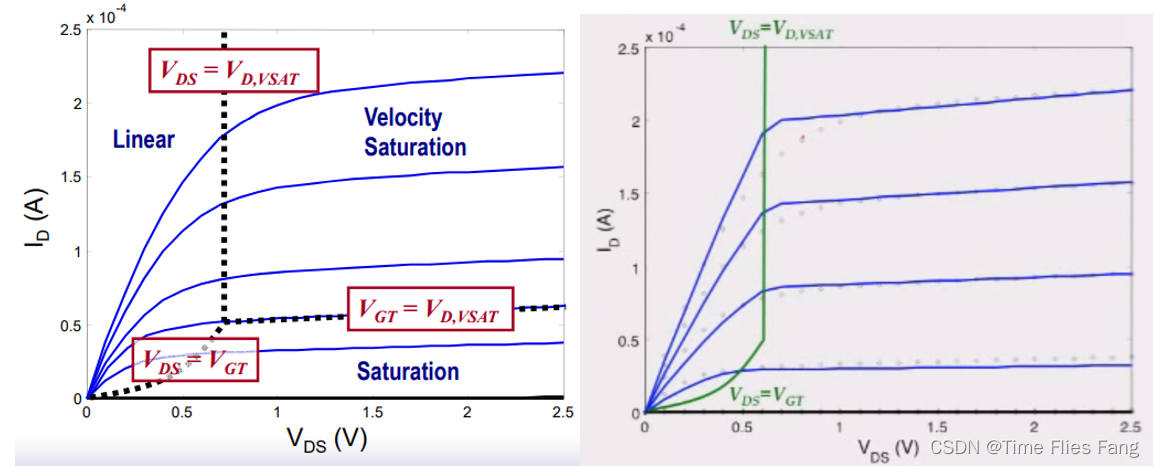

更早进入饱和区

在短沟道模型下,即使VDS还没到达VGS-VT这一阈值,即导电沟道还没完全消失时,由于速度饱和效应阻碍了电流的进一步增大,ID就已经不再随VDS的增长而线性增长了,相当于整个晶体管会在VDS更小的时进入饱和工作区。

Vgs对Id的控制从平方关系转为线性关系

在饱和区段,长沟道模型下Id与Vgs成平方关系,而在短沟道效应下同样因为速度饱和效应,这一关系转为线性关系。上述两个不同可以在下面一张图中直观表现。

需要如此复杂吗?

简化模型的建立

需要记住的是,我们是数字芯片设计者,事实上,我们有时候不一定需要对晶体管所有的物理特性都精确描述,我们只需要尽可能准确地描述会影响数字芯片性能指标的物理特性,而适当放宽对设计相关性部分较少的物理特性的描述,这也是简化模型的建立的基本思路,那么就一个MOS管而言,什么地方是可以被简化的呢?

我们先上结论:对短沟道模型至少可以进行两个简化:

(1)电流Id在速度饱和前线性上升,速度饱和后保持恒值(下图左)

(2)认为速度饱和电压Vdsat与Vgs-Vt无关(下图右)

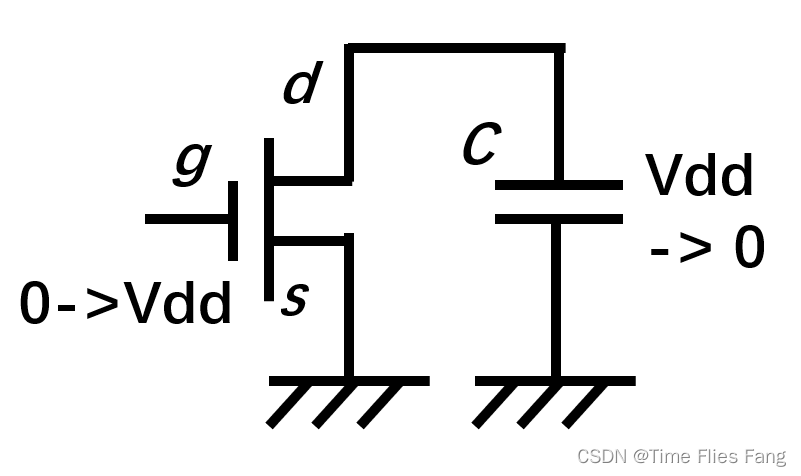

显然,上述两个简化是“不正确”的,但是为什么这仍然是主流的简化方法呢?为了说明这一点,我们看一个非常简单的电路,一个充到Vdd的电容,在一个NMOS管的控制下放电到0,由于Vgs=Vdd是恒定的,而Vds却随着电容的放电在不断减小,如果我们绘制出此时流经电容C的电流Id的话,通过上文的特性曲线我们不难知道,Id也是一个从饱和状态缓慢地下降,直到Vds小到晶体管回到线性区,近似线性的下降。

但是,数字电路中我们关心的延时指标,比如说下降时间,其定义就是电压从原电压降到原电压的一半的时间,对应到晶体管的特性曲线中,这部分的电压下降都在速度饱和区段,而我们的简化误差较大的地方都主要出现在Vds较小时的线性区,而晶体管处于这个状态时,已经不影响数字电路的延时特性了,可以理解成高低电平的切换已经完成了,这一点可以用下图来说明,可以看到在Vds从Vdd降到Vdd/2的阶段,简化模型与SPICE模型的误差其实很小。利用简化的模型可以大大节省EDA工具的优化时间。

小结

本节内容主要从MOS管的结构,工作原理,物理特性,简化建模方法几个维度,对数字集成电路的最基础的构建单元进行了简要的描述,限于篇幅,很多细节没有办法展开描述,想更深入了解这部分内容的小伙伴可以自行查阅EE141的课件与视频,也可以从经典教材《Digital Integrated Circuit: A Design Perspective》中进一步学习。

1479

1479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?