数字集成电路:MOS管器件章(二)

我们知道,RC参数是决定一个门电路的延时特性的主要因素,对于MOS管来讲,在开关模型下,电阻R基本上可以视作一个常量的导通电阻Ron,而对于电容值C,则需要建模分析不同工作区的具体值,本篇主要分析MOS管的电容值。

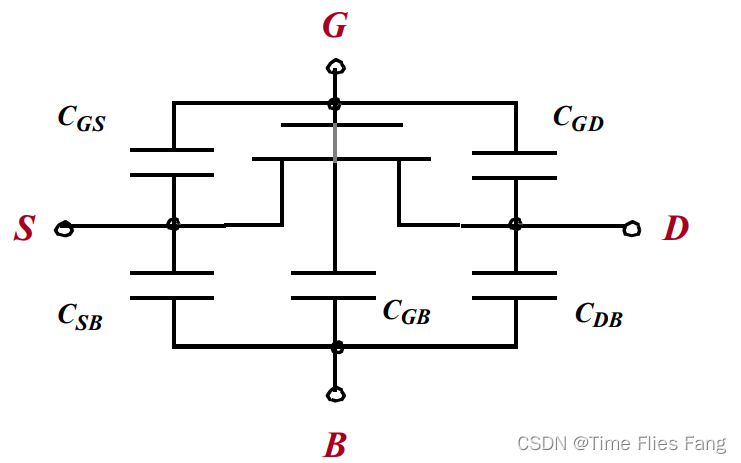

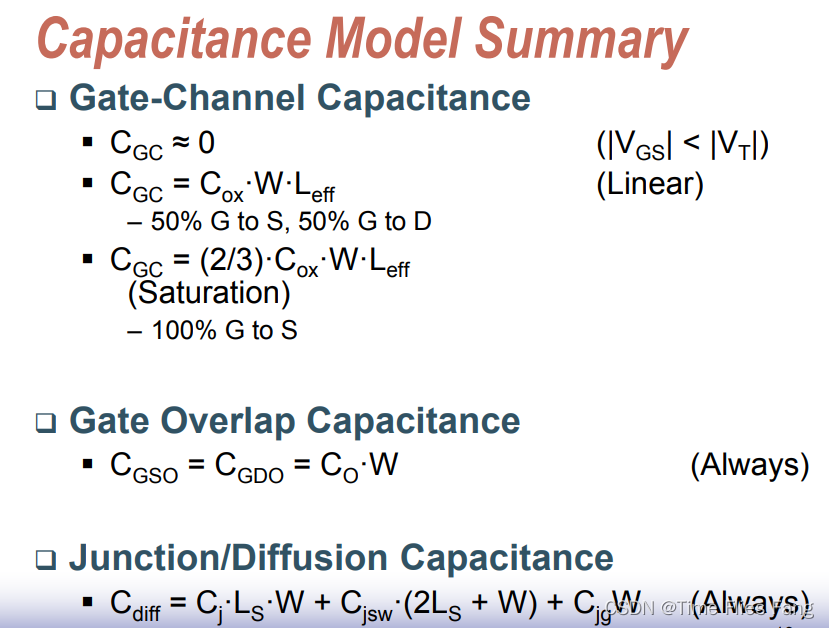

MOS管的电容主要来源于栅极对源漏和衬底的栅电容;也来源于源极和漏极的结电容,如下图所示。

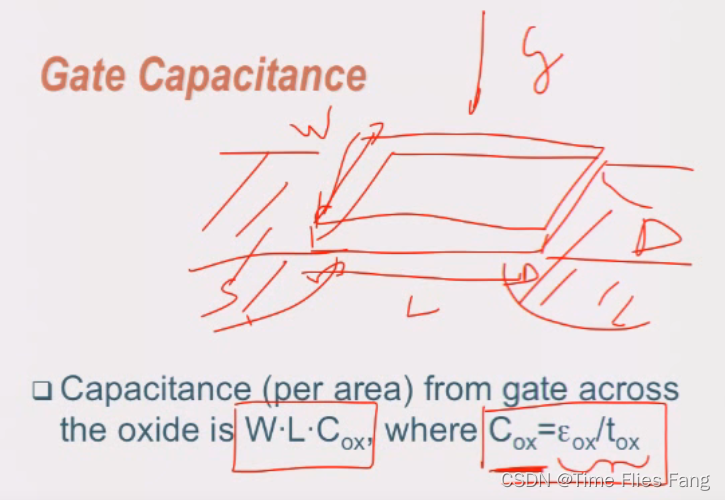

栅电容

单位面积电容与宽长比的影响

栅极单位面积的电容与栅极的厚度成反比,栅极总电容与沟道的宽度和长度成正比,由于在工艺过程中,沟道的长度是固定的最小特征尺寸,因此在定制化设计时,影响栅电容的主要参数为沟道宽度W。

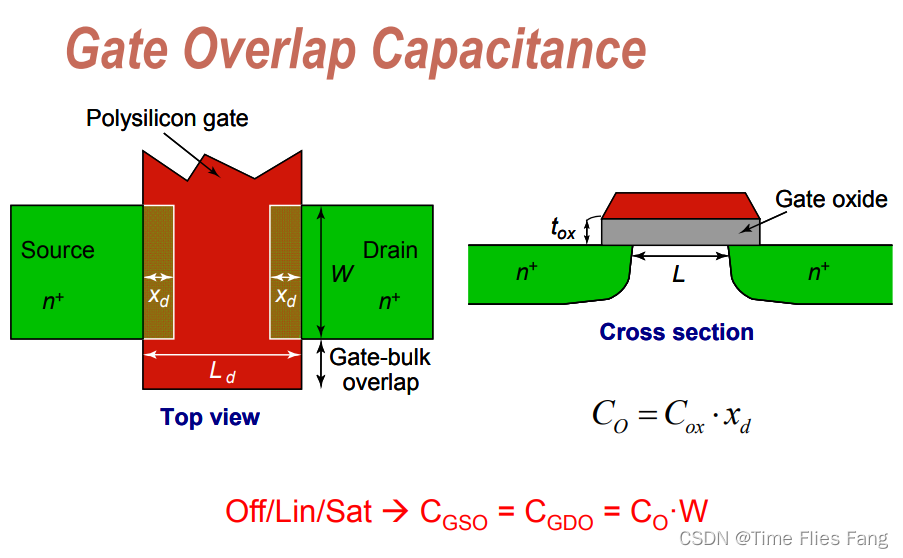

重叠电容

由于退火过程中源极和漏极高掺杂区向低掺杂区(衬底)的扩散,实际上有效的导电沟道要更短,源极,漏极和栅极之间存在重叠,这部分重叠产生的平行板会产生一部分寄生电容。

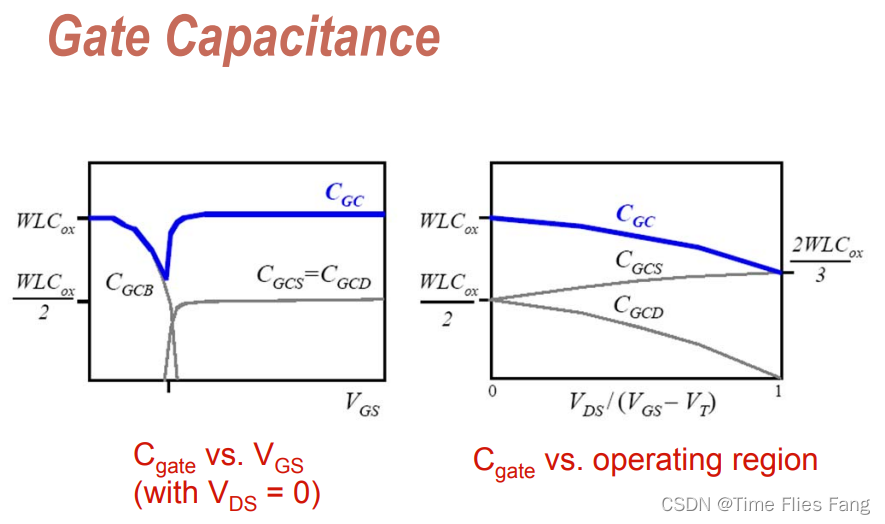

不同工作区的栅电容

截止区时,栅极电容主要来源于栅极的氧化层,并且由于源极和漏极还没形成导电沟道,所以如果忽略overlap的电容外,可以认为栅极对S和D都没有电容,栅极的电容全部对衬底bulk。随着Vgs慢慢增长,且小于VT前,耗尽层会不断变厚,由于电容值与介质厚度成反比,耗尽层电容不断减小,再加上耗尽层所形成的电容跟栅氧电容是串联关系,电容间的串联会使得总电容减小,这使得截止区时栅极电容随着Vgs增加而缓慢减小。

当Vgs增加>VT时,反型层形成,沟通了D和S,并且隔离了栅极和衬底,因此Cgb=0,栅氧电容转而跟S和D平摊,线性区时,D,S是对称的,所以栅极对S和D的电容平均分。

随着VDS增加,D极导电沟道变窄乃至夹断,进入饱和区,Cgd也逐渐减小直到0,而Cgs逐渐增加,最终上升到2/3Cg,总体来讲,在饱和区,栅极电容是在减小的。

上述过程可以由以下图片总结,左图是在Vds=0时增加Vgs,相当于从截止区一直到线性区,且由于Vds=0,源漏极是对称的,各分的一半的栅极电容;右图是Vds逐渐增大,趋于饱和状态,栅极总电容,源漏两级各自的电容的变化,源极电容不断增加直到2/3的总电容,漏极电容不断减少。

小结

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?