一、简介

false path指逻辑上存在,但不需要分析是否满足建立/保持时间的时序路径。使用set_false_path去不对指定路径其进行任何时序约束,进而在时序报告中屏蔽相关错误,但不会停止对其进行延迟计算,因为这条false path上的组合逻辑可能应用于其他的path。这一点区别于set_disable_timing,set_disable_timing完全不对路径做任何时序分析。

二、场景

- 使用了两级同步器的跨时钟域路径;

- 上电后只写一次的寄存器;

- .复位、测试逻辑;

- 分布式RAM的异步写时钟和异步读时钟之间的路径。

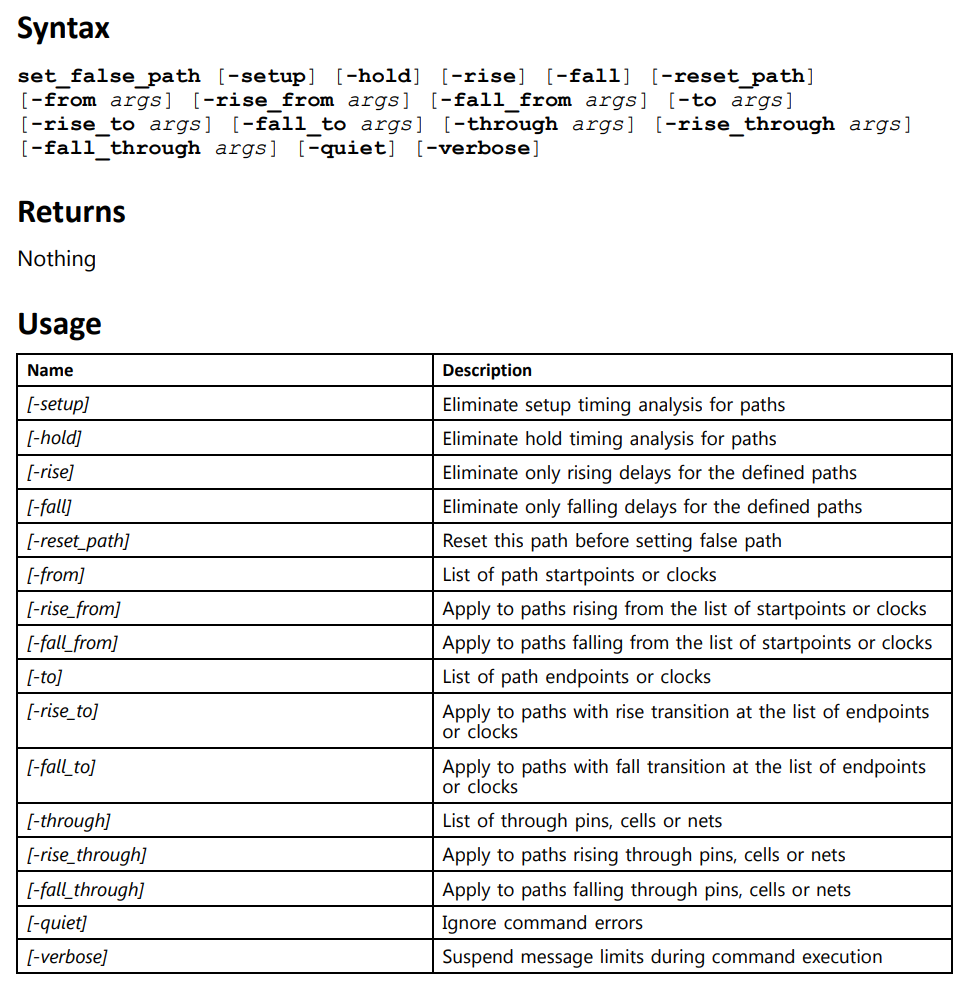

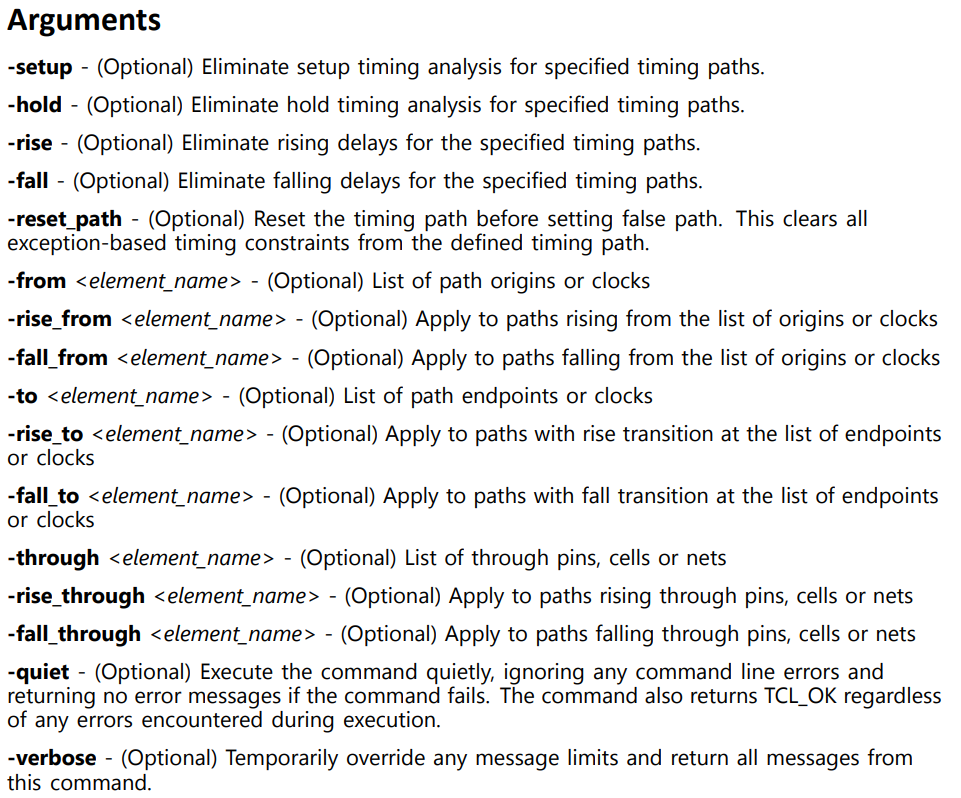

三、语法及用法

3.1 语法

3.2用法

3.2.1 复位

set_false_path -from [get_port reset] -to [all_registers] ,忽略复位端口到所有寄存器的时序路径。

3.2.2 两个时钟域

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB] ,忽略时钟CLKA到时钟CLKB的时序路径。

set_false_path -from [get_clocks CLKB] -to [get_clocks CLKA] ,忽略时钟CLKB到时钟CLKA的时序路径。

3.3.3 经过某路径

set_false_path -through [get_pins MUX1/a0] -through [get_pins MUX2/a1] ,将先经过MUX1/a0引脚后又经过MUX2/a1引脚的时序路径忽略。

四、相关语法

当需要对指定的寄存器的路线做Set False Path的操作有时会比较麻烦,(*ASYNC_REG = "TRUE"*)语法可以用来进行相关约束。

(*ASYNC_REG = "TRUE"*)命令用于声明寄存器能够接收相对于时钟源的异步数据,或者说寄存器是一个同步链路上正在同步的寄存器。这条命令可以放在任何寄存器上,除了设置它的值为TRUE外还可以设置为FALSE.

例子:(*ASYNC_REG = "TRUE"*) reg [0:0] async_rst = 0;

这样可以强制指定async_rst为异步时钟输入,防止综合器对打拍寄存器进行优化,类似DONT_TOUCH。 详情见UG901-Vivado Design Suite User Guide.pdf。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?