一、前言

多比特一般为数据,其在跨时钟域传输的过程中有多种处理方式,比如DMUX,异步FIFO,双口RAM,握手处理。本文介绍通过DMUX的方式传输多比特信号。

二、DMUX同步跨时钟域数据

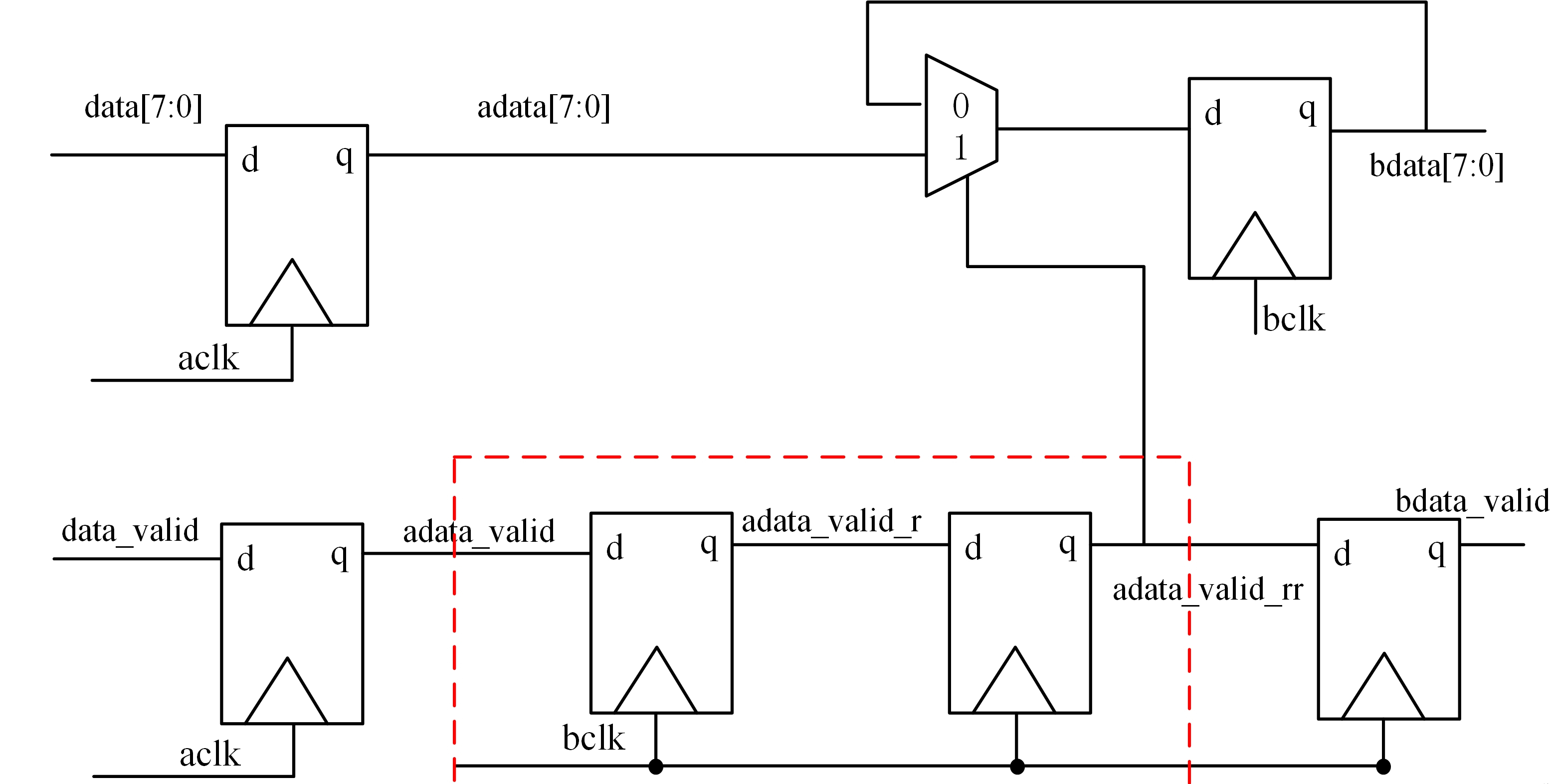

dmux表示数据分配器,该方法适合带数据有效标志信号的多bit数据做跨时钟域传输。其典型结构如下:

慢时钟域到快时钟域

快时钟域到慢时钟域只要将红框中换成单bit快时钟域到慢时钟域处理单元即可。

DMUX遵循的原则就是,数据不同步只对控制信号同步,这点其实和异步fifo里的思路一样,只不多异步fifo中的控制信号是多比特的格雷码,而这个场景下的控制信号是data_valid。继续观察结构可以发现,DMUX是将单bit控制信号同步之后将其最为mux的选择信号。因此使用这个结构需要满足一些要求:

1.数据和使能信号在源时钟域为同步到来的信号;

2.在目的时钟域对数据完成采样前,数据信号不能跳变;

如果不满足以上的要求,那么就可能造成数据漏同步、错同步等问题。

三、DMUX Verilog代码

3.1 慢时钟域数据到快时钟域

module mult_bit_slow_to_fast_dmux

#(parameter DATAWIDTH = 8)

(

input rst_n,

input

本文介绍了在多比特数据跨时钟域传输中,如何使用DMUX进行同步处理,包括DMUX的基本原理、满足的条件以及给出了Verilog代码示例,分别展示了从慢到快和快到慢的数据转换过程。

本文介绍了在多比特数据跨时钟域传输中,如何使用DMUX进行同步处理,包括DMUX的基本原理、满足的条件以及给出了Verilog代码示例,分别展示了从慢到快和快到慢的数据转换过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1718

1718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?