前言

画原理图不画PCB的菜鸟对PCB的一些了解,毕竟也需要指导PCB工程师设计符合要求的PCB嘛。

1、概述

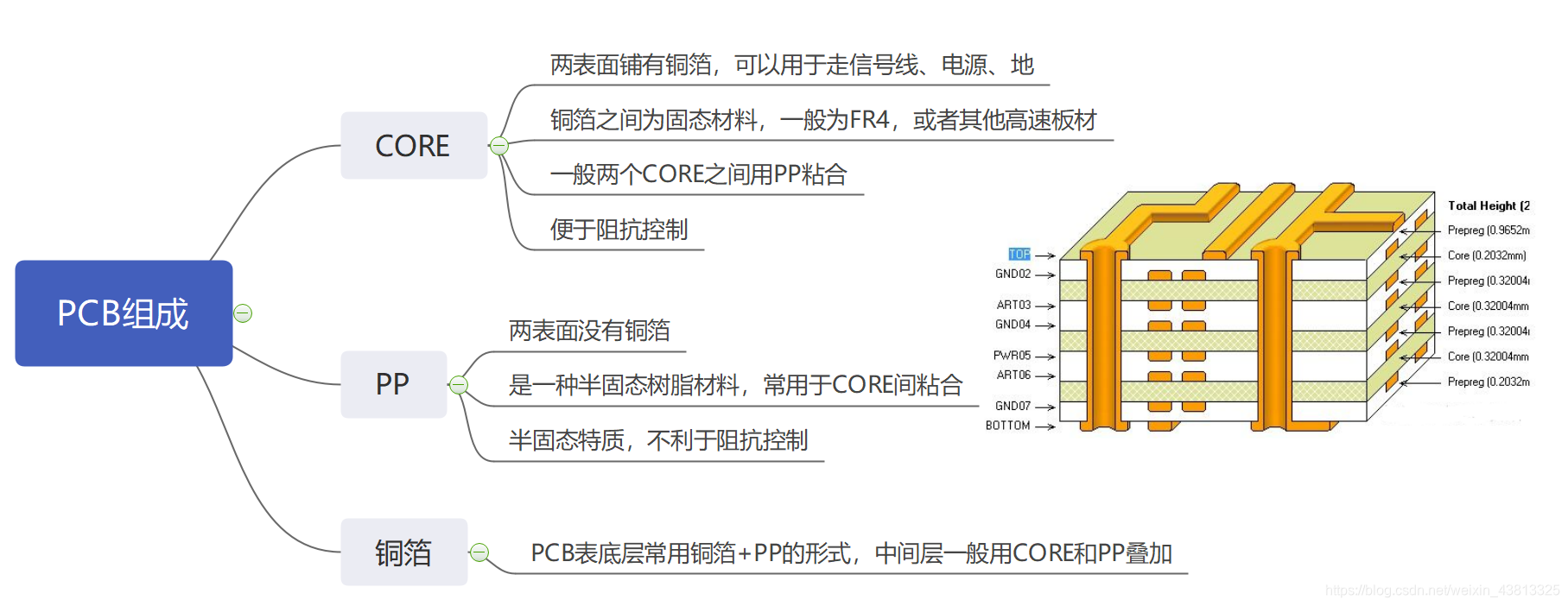

随着高速PCB发展迅速,传统的洞洞板、双面板已经无法满足需求,速率达到5M以上就应该采用4层板以上叠层,以获取更好的信号质量,随着单板功能越复杂,PCB层数越高,那么如何分配叠层和走线位置呢。首先了解下PCB板的组成,如下图所示PCB板常常由铜箔、PP、CORE组成。一般表底层采用铜箔走线,内层采用CORE上的铜箔作为导电层,因为这样的组成结构,PCB层数就一定是偶数啦。

2、叠层的先决条件

1、单板总层数

单板总层数和器件数量,信号线密度、信号速率息息相关,根据这些信息可以估计单板层数,考虑分割电源和信号层隔离度决定单板电源层、信号层、地层数目。

2、单板厚度

单板厚度一般和总层数有关,常见有1.2-2mm不等,一般16层以上单板厚度需要在2mm以上,如果需要插入机箱,还会受到导轨宽度影响,此时可以考虑削边来解除导轨的限制。

3、单端和差分信号阻抗控制

一般单端信号控制在50R,差分信号阻抗控制在100R,特殊的还有PCI总线,DDR总线、USB差分信号线等,需要根据标准控制其阻抗,通过叠层结构、线宽、与参考层之间的间距、介质常数可以控制信号线的阻抗,控制阻抗的意义就不需多言啦,防止信号反射,一般表层由于和空气接触介质常数不稳定

本文介绍了PCB设计的关键步骤,包括叠层设计、布局和布线。首先,讨论了叠层设计的先决条件,如单板层数、厚度和阻抗控制。接着,阐述了叠层设计中电源层、信号层和地层的合理安排,强调了完整参考平面的重要性。然后,讲述了PCB布局时模拟和数字部分的分离以及关键器件的布局策略。最后,详细探讨了布线中的电源、时钟和高速信号线处理,注重降低信号反射和干扰,确保信号完整性。

本文介绍了PCB设计的关键步骤,包括叠层设计、布局和布线。首先,讨论了叠层设计的先决条件,如单板层数、厚度和阻抗控制。接着,阐述了叠层设计中电源层、信号层和地层的合理安排,强调了完整参考平面的重要性。然后,讲述了PCB布局时模拟和数字部分的分离以及关键器件的布局策略。最后,详细探讨了布线中的电源、时钟和高速信号线处理,注重降低信号反射和干扰,确保信号完整性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

941

941

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?