QSpice-(3) Verilog-流水灯

Hi,uu们,之前介绍过,QSpice区别与LTSpice的点在于他支持Verilog以及C++.

今天咱们就用QSpice整个流水灯程序看看.

首先搞个流水灯的小程序,程序代码及注释如下.

| module led( //时钟输入 input CLK, //信号输出 8位 output reg [7:0]Q output ); //初始化Q的输出 initial begin //给Q赋初值 Q<=8'h01; end always @(posedge CLK ) begin //使用拼接运算符,将0位放到第一位 Q<={Q[0],Q[7:1]}; end endmodule |

程序1:流水灯程序

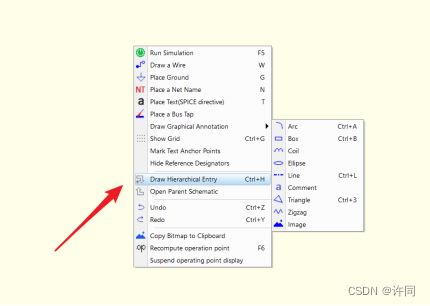

好了,上面程序大概看懂了,咱们就建一个器件呗,第一步先新建层次化入口,如图1所示.

图1:新建层次化入口

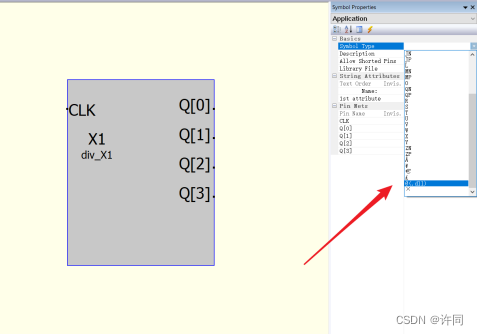

图2:添加端口

图3:修改属性符号类型改为DLL

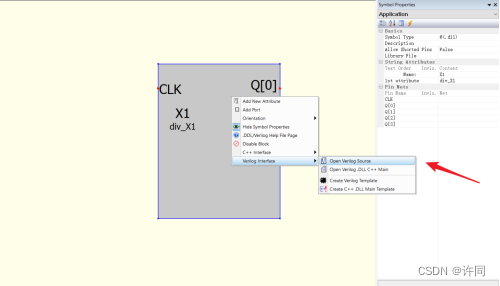

图4:选择open verilog source

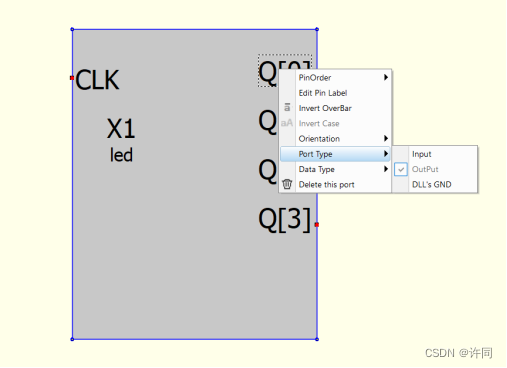

图5:设置端口类型,设置数据类型bool

似乎无法支持Q[7:0],我们改成Q1,Q0这样也不影响,直接开练!

修改代码为以下:

| // Automatically generated .v file on Sun Apr 7 21:19:38 2024 // module led ( clk, q0, q1, q2, q3 ) ; // You will probably want to flush out the nature of these port declarations: input reg clk; output reg q0; output reg q1; output reg q2; output reg q3; // Implement the module here reg [3:0]led; initial begin led<=4'b0001; end always @(posedge clk ) begin led<={led[0],led[3:1]}; q0=led[0]; q1=led[1]; q2=led[2]; q3=led[3]; end endmodule |

将代码拷贝到他生成的文件里面,在编译C++ DLL动态链接库,如下图6所示.

图6:编译Verilog代码

执行完图6步以后,在执行图7如下

图7:生成C++ DLL main template

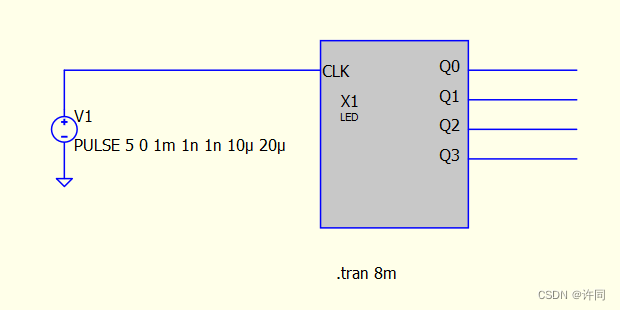

绘制图纸如下:

图8:基本练习图纸如上

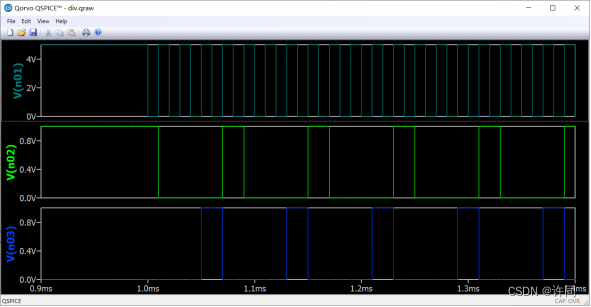

最终仿真波形如下图9所示:

图9:仿真结果

仿真代码:

| 卮X1 玁01碽?玁02碽 N03碽 N04碽 N05碽? LED V1 N01 0 PULSE 5 0 1m 1n 1n 10?20? .tran 8m .end  |

最后,在推荐夏宇闻老师的书,自学Verilog非常好用

推荐我姐家的糕点店

关注公众号不迷路

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?