参考来源:JESD209-5B

在之前的文章中介绍了LPDDR4的相关内容。从这篇文章开始,会对LPDDR5相关内容进行概要分享:

LPDDR5 Initial → LPDDR5 Command Bus and WCK2CK Training → LPDDR5 Read and Training →LPDDR5 Write and Training → LPDDR5 RFM

因为不同平台的设计细节不同,因此不会对详细细节做出分析,只参考JESD规范和SIPI - Signal Integrity and Power Integrity测试规范进行介绍。

Write Command

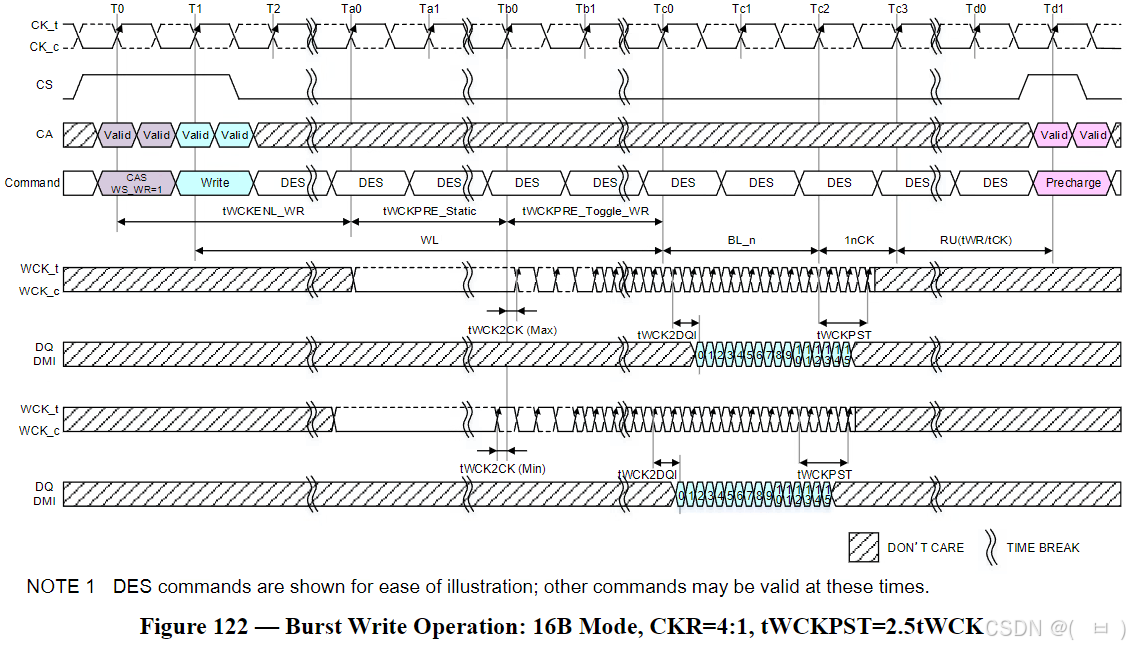

基于JEDEC标准中可以看到Write Timing信息如下:

图中相关参数信息解析如下:

- tWCKENL_WR - Write场景下,从CAS信号发出的第一个CK_t上升沿开始,用于给SOC产生稳定WCK信号的预留时间

- tWCKPRE_Static - WCK_t为Low,WCK_c为High,准备产生WCK Toggle信号

- tWCKPRE_Toggle_WR - Write场景下,WCK差分信号从static切换到toggle出第一个和CK对齐信号的时间段

- WL - Write Latency,从CAS-2命令结束的第一个CLK上升沿T3开始,到对齐第一个有效DQS信号的CLK上升沿Ta3

- tWCK2CK - Write场景下,第一个有效WCK信号上升沿和对应的CLK信号上升沿Tb0之间的skew&#x

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

234

234

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?