描述

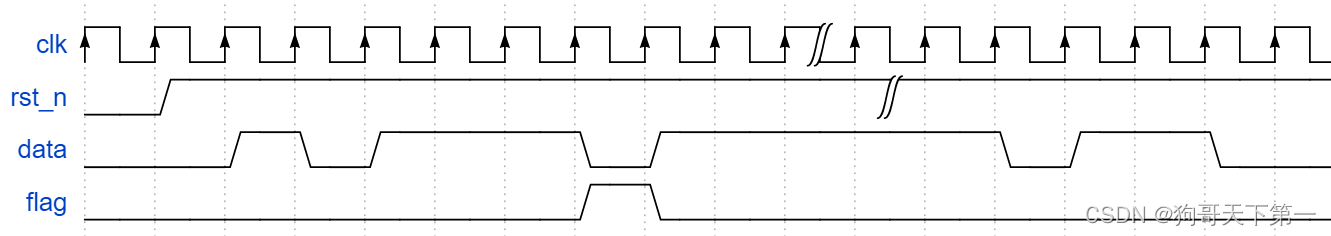

设计一个状态机,用来检测序列 10111,要求:

1、进行非重叠检测 即101110111 只会被检测通过一次

2、寄存器输出且同步输出结果

注意rst为低电平复位

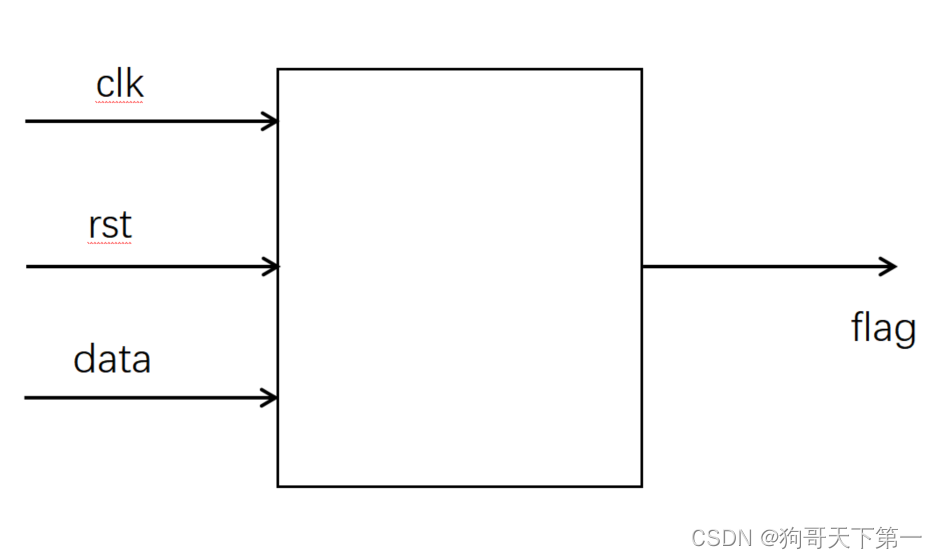

信号示意图:

波形示意图:

输入描述:

输入信号 clk rst data

类型 wire

输出描述:

输出信号 flag

类型 reg

`timescale 1ns/1ns

module sequence_test1(

input wire clk ,

input wire rst ,

input wire data ,

output reg flag

);

parameter IDLE = 0;

parameter S0 = 1;

parameter S1 = 2;

parameter S2 = 3;

parameter S3 = 4;

parameter S4 = 5;

//*************code***********//

reg [3:0] state,next_state;

always@(posedge clk or negedge rst)begin

if(!rst)

state <= IDLE;

else

state <= next_state;

end

always@(*)begin

if(flag) //注意这里

next_state = IDLE;

else

case(state)

IDLE:

if(data)

next_state = S0;

else

next_state = IDLE;

S0://1

if(!data)

next_state = S1;

else

next_state = S0;

S1://10

if(data)

next_state = S2;

else

next_state = IDLE;

S2://101

if(data)

next_state = S3;

else

next_state = S1;

S3://1011

if(data)

next_state = S4;

else

next_state = S1;

S4://10111

if(data)

next_state = S0;

else

next_state = S1;

default:state = IDLE;

endcase

end

//assign flag = (state == S4)?1'b1:1'b0;

always@(*)begin

if(!rst)

flag = 0;

else begin

if(state == S4)

flag = 1;

else

flag = 0;

end

end

//*************code***********//

endmodule

别的都跟重叠序列检测一样,但是拉高flag后要把next_state清零

`timescale 1ns/1ns

module sequence_test1(

input wire clk ,

input wire rst ,

input wire data ,

output reg flag

);

reg [4:0] temp;

always@(posedge clk or negedge rst)begin

if(!rst)

temp <= 'd0;

else begin

if(flag)

temp <= {4'b0,data};

else

temp <= {temp[3:0],data};

end

end

always@(posedge clk or negedge rst)begin

if(!rst)

flag <= 'd0;

else begin

if({temp[3:0],data} == 5'b10111)

flag <= 'd1;

else

flag <= 'd0;

end

end

//*************code***********//

endmodule

218

218

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?