硬件设计-IIS的硬件电路设计

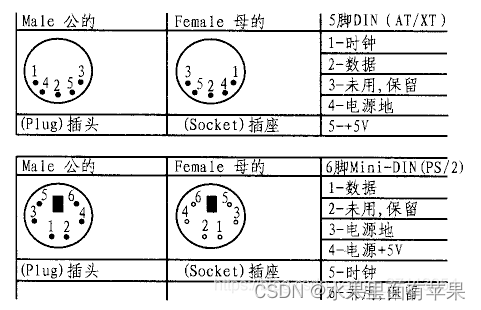

1.接口说明

PS/2接口是输入装置接口,而不是传输接口。所以PS2口没有传输速率的概念,只有扫描速率。在Windows环境下,PS/2鼠标的采样率默认为60次/秒,USB鼠标的采样率为120次/秒。较高的采样率理论上可以提高鼠标的移动精度。PS/2接口设备不支持热插拔,强行带电插拔有可能烧毁主板。

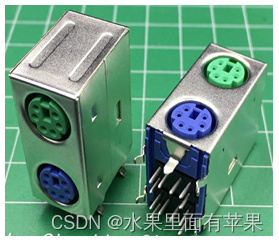

鼠标的PS/2的接口是绿色,而键盘的PS/2接口是紫色。

PS/2两种连接器都只有四个脚有意义。它们分别是Clock(时钟脚)、Data数据脚、+5V(电源脚)和Ground(电源地)。在PS/2键盘与PC机的物理连接上只要保证这四根线一一对应就可以了。PS/2键盘靠PC的PS/2端口提供+5V电源,另外两个脚Clock(时钟脚)和Data数据脚都是集电极开路的,所以必须接大阻值的上拉电阻。它们平时保持高电平,有输出时才被拉到低电平,之后自动上浮到高电平。

键盘的状态每改变一次,键盘至少会发出三个字节的数据包,在有键按下时会向主机发送该键的通码(MakeCode),当键释放时发送断码(BreakCode)。例如:键“A”的通码为0x1C,键“A”的断码为:0xF0,0x1C,因此当要传送键“A”时,键盘发送的数据包的代码是:0x1C,0xF0,0x1C

2.硬件设计要点

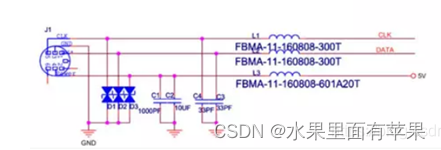

- 数据与时钟电源接口注意ESD防护

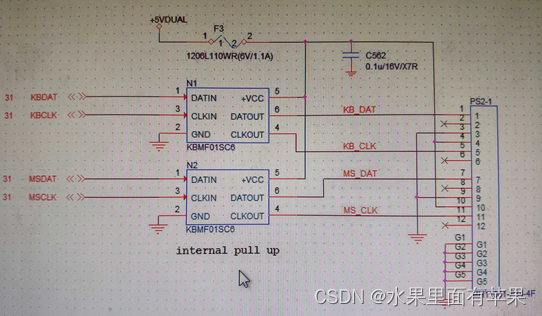

- 数据引脚和时钟引脚主机加上拉电阻

- 5V供电口注意限流保护,最好使用过流保护,电源切换。

- 注意控制端的电平标准,不一致时需要加电平转换芯片

- PS2的金属壳与电路板的GND连接时增加磁珠或者OR电阻隔一下。

563

563

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?