参考:https://blog.csdn.net/zhong_ethan/article/details/104759746

文章目录

0. 功耗源

功耗的本质是能量耗散。由能量守恒定律可知,能量只能从一种形式转成另一种形式,能量的总量不变。芯片耗散的电能主要转化成热能。如果一颗芯片的功耗过大,容易导致工作时温度过高,造成功能失效,甚至晶体管失效。因此,减小芯片功耗是很重要的一个任务。静态功耗以及动态功耗是两个主要的功耗源。

/ Static power(leakage power) : 泄露电流引起的功耗。

| (泄露电流:MOS管中的多种掺杂形成导电区域,同时这些区域会组成多个PN结,从而在通电后形成一系列微小电流。)

|

power <|

| / Switching power : 输入电平翻转,负载电容充放电产生的功耗

| |

\ dynamic power <|

| / 输入电平翻转过程中,pmos、nmos 同时导通产生的功耗

\ Internal power <|

\ cell 内部电容充电的电流产生的功耗

1. 动态功耗(Dynamic power)

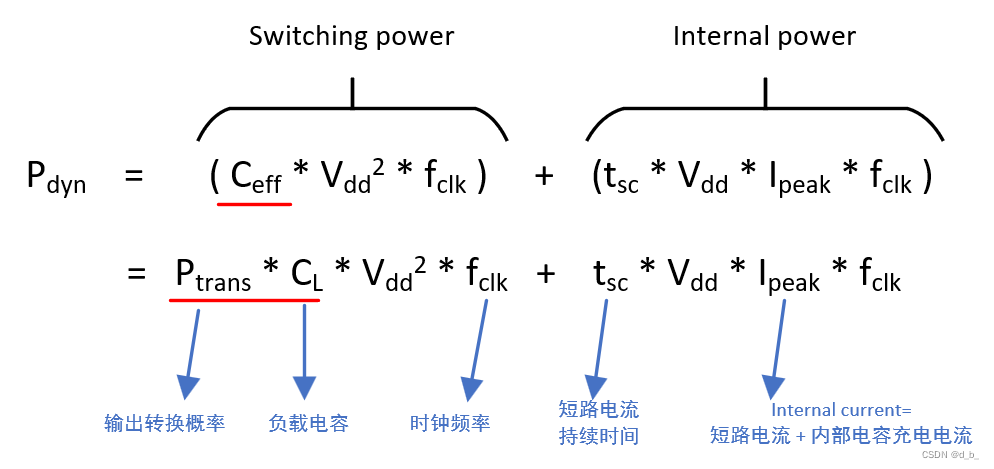

Dynamic power(动态功耗)来源:

(1)Swithcing Power (翻转功耗) : 输入信号翻转时,负载电容充、放电引起的功耗

(2)Internal Power (内部功耗,短路功耗):输入信号翻转时,互补型MOS管(CMOS) 电路的pmos和nmos管同时导通,内部电容充放电产生的功耗

1.1 Swithcing Power (翻转功耗)

翻转功耗可以用如下公式表示:

Pswitch= αCVDD2f

α 称为活动因子,是电路节点从0跳变至1的概率。时钟的活动因子为1,因为它在每个周期都有上升和下降。大多数数据的活动因子为0.5,每周期只跳变一次。

C称为负载电容。

1.1.1 降低翻转功耗方法

(1)使用门控时钟

降低活动因子是降低功耗的非常有效的办法,如果一个电路的时钟完全关断,那么它的活动因子和动态功耗将降为0。Verilog在设计寄存器时采用下面写法可以综合成一个带门控的寄存器。

input reg d;

always @(posedge clk or negedge resetn) begin

if(~resetn)

q<= 1'b0;

else if(enable)

q<= d;

end

(2) 减小毛刺

毛刺会增大活动因子,有可能使门的活动因子增加到1以上。

(3)减小负载电容

电容来自于电路中的连线以及晶体管。缩短连线长度,良好的平面规划和布局可以使连线电容减小。选择较小的逻辑级数以及较小的晶体管可以减小器件的翻转电容。

(4)电压域

动态功耗与电压有平方的关系,降低电源电压可以显著降低功耗。将芯片划分成多个电压域,每个电压域可以根据特定电路的需要进行优化。例如,对于存储器采用高电源电压来保证存储单元的稳定性,对于处理器采用中等大小的电压,对运行速度较低的IO外围电路采用低电压。解决跨电压域信号传输的方法是使用电平转换器。

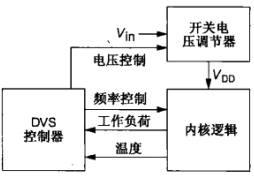

(5)动态电压频率调整(DVFS)

DVS:动态电压调整

DVFS:(Dynamic voltage and frequency scaling)动态电压频率调整

CPU处理不同的任务有不同的性能要求。对于低性能要求的任务,可以使时钟频率降低到足以按预定时间完成任务的最低值,然后使电压降低到该频率下工作所需要的最小值就可以节省大量的能耗。

根据芯片所运行的应用程序对计算机的不同需要,动态调节芯片的运行频率和电压(对统一芯片,频率越高,需要的电压越高),从而达到节能的目的

举例:电脑在运行游戏和办公软件时,功耗不同,就是运用了 DVFS 技术,调节工作频率

(6)降低频率

动态功耗正比于频率,芯片只应当工作在所要求的频率下,不能比所要求的还要快。由前面小结可以,降低频率还可以采用较低的电源电压,大大降低功耗。

(7)谐振电路

谐振电路通过使能量在储能元件如电容或电感之间来回传送而不是将能量泄放到来减小翻转功耗。

1.2 Internal Power (内部功耗,短路功耗)

短路功耗发生在当输入发生翻转时,上拉和下拉网络同时部分导通的时候。如果输入信号翻转速率比较慢,那这两个网络将同时导通较长的一段时间,短路功耗也会比较大,增大负载电容可以减小短路功耗,原因是负载较大时,输出在输入跳变期间只翻转变化很小的一个量。

短路电流一般为负载电流的10%。当输入边沿变化速度很快时,短路功耗一般只占翻转功耗的2%-10%。

2. Static power(静态功耗, leakage power(泄露功耗))

2.1 静态功耗主要来源于:

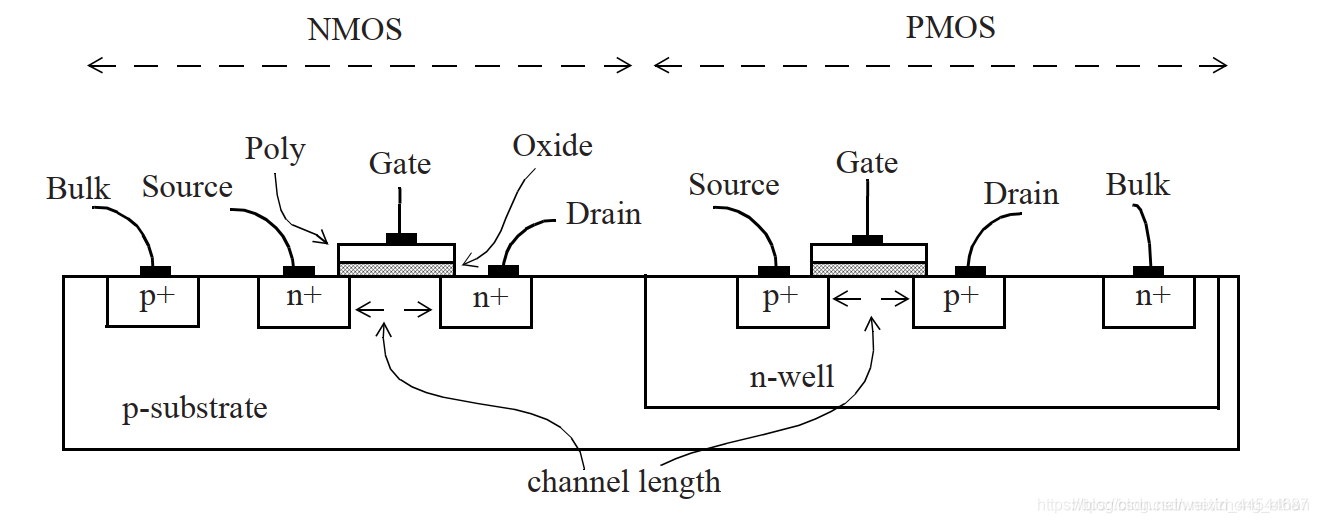

(1) 流过截止晶体管的亚阈值泄漏电流(subthreshold leakage)

亚阈值泄漏电流是晶体管应当截止时流过的电流。在90nm节点之前,泄漏功耗主要在休眠模式下才考虑,这是因为它与动态功耗相比可以忽略不计。但是在低阈值电压和薄栅氧的纳米工艺中,泄漏电流占到总工作功耗的1/3。

亚阈值泄漏电流与多种因素有关。提高源极电压或应用一个负的体电压可以减小泄漏。泄漏电流还与温度有关,限制芯片温度对于控制泄漏至关重要。另外,通过两个或更多个串联晶体管的泄漏电流会应堆叠效应(stack effect)而大大减小。例如两输入与非门,两个NMOS堆叠在一起。

(2) 流过栅介质的泄漏电流(gate leakage)

栅极泄漏电流发生在一个电压加到栅上时(例如当门导通时)载流子遂穿通过薄栅介质的情况下。泄漏电流与介质厚度有极强的关系。工艺中通过选择合适厚度的介质将栅泄漏电流限制到一个可接受的水平上。泄漏电流还取决于栅极电压。通过使晶体管堆叠起来并使截止晶体管靠近电源/地线可以使栅泄漏电流减小。

(3) 源漏扩散区的p-n节泄漏电流(junction leakage)

结泄漏电流发生在源或漏扩散区处在与衬底不同电位的情况下。结泄漏电流与其他泄漏电流相比时通常都很小。

(4) 有比电路中的竞争电流

静态CMOS电路没有任何竞争电流,但其他某些电路甚至在静态时本身就会吸取电流。电流模式逻辑和许多模拟电路也会吸取静态电流。这样的电路应该在休眠模式时通过禁止上拉或电流源工作来关断他们。

2.2 降低静态功耗办法

(1)电源门控

减小静态电流最容易的方法就是关断休眠模块的电源。这一技术称为电源门控。

(2) 多种阈值电压和栅氧厚度

有选择的应用多种阈值电压可以使具有低Vt晶体管保持性能而又使具有高Vt晶体管的其他路径减少泄漏。

大多数纳米工艺的逻辑管采用薄栅氧,IO晶体管采用厚的多的栅氧以使它们能够承受较大的电压。

(3)可变阈值电压

通过体效应可以调制阈值电压。在休眠模式下应用一个反向体偏置减小泄漏。在工作模式下利用一个正向体偏置来提高性能。

(4)输入向量控制

由前面可知,堆叠效应和输入排序会引起亚阈值泄漏和栅泄漏的变化。因此,一个逻辑模块的泄漏与门的输入有关。输入向量控制是当模块置于休眠模式时,应用一组输入图案使模块的泄漏最小。这些输入向量可以通过寄存器上的置位/复位输入端或通过扫描链加入。

3、其他低功耗设计方法

3.1、系统级低功耗

多电源电压

软件功耗管理

时钟树功耗管理

算法级低功耗

3.2、RTL级低功耗

面积换功耗

资源共享

状态编码

操作数隔离

门控时钟

3.3、门级低功耗

多阈值电压

- lvt (low voltage threshold): 速度快,漏电流大

- svt (standard voltage threshold)

- hvt (high voltage threshold):速度慢,漏电流小

电源门控

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?