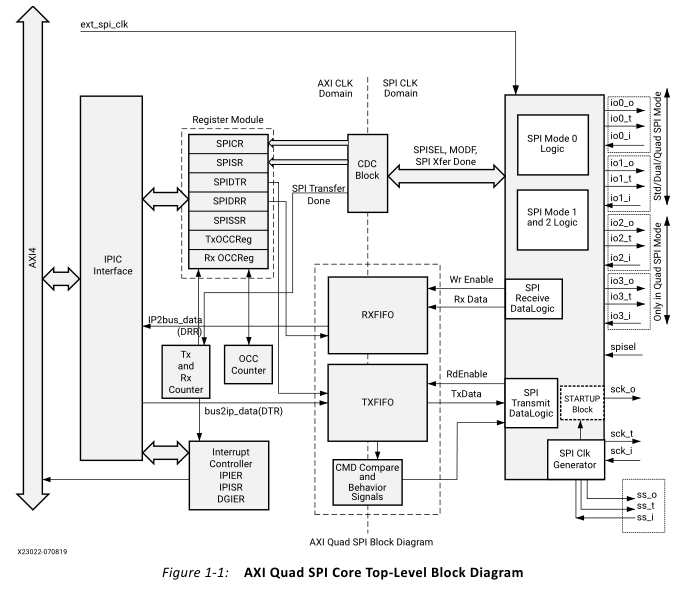

ZYNQ_FPGA_SPI通信协议多种实现方式

填一下前面的坑。

介绍关于Vivado中AXI Quad SPI v3.2的使用方法。

参考资料:pg153-axi-quad-spi.pdf,可自行在官网下载。

以该IP核的Standard SPI Mode的使用为例。

| Address Space Offset | Register Name | Access Type | Default Value (hex) | Description |

|---|---|---|---|---|

| 40h | SRR | Write | N/A | Software reset register |

| 60h | SPICR | R/W | 0x180 | SPI control register |

| 64h | SPISR | Read | 0x0a5 | SPI status register |

| 68h | SPI DTR | Write | 0x0 | SPI data transmit register. A single register or a FIFO |

| 6Ch | SPI DRR | Read | N/A | SPI data receive register. A single register or a FIFO |

| 70h | SPISSR | R/W | No slave is selected 0xFFFF | SPI Slave select register |

| 74h | SPI Transmit FIFO Occupancy Register | Read | 0x0 | Transmit FIFO occupancy register |

| 78h | SPI Receive FIFO Occupancy Register | Read | 0x0 | Receive FIFO occupancy register |

| 1Ch | DGIER | R/W | 0x0 | Device global interrupt enable register |

| 20h | IPISR | R/TOW | 0x0 | IP interrupt status register |

| 28h | IPIER | R/W | 0x0 | IP interrupt enable register |

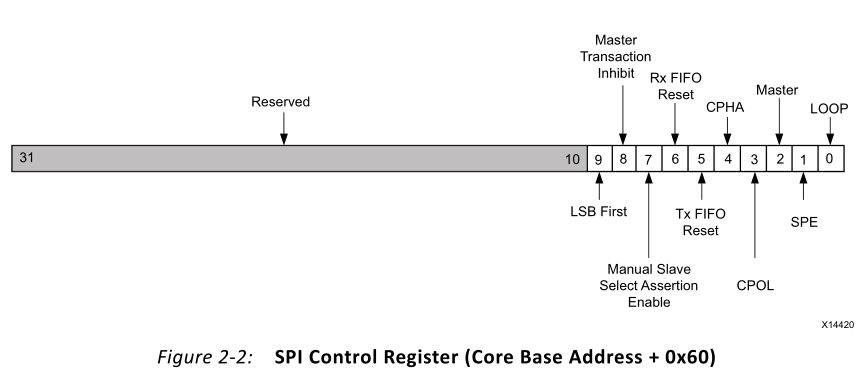

着重介绍使用时所必需的寄存器。

D9:选择数据传输格式LSB first,还是MSB first。默认MSB。

D8:写0时使能主机传输,写1时禁止。

D7:选择从机选择方式。写0时由内核控制,写1时由SPISSR寄存器控制。

D6:写1时复位接收FIFO指针。

D5:写1时复位发送FIFO指针。

D4:CPHA。

D3:CPOL。

D2: 写0时将SPI配置为从机模式,写1时为主机模式。

D1:写0时禁用SPI,写1时启用SPI。

D0:写0时正常,写1时启用loopback模式。

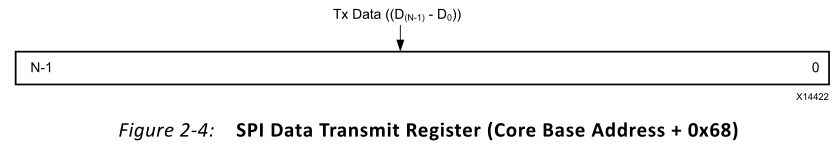

此寄存器的中的N取决于Transfer Width parameter,可设置为8,16,32.

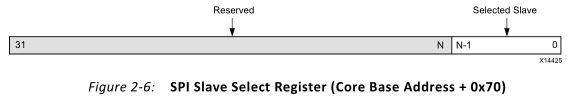

此寄存器中的N为可选择的从机数目,需要使能哪个从机,即在对应位置0。

IP核配置界面如下图。

各参数含义显而易见,值得注意的是Transaction Widith代表一次传输的数据位宽,Frequency Ratio = ext_spi_clk / sck。

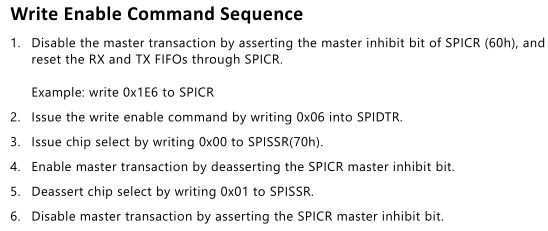

手册中提供一个编程例子:

第1步,将0x1E6写入SPICR(60h)。0x1E6 = 0001 1110 0110。

则目前配置为LSB First,禁止主机传输,使用SPI SSR选择从机, 复位 RX FIFO,复位TX FIFO,CPHA=0,CPOL=0,主机模式,使能SPI,正常模式。

第2步,将0x06写入SPIDTR(68h),0x06即需要传输的8位数据。

第3步,将0x00写入SPISSR(70h),即拉低SS信号。

第4步,将0x0E6写入SPICR(60h),将SPICR的D8置0,使能传输。

第5步,将0x01写入SPISSR(70h),即拉高SS信号。

第6步,将0x1E6写入SPICR(60h),将SPICR的D8置1,禁用传输。

若使用PS端只需要调用AXI总线的读写函数,完成上述步骤即可。

Xil_Out32((BaseAddr) + (u32)(RegOffset), (u32)(Data));

Xil_In32((BaseAddr) + (u32)(RegOffset));

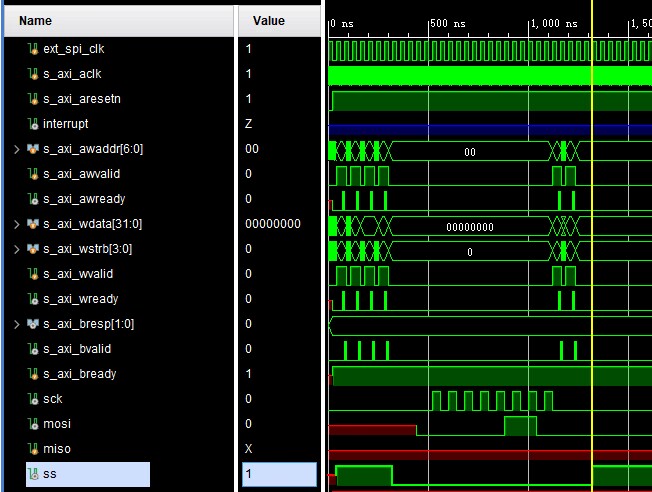

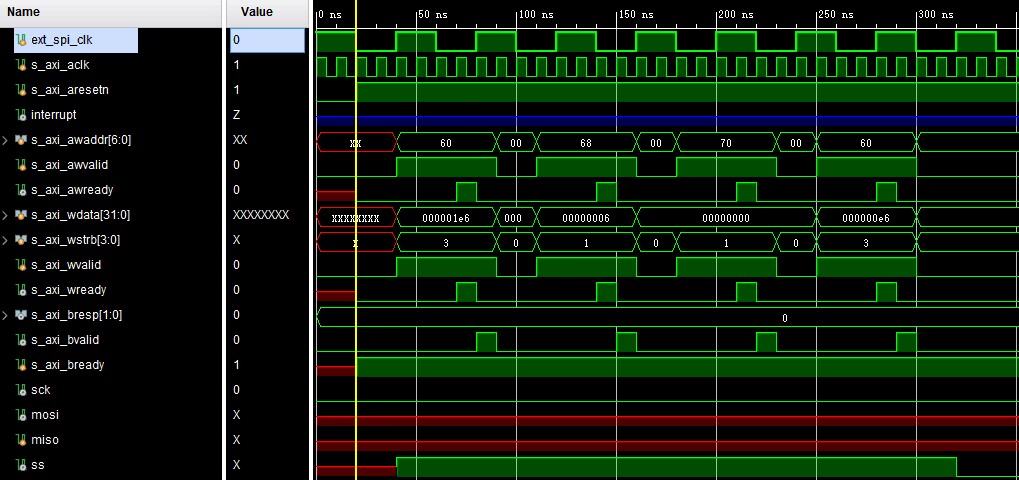

若使用PL端则,参考以下仿真时序。

SPI通信前的具体时序如下图,

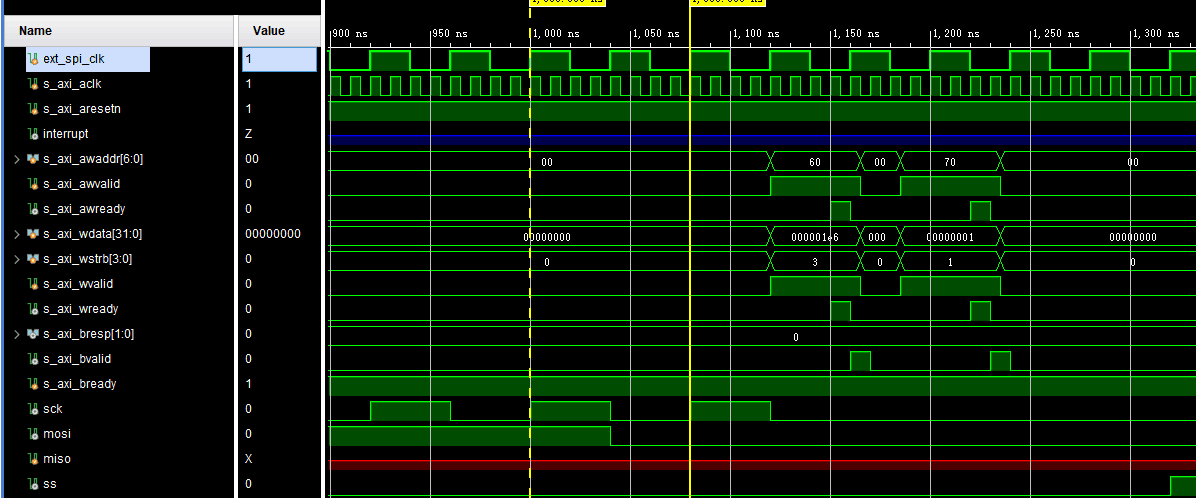

SPI通信后的具体时序如下图,

从上图结果也可以验证Frequency Ratio = ext_spi_clk / sck。

537

537

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?