LogiCORE™IP AXI四串行外设接口(SPI)IP核将AXI4接口连接到那些支持该标准的SPI从设备、双SPI或四SPI协议指令集。

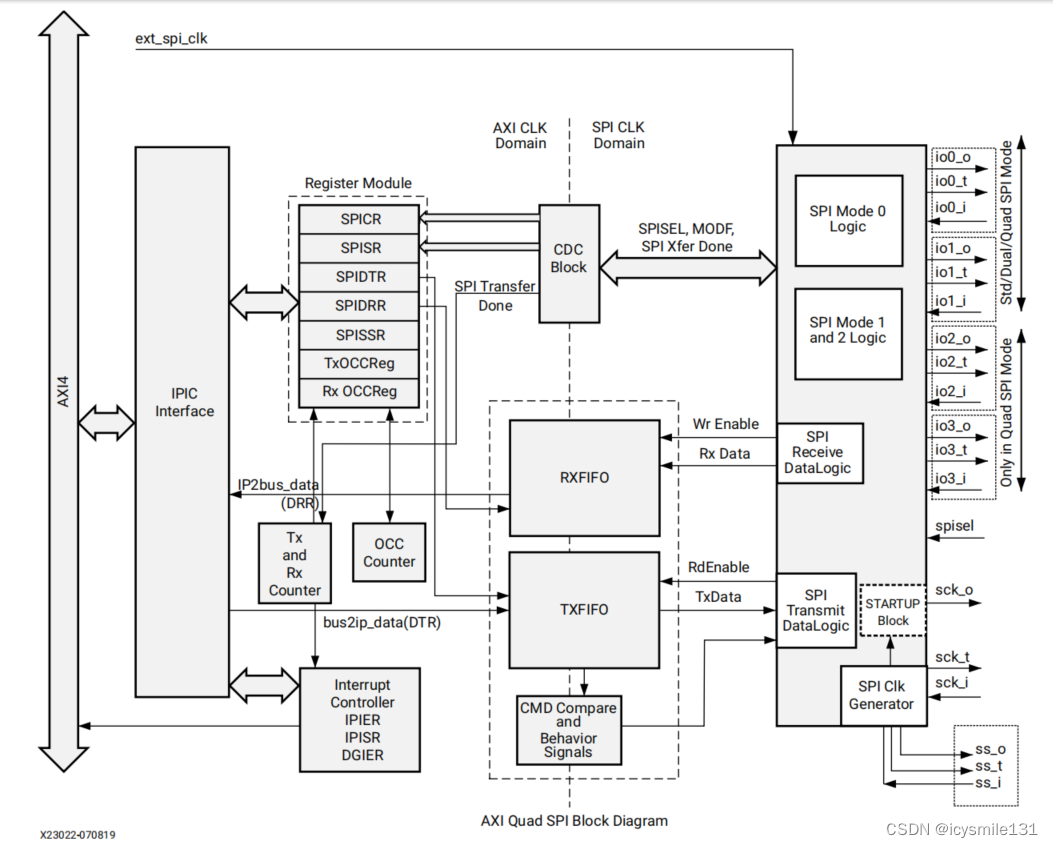

当配置为AXI4-Lite接口时AXI Quad SPI IP核的顶层框图如下图所示。

AXI4-Lite或AXI4接口的选择是基于Vivado IDE中的Enable Performance Mode选项。当选择AXI4-Lite接口时,默认情况下禁用性能模式。当选择AXI4接口时,该IP核始终是一个从IP。

AXI4-Lite或AXI4接口的选择是基于Vivado IDE中的Enable Performance Mode选项。当选择AXI4-Lite接口时,默认情况下禁用性能模式。当选择AXI4接口时,该IP核始终是一个从IP。

SPI的操作模式包括:

1 Legacy Mode(传统模式)

在Vivado IDE中,当Enable Performance mode选项被禁用时,选择传统模式。传统模式使用AXI4-Lite接口。

AXI Quad SPI IP核在配置为不同的SPI模式时,会展现出不同的接口特性和功能。

标准SPI模式(Standard SPI Mode)

在标准SPI模式下,AXI Quad SPI IP核作为一个全双工同步通道,支持主设备(Master)和选定的从设备(Slave)之间的四线接口:

- 接收线(Receive):用于从设备向主设备传输数据。

- 发送线(Transmit):用于主设备向从设备发送数据。

- 时钟线(Clock):由主设备提供,用于同步数据传输。

- 从设备选择线(Slave-Select):允许主设备选择一个或多个从设备与之通信(取决于从设备的配置和是否支持多个从设备同时操作)。

双线SPI模式(Dual SPI Mode)

在双线SPI模式下,AXI Quad SPI IP核除了标准SPI模式的四线接口外,还增加了额外的数据线,以支持更高的数据传输速率。具体来说,它使用两条数据线进行数据的接收和发送:

- 两条接收线:并行地接收数据,增加了带宽。

- 两条发送线:并行地发送数据,同样增加了带宽。

时钟线和从设备选择线的功能与标准SPI模式相同。

四线SPI模式(Quad SPI Mode)

在四线SPI模式下,AXI Quad SPI IP核进一步扩展了数据线,使用四条数据线进行数据的接收和发送:

- 四条接收线:并行地接收数据,进一步增加了带宽。

- 四条发送线:并行地发送数据,同样进一步增加了带宽。

时钟线和从设备选择线的功能也保持不变。

在Dual/Quad SPI模式下,AXI Quad SPI IP核的控制寄存器设置和使用的命令决定了是否使用额外的数据线来传输命令、地址和数据。通过正确配置控制寄存器和选择适当的命令,主设备可以控制是否在特定情况下使用额外的数据线来提高数据传输效率。

SPI IP核支持手动从机选择模式作为从机选择模式的默认操作模式。它允许通过写入从设备选择寄存器来手动控制从设备选择线。这种模式允许在元素之间不切换从设备选择线的情况下,传输任意数量的元素。但是,在开始新的传输之前,必须切换从设备选择线。

自动从设备选择模式是SPI通信协议中与从设备选择相关的一种模式。在这种模式下,每次元素传输完成后(当FIFO被禁用时),从设备选择线(SS线,也称为片选线)会自动切换。这种模式仅在标准SPI模式下可用。

SPI IP核的功能通常被分为几种不同的模式,包括标准SPI模式以及更高速率的数据传输模式,如双SPI模式和四SPI模式。这些模式的主要区别在于它们与从设备内存交互的方式不同。

2 标准SPI模式(Standard SPI Mode)

标准SPI模式是在使用Vivado IDE(Xilinx的集成开发环境)时,通过将Mode选项设置为Standard来选择的。在这种模式下,相关的参数包括:

- • Mode:SPI的工作模式,即标准SPI模式。

- • Enable STARTUPEn Primitive:一个启动原语(primitive)的使能选项。在Xilinx FPGA设计中,STARTUP原语用于在FPGA上电或复位后执行一些初始化操作。对于7系列设备,通常使用STARTUPE2原语;而对于Ultrascale™系列设备,则使用STARTUPE3原语。

- • Transaction Width:这指的是SPI事务的数据宽度。在标准SPI模式下,这通常指的是每次传输的数据位数,可以是1位、2位、4位、8位等,具体取决于SPI接口和从设备的配置。

- • No. of Slaves:定义了SPI接口可以连接的最大从设备数量。

- • Frequency Ratio:用于设置SPI时钟与主时钟之间的比率,以控制SPI通信的速率。

- • Enable FIFO:控制参数,用于决定是否在SPI接口中启用FIFO。FIFO的引入可以平滑不同时钟域之间的数据传输,并允许在不连续的数据传输中存储数据。

- 在标准SPI模式下,IP核的特性(包括是否包含FIFO)可以描述如下:

- • 是否包含FIFO取决于Enable FIFO参数的设置。当Enable FIFO参数被设置为启用时,FIFO将被包含在SPI IP核中;否则,SPI IP核将不包含FIFO。FIFO Depth参数与Enable FIFO参数相关联。当FIFO被启用时,FIFO Depth参数将限制发送和接收FIFO的深度。在标准SPI模式下,当FIFO被启用时,FIFO深度的有效值可以是16或256。如果FIFO没有被启用,那么FIFO深度参数的值将被视为0,因为此时没有FIFO来存储数据。在选择FIFO深度时,通常建议选择与闪存页面大小最匹配的深度。一个256深度的FIFO通常是一个很好的选择,因为它可以适应大多数闪存设备的页面大小,从而提高数据传输的效率。

- • 在标准SPI模式下,当通过Enable FIFO参数启用FIFO时,FIFO深度的有效值通常是16或256。这意味着你可以配置FIFO以存储最多16个或256个数据项。

当Enable FIFO参数设置为0时,IP核中不包含FIFO。在这种情况下,数据传输通过单个的发送和接收寄存器进行。这意味着每次数据传输都需要直接操作这些寄存器,而没有额外的缓冲区来缓存数据。

当Enable FIFO参数被设置为启用,并且FIFO Depth被配置为16或256时,设计中将包含发送或接收FIFO,其深度为16个或256个元素。FIFO的宽度(即每次可以传输的数据位数)是通过Transaction Width选项来配置的。

AXI Quad SPI IP核支持连续传输模式,当AXI Quad SPI IP核配置为主设备时,数据传输会持续进行,直到发送寄存器/FIFO中有数据可供传输。AXI Quad SPI支持手动和自动从设备选择模式。以页面读取命令为例,命令、地址以及数据发送寄存器(DTR)中的数据节拍数必须设置为与SPI存储器意图读取的数据字节数相同。

当AXI Quad SPI IP核被配置为从设备时,如果在数据传输元素过程中从设备选择线(SPISEL)变为高电平(非活动状态),当前的传输将被中止。如果之后从设备选择线变为低电平,被中止的数据元素将重新传输。请注意,IP核的从设备模式仅在标准SPI模式下可用。

3 Dual/Quad SPI Mode

在Vivado IDE中,当Mode选项被设置为Dual时,AXI Quad SPI IP核将进入Dual SPI模式。当Mode选项被设置为Quad时,AXI Quad SPI IP核将进入Quad SPI模式。相关的参数包括:

- • Mode:当设置为Dual时,AXI Quad SPI将工作在Dual SPI模式下,允许同时从两个SPI通道进行数据传输。

- • Slave Device:用于配置从设备。

- • Enable STARTUPEn Primitive:这是一个启动原语(primitive)的使能选项。

- • Transaction Width:定义了每次SPI传输的数据宽度。在Dual SPI模式下,这个设置将应用于两个SPI通道。

- • No. of Slaves:指定了连接到AXI Quad SPI IP核的从设备数量。在Dual SPI模式下,这个值通常会被设置为2,因为有两个SPI通道可以分别连接到一个从设备。

- 在AXI Quad SPI IP核中,FIFO的深度和宽度是关键的配置参数,它们决定了FIFO能够缓存的数据量以及数据的宽度。以下是与FIFO相关的属性和Dual SPI模式下端口的行为说明:

- • FIFO Depth:基于FIFO Depth选项进行设置,有效的值可以是16或256。

- • FIFO Width:通常情况下,FIFO的宽度配置为8位,因为SPI从设备存储器的页面大小通常是8位。

在不同模式下,端口的行为会有所不同,具体取决于所使用的SPI指令和存储器类型。

标准SPI模式指令:对于标准SPI模式的指令,IO0和IO1引脚是单向的,并且其行为与标准SPI模式相同。这些引脚通常用作MOSI(主设备输出从设备输入)和MISO(主设备输入从设备输出)。

Dual SPI模式指令:在Dual SPI模式下,IO0和IO1引脚可以是单向或双向的,具体取决于通过控制寄存器位设置的指令类型和选择的存储器。IO2和IO3引脚处于三态(高阻态),通常不用于数据传输。

Quad SPI模式指令:在Quad SPI模式下,IO0、IO1、IO2和IO3引脚可以是单向或双向的,具体取决于在传输命令、地址和数据时所使用的存储器类型。这四个引脚同时参与数据传输,从而提高了带宽。

当Mode选项被设置为Dual或Quad时,AXI Quad SPI IP核将分别被强制运行在Dual或Quad SPI模式下。然而,IP核仍然支持标准SPI命令和接口,这意味着你可以使用标准的SPI命令与从设备通信,尽管IP核内部可能以更高的数据传输速率运行。

内部命令逻辑会根据加载到DTR FIFO(SPI DTR)中的命令来指导IP核I/O的行为。Mode选项的设置还会影响I/O引脚的可用性。在Quad SPI模式下,所有四个IO引脚(IO0、IO1、IO2和IO3)都将被用于数据传输。而在Dual或标准SPI模式下,只有部分引脚会被使用。

4 Common Information for Both SPI Modes

AXI Quad SPI IP核允许添加额外的从设备,并自动为主机生成所需的解码逻辑,以用于单独的从设备选择输出。同样,也可以添加额外的主机。然而,这个接口标准并没有实现检测所有可能冲突的功能。为了消除冲突,系统软件需要仲裁总线控制。

该IP核可以与片外和片上的主机和从设备进行通信。从设备的数量受限于从设备选择寄存器的大小,通常最多支持32个从设备。然而,从设备和主机的数量会影响在频率和资源利用率方面可达到的性能。

所有的SPI IP核和中断寄存器都是32位宽,仅支持对所有SPI和中断寄存器模块的32位访问。这意味着在编程和配置AXI Quad SPI IP核时,需要确保使用32位的数据类型来访问这些寄存器。

591

591

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?