AXI Quad SPI IP核(Quad Serial Peripheral Interface)是一个提供串行接口连接SPI从设备的解决方案,它支持Standard(单线路)、Dual(双线路)、Quad(四线路)模式,其中线路数越多,传输速度越快。

要自定义AXI Quad SPI IP核以供您的设计使用,您可以按照以下步骤为与该IP核相关的各种参数指定值:

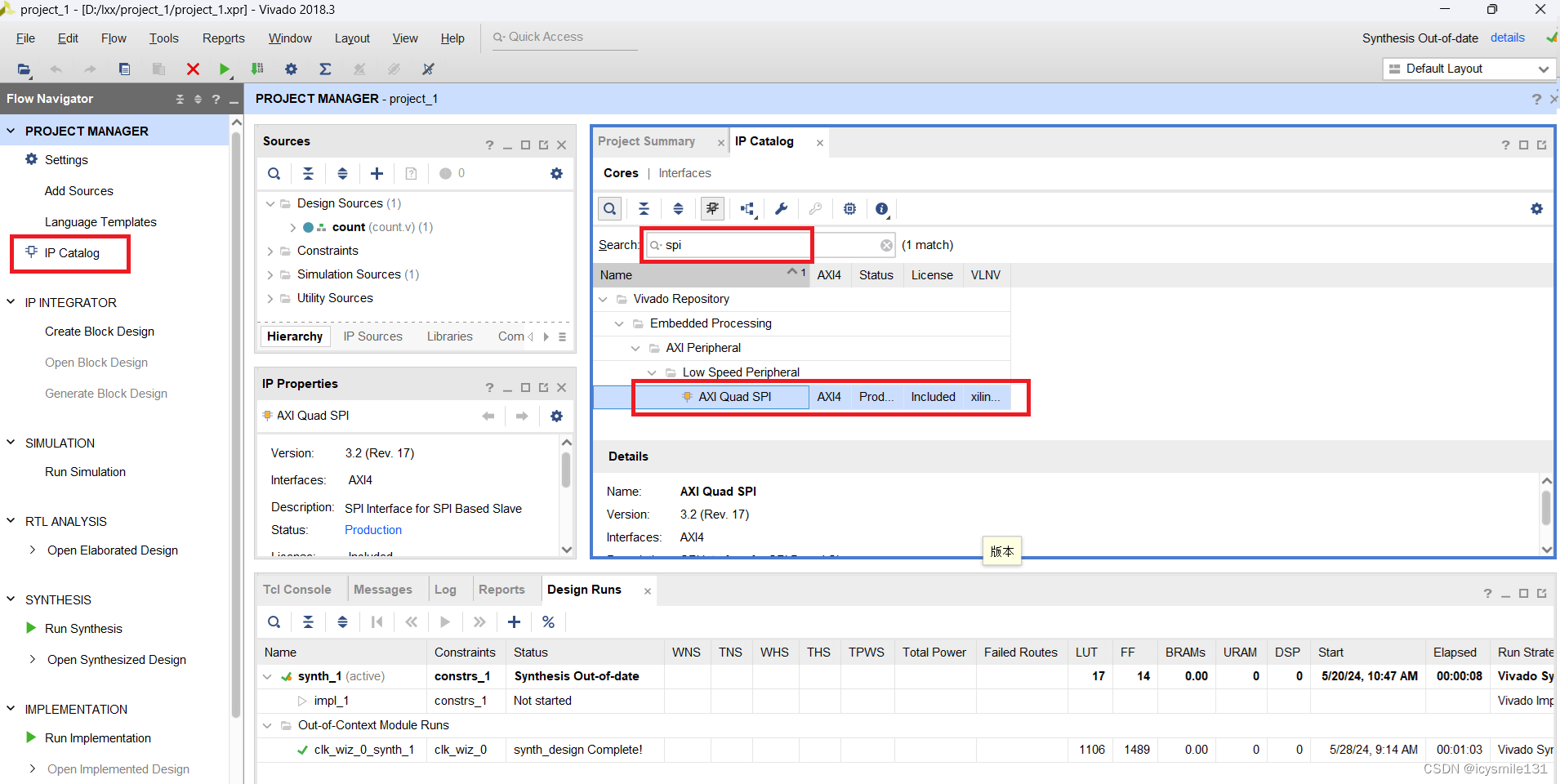

1 从Vivado IP目录中选择IP

打开Vivado软件,并加载您的项目。在左侧的IP浏览器中,找到并定位到AXI Quad SPI IP核。从IP目录中选择AXI Quad SPI IP核。

2 自定义IP

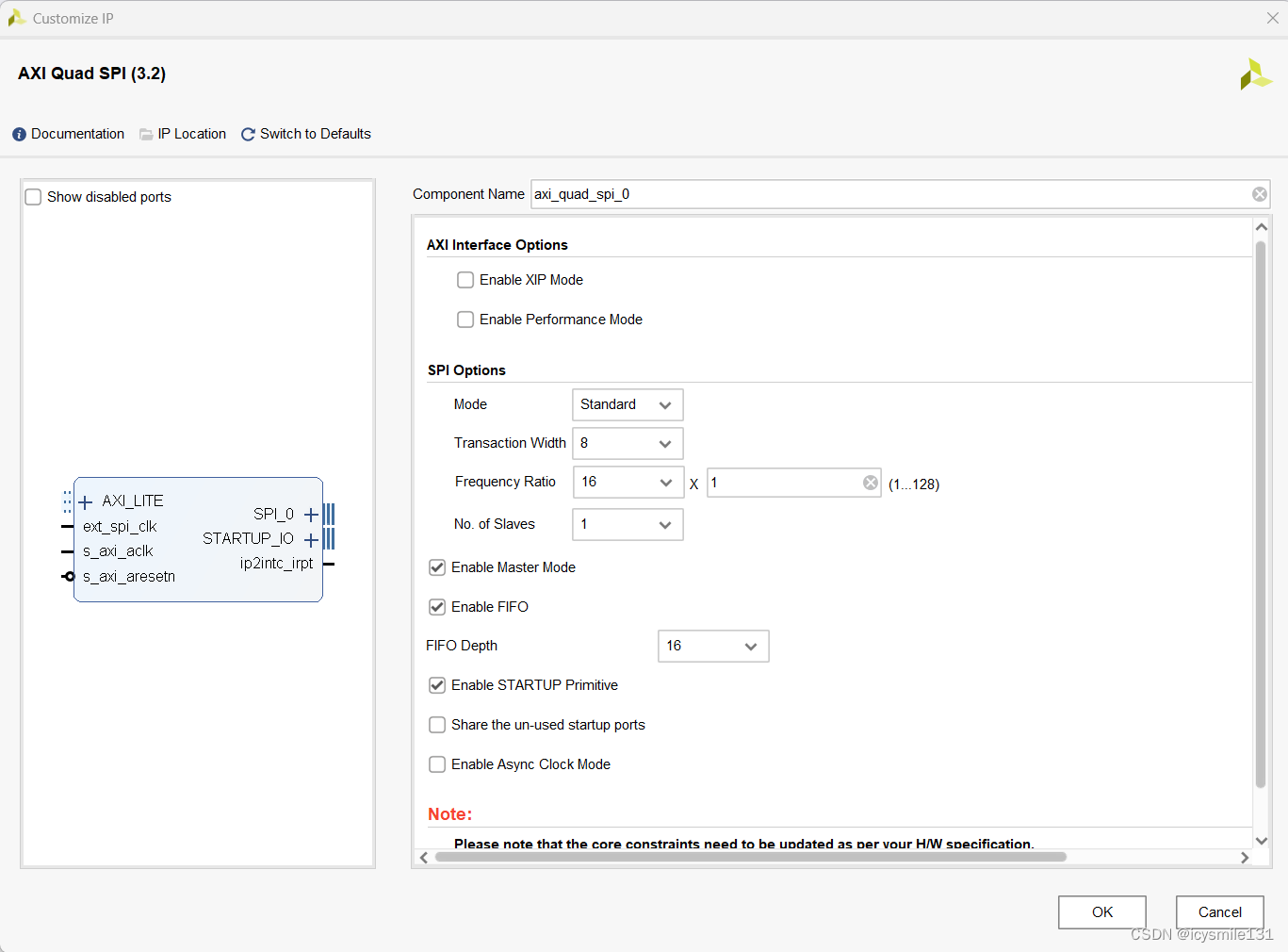

选中AXI Quad SPI IP核后,可以通过以下方式之一来打开其自定义界面:

- 直接双击选中的IP核。

- 在工具栏中找到并点击“Customize IP”命令。

- 右键点击选中的IP核,从弹出的菜单中选择“Customize IP”命令。

3 配置参数

在打开的自定义界面中,将看到与AXI Quad SPI IP核相关的多个参数和选项。

(1)AXI Interface Options

- Enable XIP Mode:在AXI Quad SPI IP核的配置中,启用XIP 模式将同时启用AXI4和AXI4-Lite接口。选择24位或32位寻址模式应该基于下游SPI设备的要求。

XIP (eXecute In Place) 模式:

XIP模式允许在AXI Quad SPI存储器中的程序直接运行,而无需将其复制到其他存储器中。这通常用于存储FPGA的启动代码或配置数据,以便在FPGA上电时直接执行。在XIP模式下,AXI Quad SPI IP核的AXI4接口仅用于读取操作,不支持写入操作,因为该存储器被视为只读存储器。

寻址模式选择:

AXI Quad SPI IP核支持24位和32位寻址模式。选择哪种寻址模式取决于连接到SPI从设备的存储器大小以及您如何配置该存储器。

- 24位寻址模式:适用于最大4GB(2^24字节)的存储器空间。如果您的SPI从设备使用小于或等于4GB的存储器,并且您不需要32位寻址的全部功能,则可以选择24位寻址模式。

- 32位寻址模式:适用于最大4TB(2^32字节)的存储器空间。如果您的SPI从设备使用大于4GB的存储器,或者您需要更大的寻址空间,则应该选择32位寻址模式。

请注意,在选择寻址模式时,还需要确保AXI Quad SPI IP核的AXI4和AXI4-Lite接口配置正确,以匹配您选择的寻址模式。例如,在32位寻址模式下,AXI4接口可能需要配置为支持32位数据宽度和地址宽度。

- Enable Performance Mode:当“Enable Performance Mode”被选中时,AXI4接口被启用,从而允许使用突发传输(Burst Capability)和其他高级功能。如果不选择此选项,系统将使用AXI4-Lite接口,这可能会限制数据传输的性能。

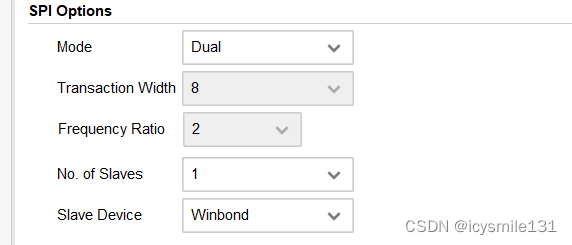

(2)SPI Options

-

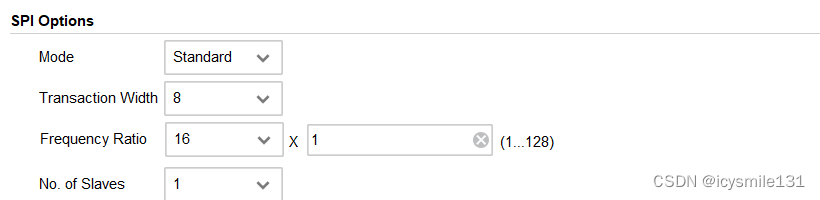

Mode:选择标准、双线路模式或四线路模式。正确的模式应根据目标SPI从设备和应用程序来选择。

- 标准模式(Standard SPI):最基本的SPI通信模式,使用单条数据线进行数据传输。

- 双线路模式(Dual SPI):使用两条数据线同时进行数据传输,提高了数据传输速率。

- 四线路模式(Quad SPI):使用四条数据线同时进行数据传输,进一步提高了数据传输速率。

-

Transaction Width:选择8位、16位或32位事务。每个SPI事务都会包含所选位数的数据。在双线路模式和四线路模式下,事务宽度限制为8位。在XIP模式下,无论哪种模式,事务宽度都限制为8位。

-

Frequency Ratio:选择一个2的幂次方作为除数,范围从2到2048。由此产生的SPI时钟频率是与

ext_spi_clk信号相关联的频率除以所选值的商。在双线路模式或四线路模式的传统和增强模式下,除数限制为2。在XIP模式下,无论哪种模式,频率比都限制为2。

-

No. of Slaves:在非XIP模式下,选择从设备数量,范围从1到32。在XIP模式下,SPI从设备数量限制为1。

-

Slave Device:在双线路模式或四线路模式下,选择从设备的类别,包括:

- Mixed:选择Winbond、Micron和Spansion存储器规范中共同的命令子集。

- Winbond:选择Winbond特定的存储器命令集。

- Micron:选择Micron特定的存储器命令集。

- Spansion:选择Spansion特定的存储器命令集。

在非标准的XIP SPI模式下,从设备参数将被忽略。如果在Vivado IDE中选择了双模式或四模式作为SPI模式,则从设备选项将可见。

(3)Remaining Options

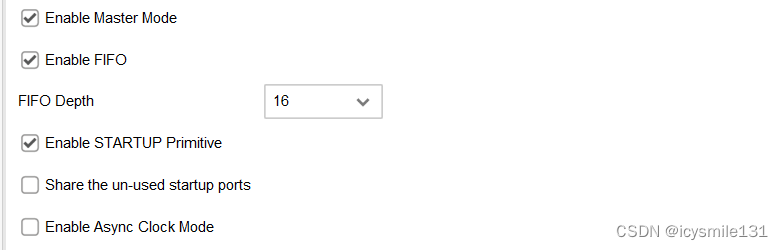

• Enable Master Mode:当选中此选项时,启用主SPI模式;未选中时,则启用从SPI模式。这个参数仅适用于标准SPI模式。在双线路模式或四线路模式下,仅支持主SPI模式。

主SPI模式:允许SPI设备主动发起数据传输。

从SPI模式:SPI设备等待外部主设备发起数据传输。

• Enable FIFO:当选中此选项时,设计中将包含发送或接收FIFO;未选中时,则省略FIFO。这个“启用FIFO”参数仅适用于标准SPI模式。在双线路模式或四线路模式下,FIFO总是包含在设计中。

• FIFO Depth:选择包含的FIFO的深度,可选值为0、16或256个节拍。在标准SPI模式下,此参数仅在包含FIFO时可用。在双模式或四模式下,FIFO深度限制为16或256。FIFO宽度固定为8位。

FIFO深度:指的是FIFO可以存储的数据量。更深的FIFO可以存储更多的数据,有助于在高 数据速率下减少数据溢出或下溢的可能性。

FIFO宽度:指的是每个存储单元可以存储的数据位数。在这里,每个存储单元可以存储8位 数据。

- Enable STARTUPEn Primitive:选中此选项时,设计中将包含STARTUP原语;未选中时,则省略该原语。7系列FPGA中提供STARTUPE2原语,而UltraScale™器件中提供STARTUPE3原语。此原语对于与外部SPI从设备共享SPI时钟非常有用。在设备的从模式下,此原语始终被禁用。

- Enable Async Clock Mode:仅当AXI Quad SPI IP核处于独立模式,且AXI接口和外部SPI时钟在相位/极性和频率方面不同时,才启用此选项。此选项在IP集成器中被禁用。此参数根据连接到内核的时钟自动传播。如果AXI时钟和ext_spi_clk彼此同步,则此参数设置为0;如果它们是异步的,则设置为1。

IP核处于“独立模式”(standalone mode)时,这通常意味着该IP核不依赖于其他IP核或处 理器来运行,而是可以独立地处理数据和执行其功能。在独立模式下,IP核通常具有其自己 的时钟、复位逻辑和中断处理机制。

异步时钟模式:允许AXI接口和外部SPI时钟以不同的频率和相位运行,这对于跨不同时钟 域的通信至关重要。

- Share the un-used startup ports:启动端口(startup ports)通常用于设备的初始化和配置。然而,在某些情况下,可能有些启动端口并未被使用。这时,可以考虑共享这些未使用的启动端口,以提高资源的利用率和设计的灵活性。

995

995

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?