一、为什么要跨时域?

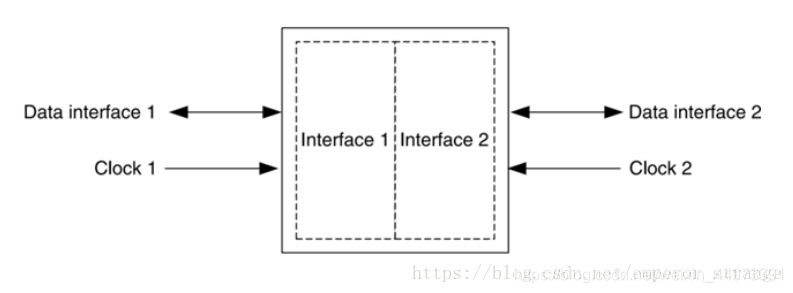

如果一个设计中只用了一个clock,那就只有一个时钟域。如果在一个设计中有多个时钟去控制不同的接口,那就是有多个时钟域,我们在实际中都会遇到跨时钟域的问题。

当时钟不匹配时,就需要进行同步化,否则可能出现亚稳态,从而造成整个设计的不稳定。

二、相关概念解释

1.脉冲信号:跟随时钟,信号发生转变

2.电平信号:不跟随信号,信号发生转变

3.亚稳态:数据的转变没有符合时钟采样所需要的setup/holdtime时间,在时钟的上升沿或下降沿到来时正好采到数据的变化状态,此时,由于数据并没有稳定,所以会导致采到的数据不停变化,而不是逻辑0或者逻辑1,此时采到的数据会一致抖动,直到隔一段时间稳定。

处理亚稳态的方法:

(1)相位控制;

(2)多级寄存器;

(3)异步FIFO缓存;

三、跨时序处理的原理及方法?

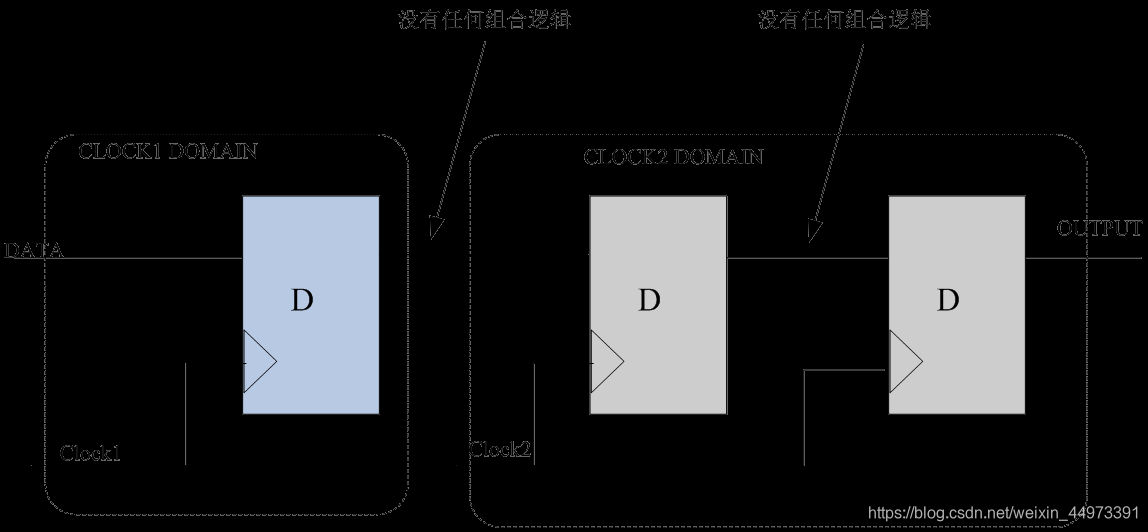

1.打两拍;

处理跨时域的数据有单字节和字节的区别,而打两拍的方式常见于处理单字节数据的跨时钟问题。所谓的打两拍,就是定义两级寄存器,对输入的数据进行延拍。

那么为什么是打两拍,而不是打一拍,打三拍呢?

那么为什么是打两拍,而不是打一拍,打三拍呢?

两级寄存器是一级寄存器的平方,两级并不能完全消除亚稳态危害,但是提高了可靠性,减少了其发生概率,总的来说,就是一级概率很大,三级改善不大。

2.异步双口RAM;

处理多字节数据的跨时钟域,一般采用异步双口RAM。我们假设有一个信号采集平台。ADC芯片提供源同步时钟60MHz,ADC芯片输出的数据在60MHz时钟上升沿变化,而FPGA内部需要使用100MHz的时钟来处理ADC采集到的数据。

在这样类似的场景中,我们便可以使用异步双口RAM来做跨时域处理。先利用ADC芯片提供的60MHz时钟将ADC输出的数据写入异步双口RAM,然后使用100MHz的时钟从RAM中读出。

在使用异步双口RAM来处理跨时域的应用中,也可以使用异步FIFO来达到同样的目的。

3.格雷码转换;

我们将ADC采样的数据写入RAM时,需要产生RAM的写地址,但是我们读出RAM中的数据时,肯定不是一上电就直接读取,而是要等RAM中有ADC的数据之后才去读RAM。这就需要100MHz的时钟对RAM的写地址进行判断,当写地址大于某个值之后再去读取RAM。

如果先将RAM的写地址转为格雷码,然后再将地址的格雷码进行打两拍,之后再再RAM的读时钟域将格雷码恢复成10进制。这种处理就相当于对单字节数据的跨时域处理了。

本文深入探讨了FPGA设计中跨时钟域处理的重要性,介绍了亚稳态的概念及其对设计稳定性的影响。文章详细阐述了处理亚稳态的三种方法:相位控制、多级寄存器和异步FIFO缓存。此外,还讲解了打两拍技术和异步双口RAM在处理跨时域数据时的应用,以及如何通过格雷码转换来解决字节数据的跨时钟域问题。

本文深入探讨了FPGA设计中跨时钟域处理的重要性,介绍了亚稳态的概念及其对设计稳定性的影响。文章详细阐述了处理亚稳态的三种方法:相位控制、多级寄存器和异步FIFO缓存。此外,还讲解了打两拍技术和异步双口RAM在处理跨时域数据时的应用,以及如何通过格雷码转换来解决字节数据的跨时钟域问题。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?