让你评估高速串行信号的串扰,你会说它们的串扰在-40db以下,没什么影响。但是如果让你评估像DDR这种并行信号的串扰,你说DQ0和DQ1的串扰-30db,DQ1和DQ2的串扰-25db,DQ2和DQ3的串扰……你慢慢数,我先走了。

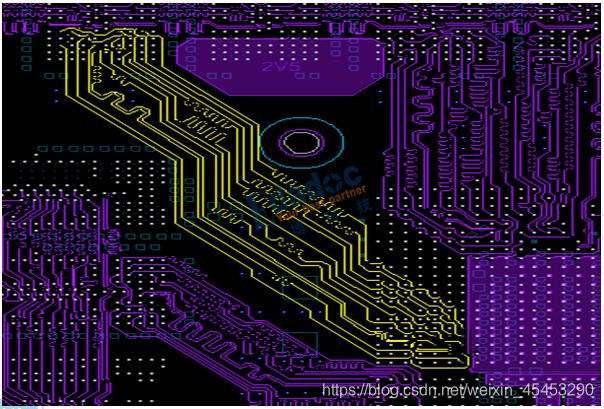

根据以往的经验,今天大家都会怀着无比沉重的心情来到公司上班,高速先生也表示深深的理解哈,所以今天的文章是非常的简洁而形象的,以便满足大家今天不想多动脑的欲望。记得前几篇文章提到过人工智能的话题,我们就接着说一点技术上的东西哈。在人工智能迅速冒起的热潮中,作为核心算力的DDR模块无疑出了一次很大的风头。因为在追求超大算力的情况下,人们对DDR的容量和速率要求越来越高。我们高速先生接触的算力卡一块比一块小,但是板内的DDR模块却有越来越多的趋势,动不动就上4通道、8通道,甚至更多。而且在颗粒数量不断提高的同时,我们要求的速率基本也越来越高,基本都是2400Mbps起步,最高的有做过3200Mbps的。加上板子密度越来越小,从我们这一年多以来接触的各种DDR的设计来看,可以毫不夸张的和大家说,现在DDR的设计难度可能已经超过了很多人的想象了……

做过DDR设计的同行都知道,在非常密的颗粒排布下,想成功的把所有的信号拉出来可能都要去条命,然后导通之后还要把手抓稳去做抖一下就让你想剁手的等长(5mil,2mil,我们有见过客户要求做1mil的……),当你以为可以收工的时候,客户还要抱着看上去和你商量的态度说你的间距能不能再拉开一点。

行……我们的设计工

本文通过简单直观的图表,解释DDR并行信号中串扰如何影响电平振荡和传输延时,强调在DDR设计中串扰分析的重要性,尤其是在高密度、高速率的DDR模块中,串扰可能造成的影响远大于预期。

本文通过简单直观的图表,解释DDR并行信号中串扰如何影响电平振荡和传输延时,强调在DDR设计中串扰分析的重要性,尤其是在高密度、高速率的DDR模块中,串扰可能造成的影响远大于预期。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1715

1715

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?