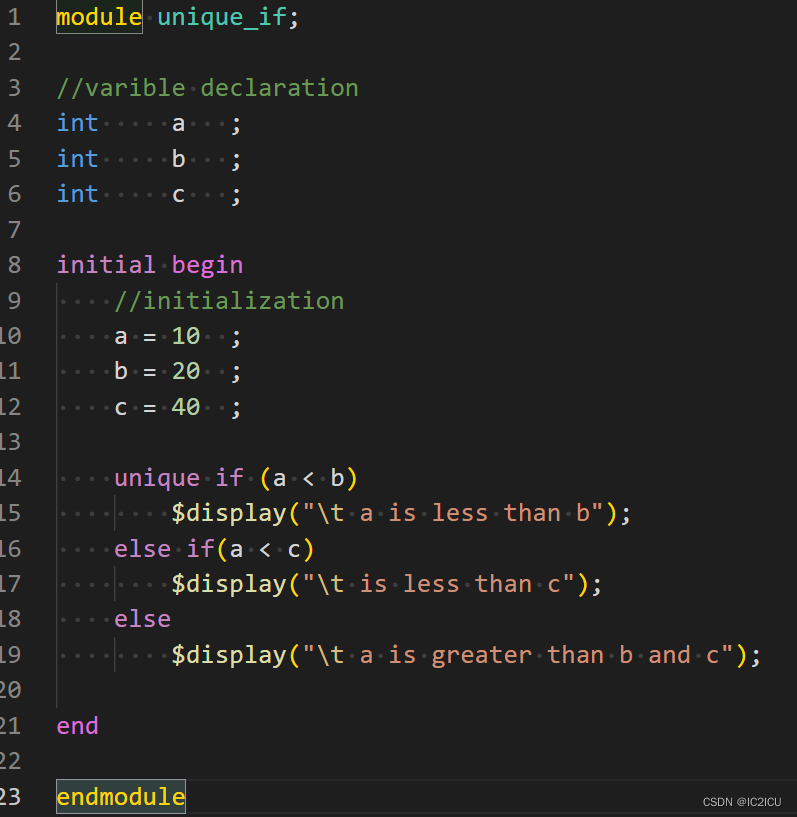

unique if

unique if 语句是并行的检查所有的条件,当超过一个条件满足、没有一个条件满足和没有与if像配对的else时,就会报错。

如下面的例子,有超过1个条件满足:

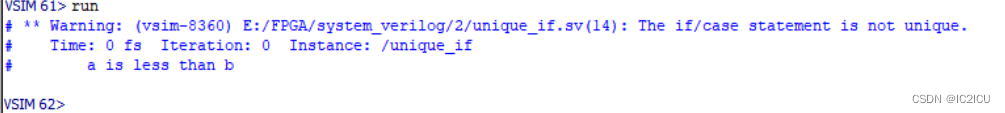

其输出结果为

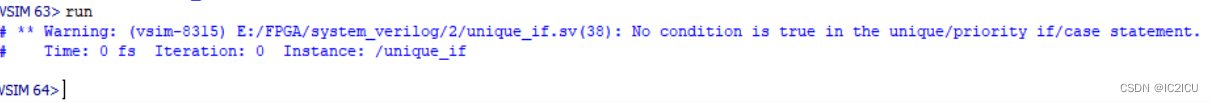

priority if

与verilog中理解差不多,在没有条件满足和没有与if相配对的else语句会报错。

module priority_if;

//variables declaration

int a,b,c;

initial begin

//initialization

a=50;

b=20;

c=40;

priority if ( a < b ) $display("\t a is less than b");

else if ( a < c ) $display("\t a is less than c");

end

endmodule

其输出结果为:

RT Warning: No condition matches in 'priority if' statement.

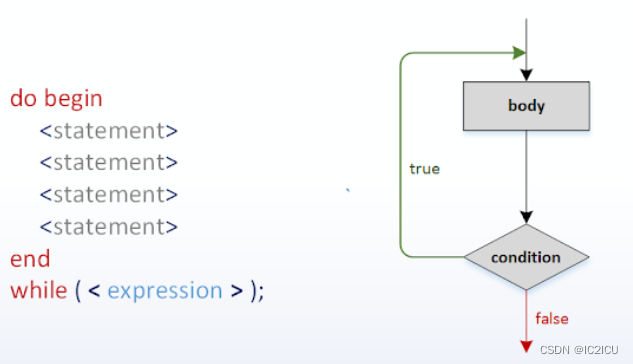

do while

do begin

// statement -1

...

// statement -n

end

while(condition);

while

while(condition) begin

// statement -1

...

// statement -n

end

本文详细介绍了SystemVerilog中的几种流程控制结构,包括uniqueif、priorityif、do-while、while、foreach、for、repeat和forever。每个结构通过实例展示了其用法和特点,并提供了相应的输出结果。uniqueif在有多个条件满足时会报错,priorityif在没有匹配的else语句时会警告,do-while和while循环根据条件执行,foreach用于遍历数组,for循环允许内部声明和初始化变量,repeat和forever则分别执行固定次数和无限次的循环。

本文详细介绍了SystemVerilog中的几种流程控制结构,包括uniqueif、priorityif、do-while、while、foreach、for、repeat和forever。每个结构通过实例展示了其用法和特点,并提供了相应的输出结果。uniqueif在有多个条件满足时会报错,priorityif在没有匹配的else语句时会警告,do-while和while循环根据条件执行,foreach用于遍历数组,for循环允许内部声明和初始化变量,repeat和forever则分别执行固定次数和无限次的循环。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2659

2659

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?