注:本文转自赛灵思中文社区论坛,源文链接在此。本文原作者为XILINX工程师John Blaine

以下为个人译文,仅供参考,如有疏漏之处,还请不吝赐教。

许多 FPGA 设计都难以达成所期望的性能目标。原因不尽相同,以下列出的只是其中部分可能的原因:

-

未遵循 UltraFast 设计方法

-

时序约束不良

-

过高资源利用率

-

控制集过多

-

未采用最优化时钟设置

-

逻辑层次过多,难以达成目标性能

-

布局规划不良

-

布线拥塞

-

因约束导致工具优化受限

通过阅读这篇博文,您将了解到“report_qor_suggestions”如何通过自动执行解决方案来解决限制 FPGA 性能的种种问题,从而提升您的工作效率。

如何才能轻松发现并快速修复这些问题?

Report QoR Suggestions

Report QoR Suggestions (RQS) 可识别设计问题,并提供工具开关和可影响工具行为的设计单元属性的解决方案,即便在无法自动执行解决方案的情况下也可提供文本修改建议。

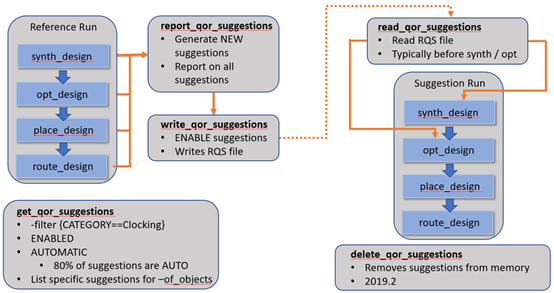

早在 Vivado 2019.1 中,RQS 就已经开始输出建议对象文件。这使我们可以对建议进行跟踪、自动完成其实现、改进每一项建议的验证工作并提供更复杂的建议。在此过程中新的命令和一些流程修改应运而生,如下所述:

1. “report_qor_suggesti

本文介绍了如何使用Vivado的report_qor_suggestions命令来识别和解决FPGA设计中的性能瓶颈,包括未遵循UltraFast设计方法、时序约束问题等。通过报告的自动建议,设计师可以提高设计效率和质量,实现更好的QoR。

本文介绍了如何使用Vivado的report_qor_suggestions命令来识别和解决FPGA设计中的性能瓶颈,包括未遵循UltraFast设计方法、时序约束问题等。通过报告的自动建议,设计师可以提高设计效率和质量,实现更好的QoR。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

274

274

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?