数字系统抽象层次

抽象层次 | 基本单元 | 电路的功能描述 | |

前端 | 系统级 | CPU、硬盘等 | 性能规格说明 |

算法级 | 算法 | 算法流程图 | |

寄存器变换级(RTL) /电路级 | 寄存器、ALU、MUX等 | 算法状态机图、有限状态机、数据流图、控制流图 | |

后端 | 逻辑门级 | 逻辑门 | 原理图 |

开关级 | 晶体管、R、L、C等 | 电压、电流 | |

物理(版图)级 | 几何图形 |

系统级

是数字系统设计的最高层次。一个系统可包含若干芯片,其中也会有若干类似于处理器、存储器,如设计一个低通滤波器等。

算法级

对整个系统的数学模型进行建模,一般通过对输入/输出之间的关系描述来模拟器件的行为,检验功能是否正确,不考虑具体硬件实现。

寄存器变换级(RTL)

描述数据在寄存器之间的流动和如何处理、控制这些数据流动的模块,考虑具体硬件电路实现。

Verilog在抽象级上建模

混合描述=行为描述(Behavior)+数据流描述(Data Flow)+门级原语结构描述 (Structure)

行为级

| ||||

RTL级/功能级

| ||||

逻辑门级

| ||||

开关级 | ||||

版图级 | ||||

抽象级描述:

在不同的设计阶段采用不同的抽象级

首先在行为级描述各功能块,以降低描述难度,提高仿真速度

在综合前将个功能块进行RTL级描述

在综合的库中的大多数单元采用门极描述

Verilog还有一定的晶体管级描述能力及算法级描述能力

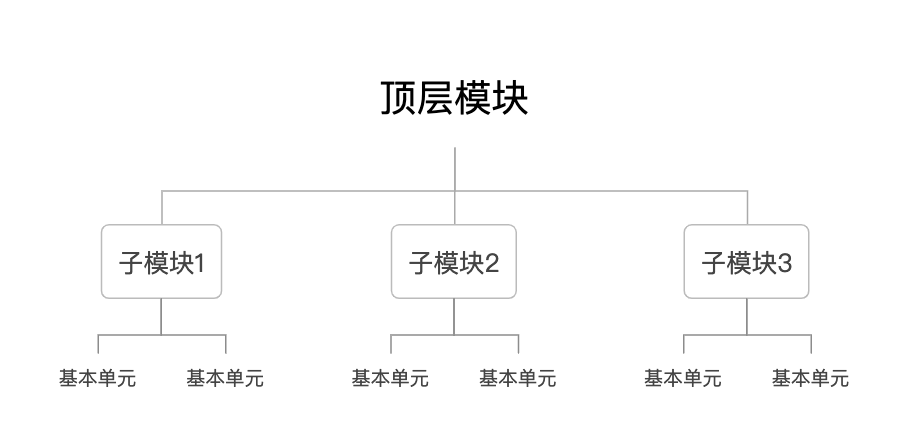

自顶向下(Top-Down)的结构化设计方式

从高到低(上到下)顺序依次为:系统级-算法级- RTL-逻辑门极-开关级,版图级

结构化设计中模块的分解,实际是高抽象层次模块分解为低抽象层次部件的过程。

Top-Down设计方法

一个系统由总设计师先进行系统描述,将系统划分为若干模块,编写模块模型(一般为行为级),仿真验证后,再把这些模块分配给下一层的设计师,由他们完成模块的具体设计,最后总设计师负责各模块的借口定义。

典型数字系统设计流程

首先进行系统设计,接着进行算法设计和验证,之后进行RTL设计和验证,然后进行逻辑综合,向foundry提供网表,由其进行版图设计,返回最终的网表,用EDA进行后仿真,验证版图设计网表功能与RTL级是否一致,最后向foundry流片。

简述Verilog如何建模

数字电路有2种基本要素:线(wire)和器件(module),Verilog建模就是用 HDL语言将数字电路的两个基本要素的特性及相互之间的连接关系进行描述的过程。

567

567

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?