干法刻蚀若干问题

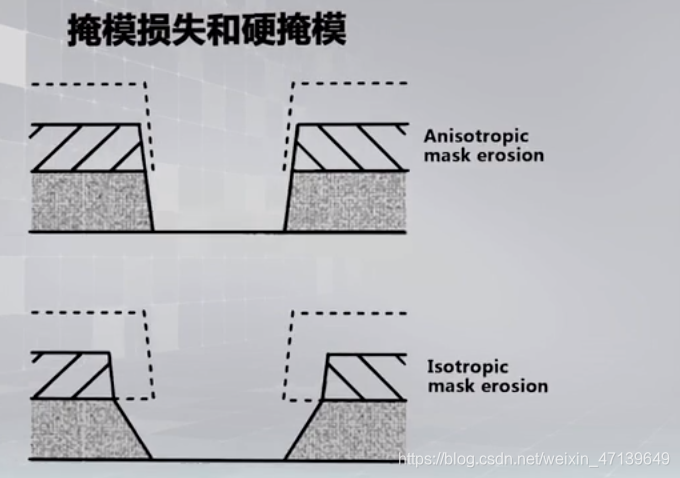

掩模损失和硬掩模

在刻蚀中,光刻胶的开口也会被刻蚀,导致掩模展宽,开口变大,这降低了刻蚀的精度;为避免这种情况,

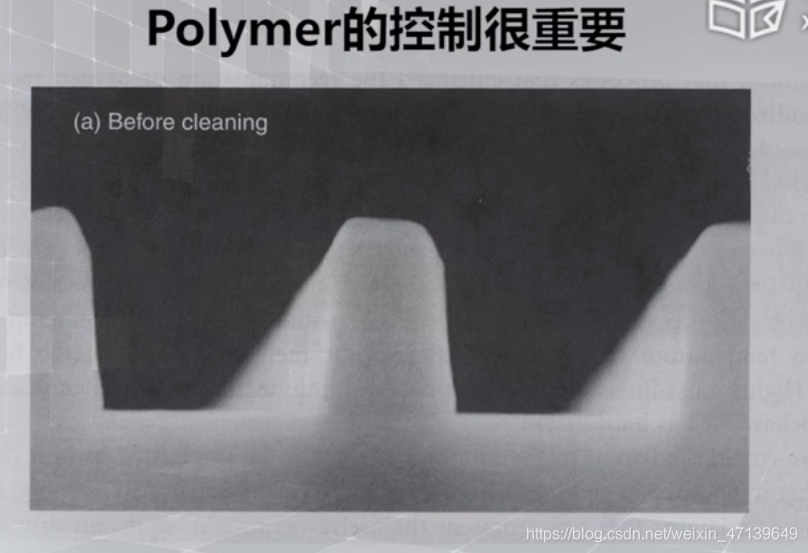

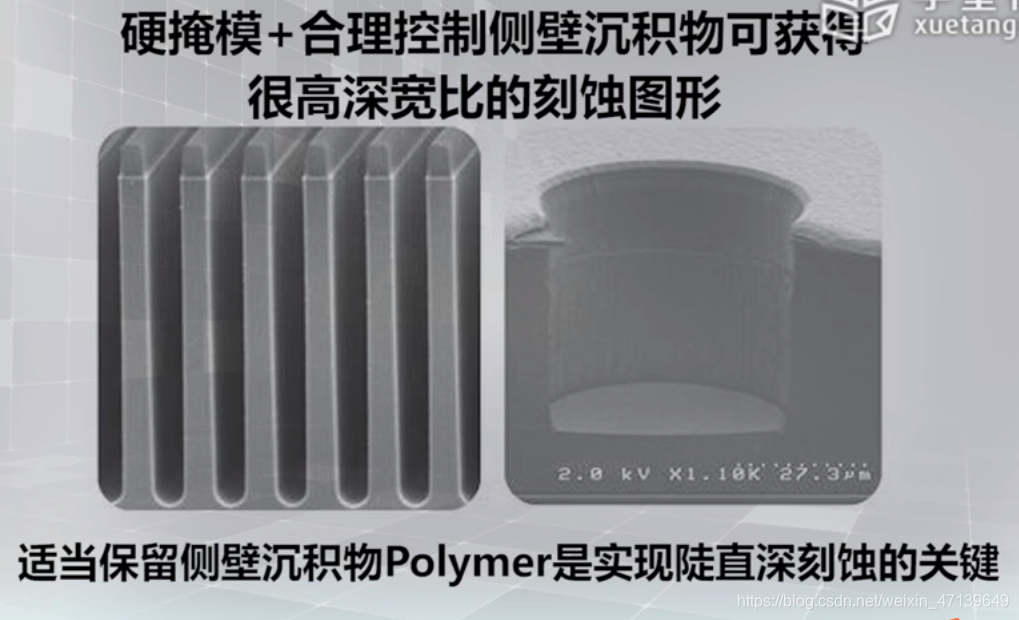

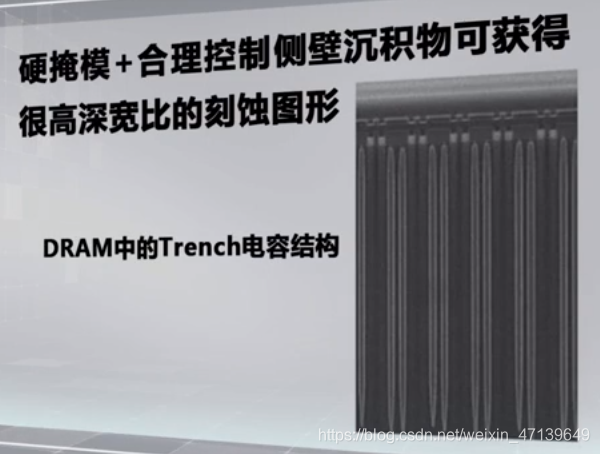

侧壁沉积物的控制

可以有效保护侧壁,但是过多会使窗口缩小;

侧壁沉积物过多,导致下面的形貌:

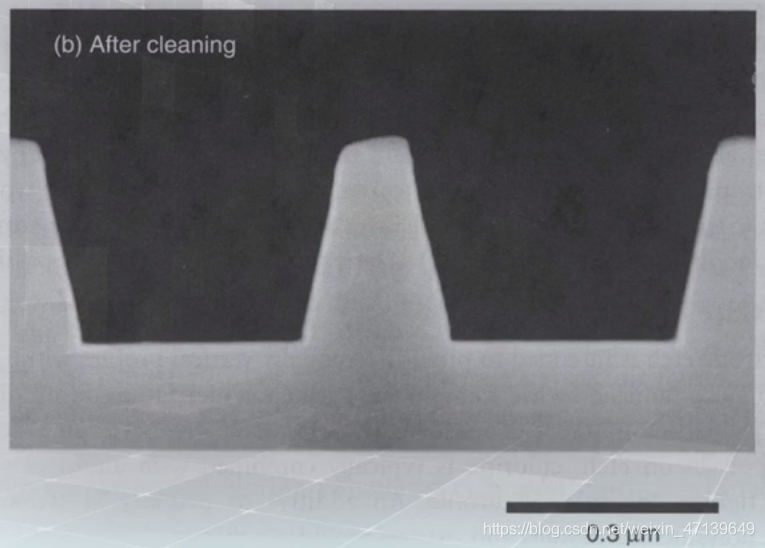

清除沉积物后的刻蚀结果:

可以通过通入氧气来去除Polymer;

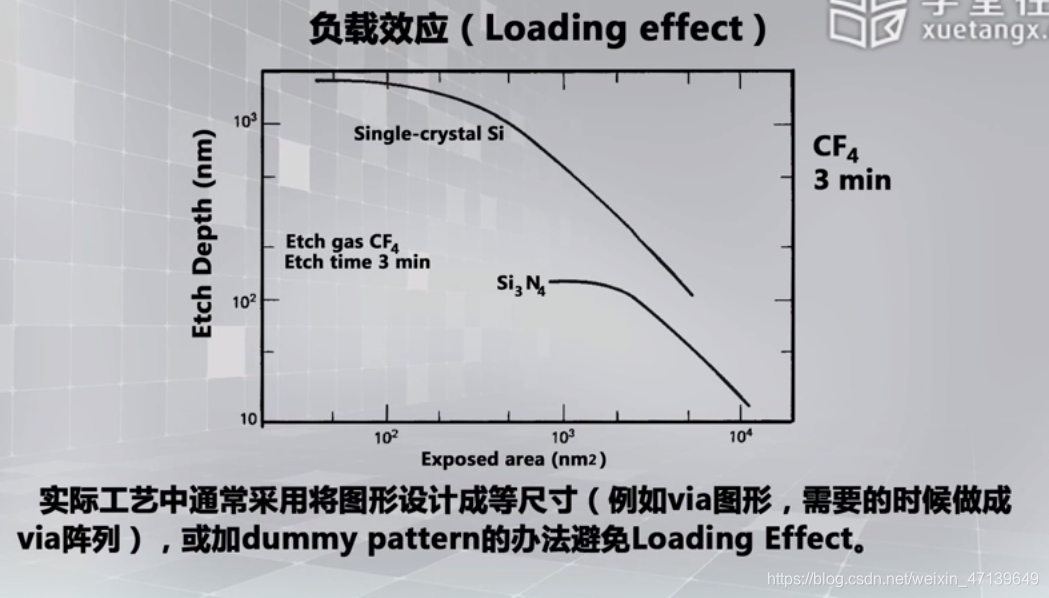

负载效应

由于图形的疏密程度不同,导致刻蚀速率不同;

通过加入一些Dummy pattern 来避免负载效应;

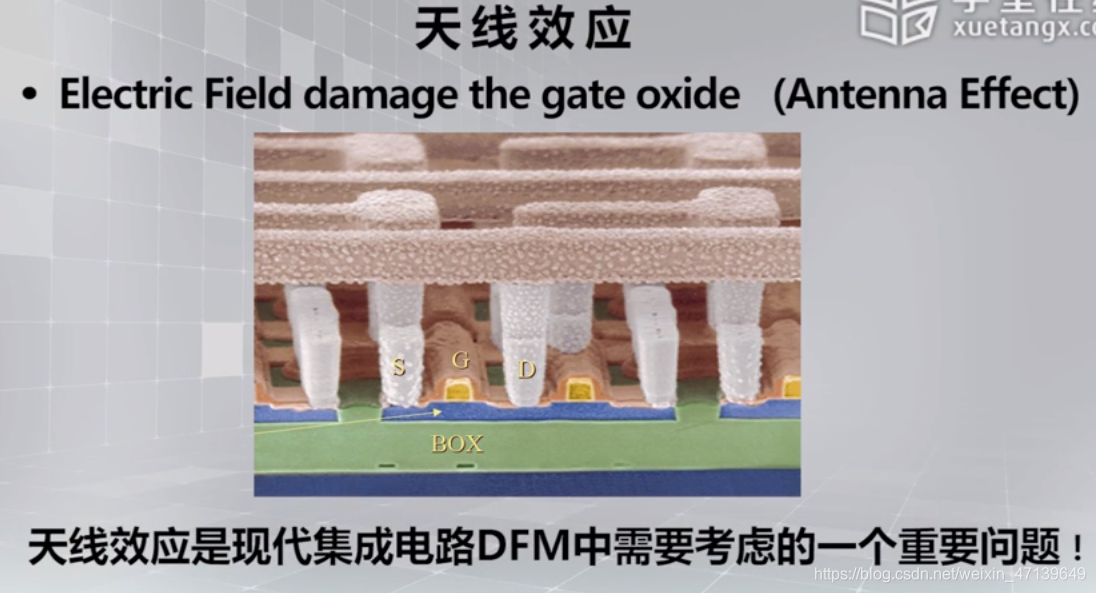

天线效应

在芯片生产过程中,暴露的金属线或者多晶硅(polysilicon)等导体,就象是一根根天线,会收集电荷(如等离子刻蚀产生的带电粒子)导致电位升高。天线越长,收集的电荷也就越多,电压就越高。若这片导体碰巧只接了MOS 的栅,那么高电压就可能把薄栅氧化层击穿,使电路失效,这种现象我们称之为“天线效应”。随着工艺技术的发展,栅的尺寸越来越小,金属的层数越来越多,发生天线效应的可能性就越大。

举例:

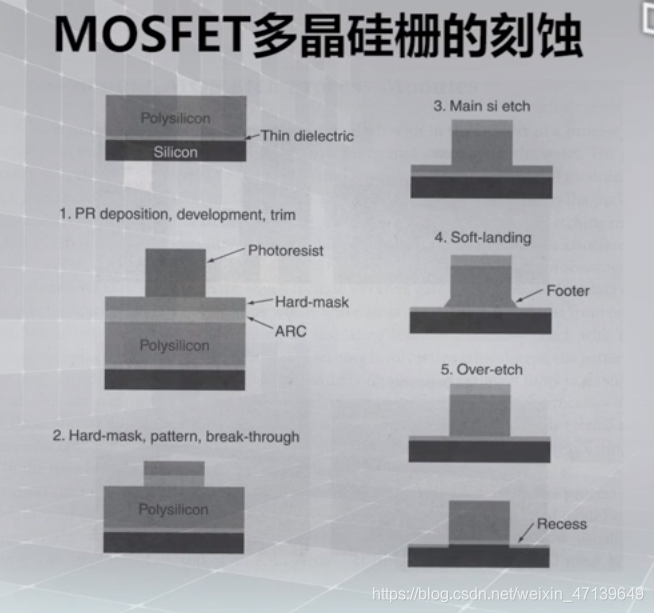

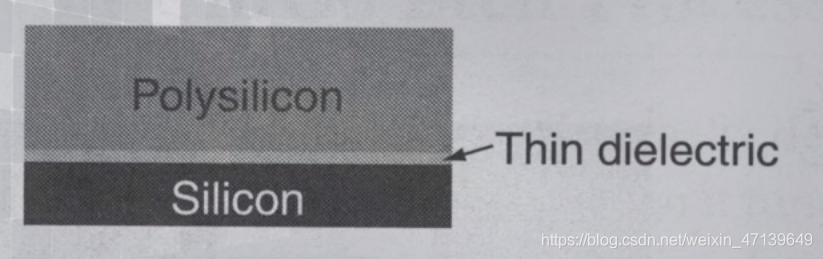

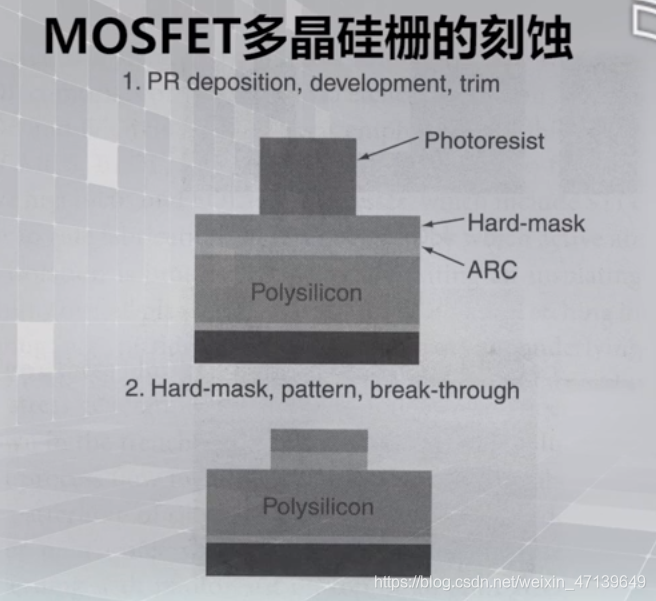

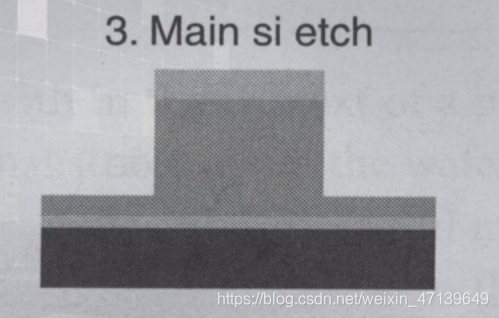

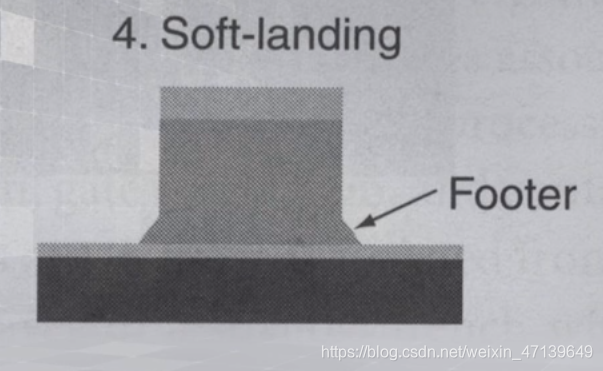

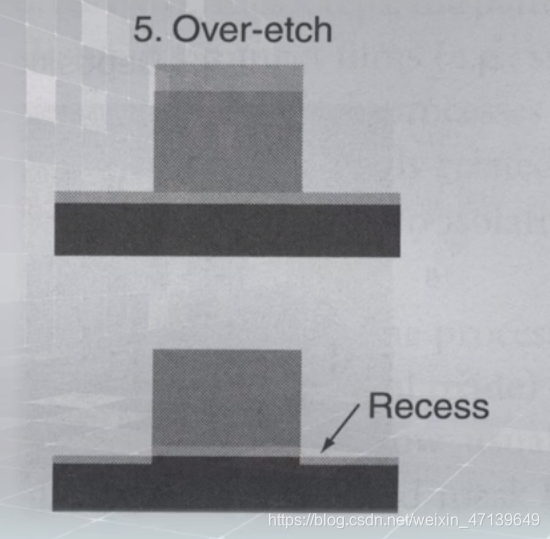

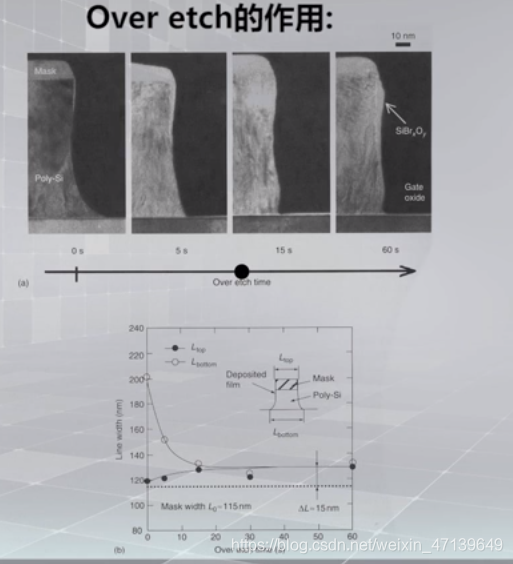

1. 多晶硅栅的刻蚀

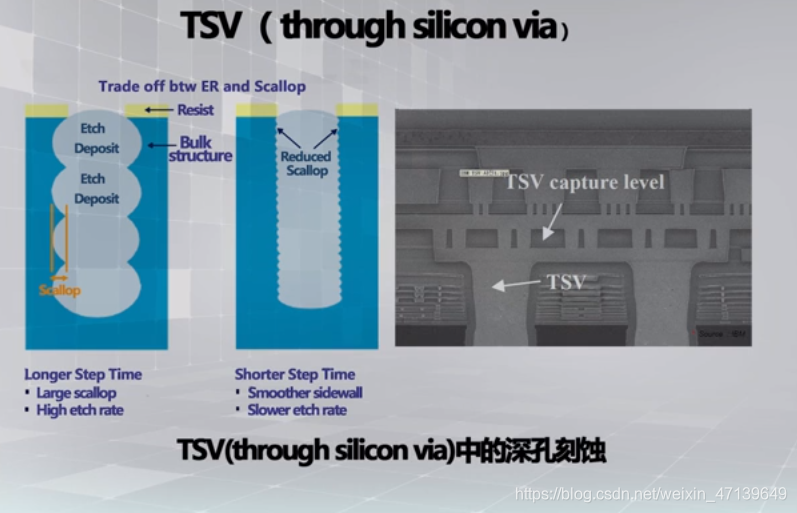

2. TSV的刻蚀

2153

2153

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?