规律总结:

纳米级MOS栅氧瞬态击穿电压一般性规律:

1.栅极氧化层越厚其相应瞬态击穿电压越高;

2.TLP脉冲的上升时间越短,栅氧化层瞬态击穿电压越低;

3.在沟道长度在微米量级时,瞬态击穿电压随着MOS栅氧面积的减小而增大;

4.当沟道长度在深亚微米尺度以下,瞬态击穿电压随着MOS沟道长度的减小而减小;

5.当沟道长度和MOS栅氧面积都达到工艺精度的最小值时,器件鲁棒性最差,栅氧瞬态击穿电压最低。

另外,在电路设计中需要注意的是,当射频电路中输入输出端需使用片上MOS电容作为滤波电容,或输入端MOS栅极暴露在ESD之下时,尽量避免使用最小沟道长度,使用0.5um或以上的沟长有利于提高栅氧击穿电压。此外,MOS的宽度W与叉指数F的乘积不能过小也不能太大,控制在200um左右为较优选择。

实验数据

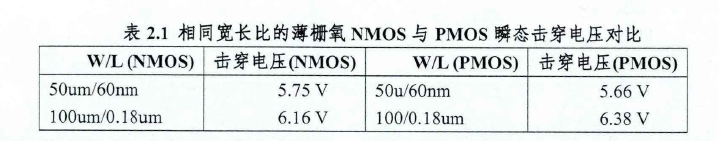

首先针对两组相同宽长比(W/L)的NMOS和PMOS管栅氧结构进行TLP测试,实验结果见表2.1, PMOS的栅氧TLP击穿电压与NMOS并无明显差异。

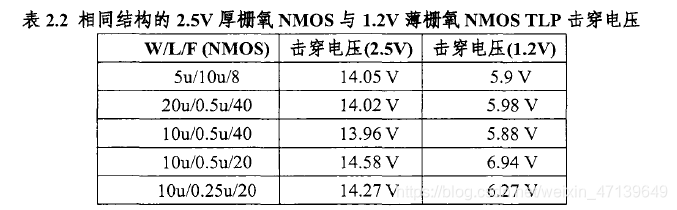

其次针对五组相同叉指宽度(W)、沟长(L)和叉指数(F)的1.2V与2.5V的NMOS管栅氧结构进行TLP测试,实验结果见表2.2。可以看出,厚栅氧NMOS击穿电压约为14V左右,远远高于6V左右的薄栅氧NMOS的击穿电压。另外由于薄栅氧MOS管的栅氧厚度为几个纳米,在纳米尺度下控制薄栅氧工艺的均勾性比2.5V的厚栅氧MOS管相对要难,造成了 1.2V MOS管栅氧瞬态击穿电压个体差异略大。

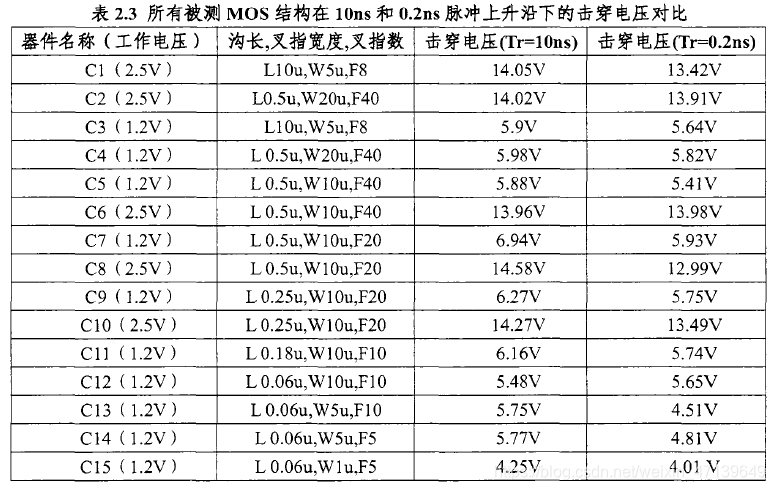

针对15组沟道长度分别从0.06um变化到lOum,叉指宽度从lum变化到20um,叉指数目从5变化到40的不同NMOS测试结构。分别用10ns和0.2ns上升时间(Tr)的TLP脉冲对15组NMOS进行测试,实验结果整理见表2.3。

可以总结出2.5V的厚栅氧MOS在TLP脉冲下的击穿电压在13 V ~15V之间,1.2V的薄栅氧MOS在TLP脉冲下的击穿电压在4V ~ 7V之间。

针对1.2V的NMOS,如图2.3所示,对比C3、C4和C5可以看出沟长在0.5um ~ 10um范围内变化对其TLP击穿电压无太大影响。对比C5和C7可以得出,在沟长同为0.5um的情况下,叉指数从40减少到20,即MOSFET栅氧面积减少一半,此时TLP击穿电压5.88V提高到了 6.94V。对比C7、C9、C11和C12可以看出,当沟道长度从0.5urn不断降低到0.06iim,栅氧面积并不作为主导因素,NMOS的TLP击穿电压随沟长不断降低。对比C12~C15可以看出,当沟长为0.06um的NMOS栅氧面积不断减小到WF=lum5时,TLP击穿电压降低至4.25V。

通过对比表2.3中10ns上升沿和0.2ns上升沿TLP下的击穿电压,大部分被测MOS栅氧击穿电压在0.2ns的上升沿TLP脉冲下比10ns上升沿TLP脉冲更低。这主要由于在相同的100ns脉冲宽度下,当脉冲上升时间越短,由于/ = C^,瞬间通过栅电容的漂移电流越大,导致栅氧更容易发生击穿失效。因dt此,越是快速的ESD脉冲(如CDM ESD脉冲),ESD防护器件越容易来不及响应及开启,造成内部电路脆弱的薄氧化层结构过早的受到损坏。

文章来源:<先进工艺下集成电路的静电放电防护设计及其可靠性研究>

本文详细探讨了纳米级MOS栅氧瞬态击穿电压的规律,包括栅层厚度、TLP脉冲特性、沟道尺寸、工艺精度等因素的影响,并提供了电路设计中关键注意事项。实验数据展示了不同结构NMOS和PMOS的TLP击穿电压对比,以及优化策略建议。

本文详细探讨了纳米级MOS栅氧瞬态击穿电压的规律,包括栅层厚度、TLP脉冲特性、沟道尺寸、工艺精度等因素的影响,并提供了电路设计中关键注意事项。实验数据展示了不同结构NMOS和PMOS的TLP击穿电压对比,以及优化策略建议。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?