Q:介绍完D触发器分频器概念原理之后,本期我们设计实现四分频D触发器分频器。

A:使用DE2-115开发板的KEY[0]作为时钟clk输入,LEDR[1:0]显示Q0和Q1的输出值,分别表示二分频和四分频的结果。

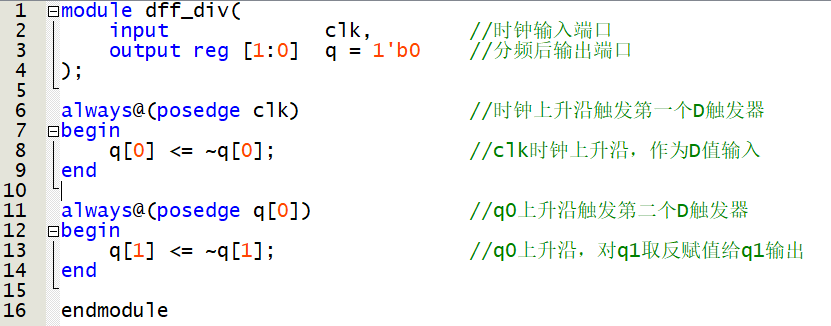

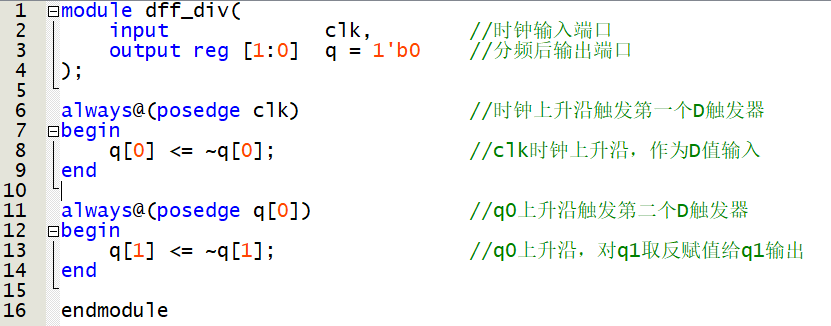

2个D触发器级联实现4分频的Verilog代码:

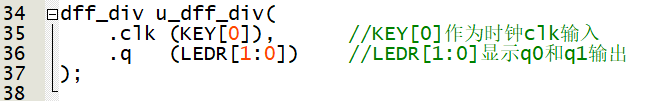

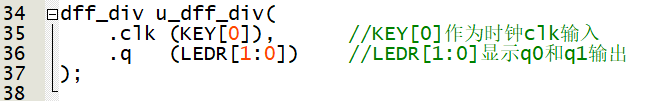

在顶层.v文件中例化分频器:

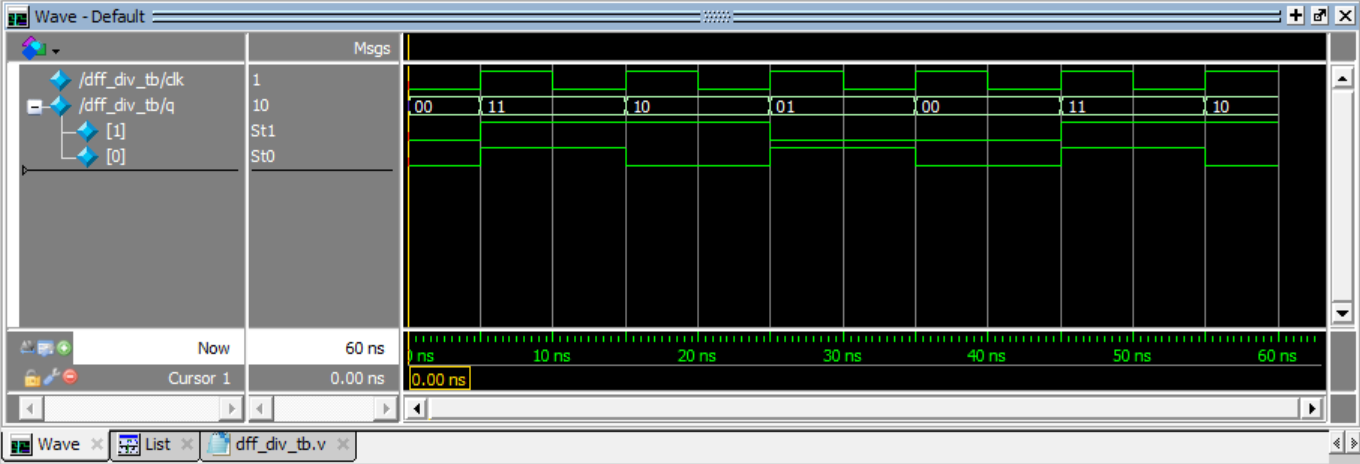

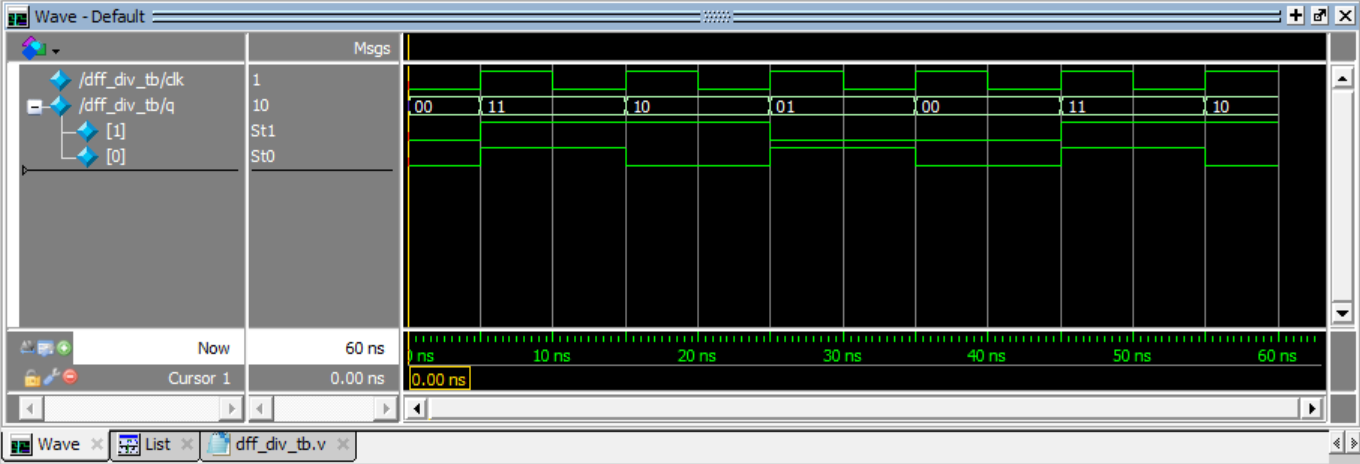

Modelsim仿真结果:输出Q0的波形频率为clk频率的1/2,即二分频;输出Q1的波形频率为clk频率的1/4,即四分频。

Q:介绍完D触发器分频器概念原理之后,本期我们设计实现四分频D触发器分频器。

A:使用DE2-115开发板的KEY[0]作为时钟clk输入,LEDR[1:0]显示Q0和Q1的输出值,分别表示二分频和四分频的结果。

2个D触发器级联实现4分频的Verilog代码:

在顶层.v文件中例化分频器:

Modelsim仿真结果:输出Q0的波形频率为clk频率的1/2,即二分频;输出Q1的波形频率为clk频率的1/4,即四分频。

884

884

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?