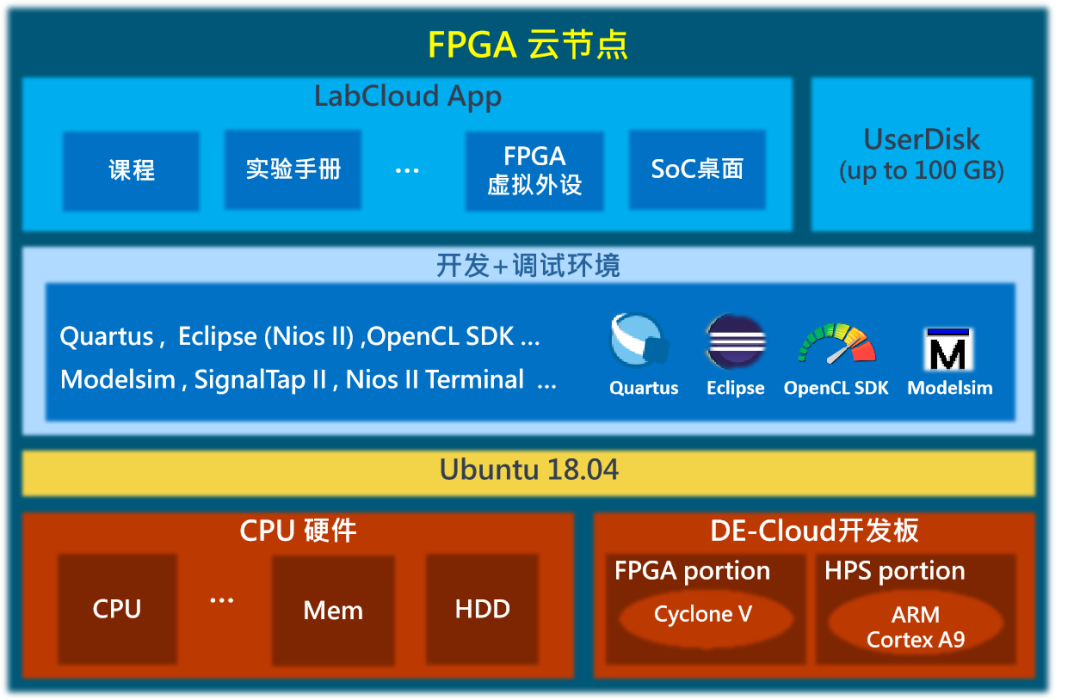

友晶科技依托其在FPGA技术领域的深厚积累,成功研发出了一套完整的FPGA云平台解决方案(即FPGA 硬件在线实验云,简称LabCloud )。LabCloud 是一个高效、实用的学习平台,目前已在多个学校成功部署。

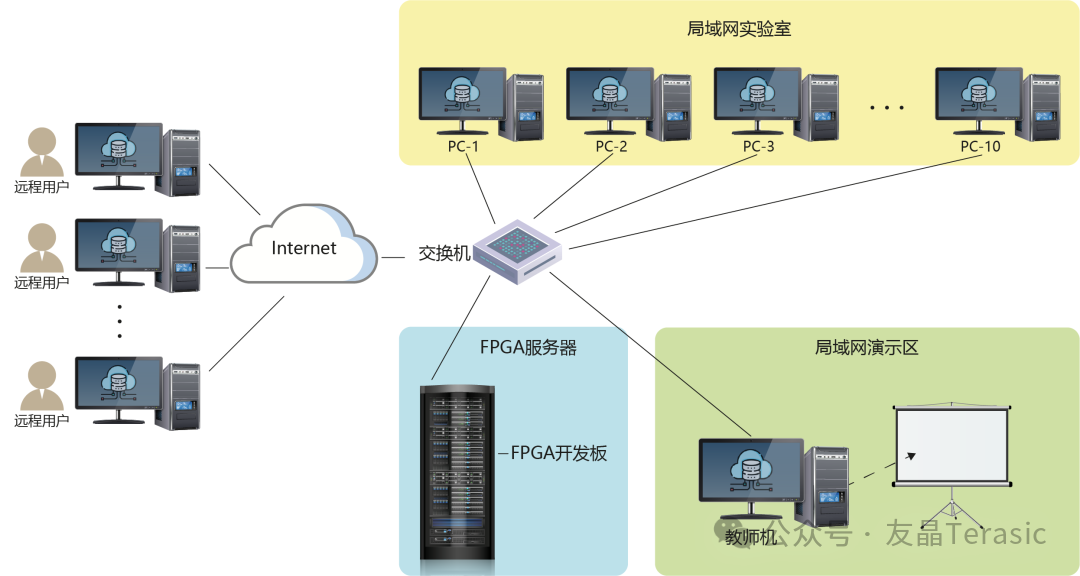

LabCloud 是通过 B/S 架 构 (Browser/Server)实现将 FPGA 硬件和 FPGA 开发环境搬移至云端,使用者无需搭建任何开发环境,只需使用浏览器访问 LabCloud 即可随时随地在任意终端进行 FPGA 学习与实操。

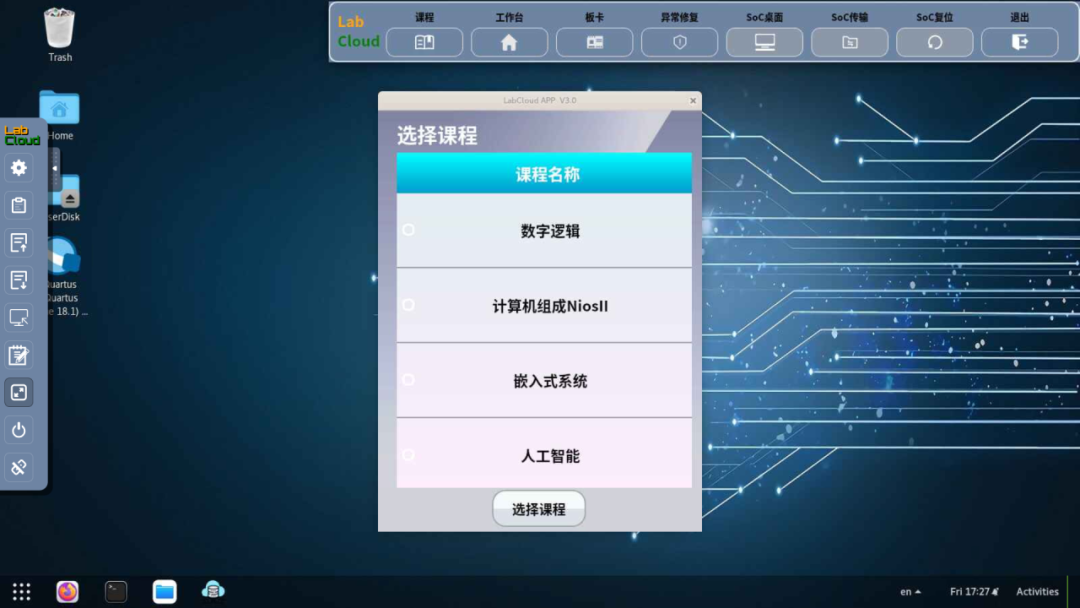

LabCloud 不仅可提供丰富的课程(如数字逻辑、计算机组成、嵌入式设计、人工智能等),还提供了众多网页交互功能,如文件上传下载、作业提交、特色课程定制等等;为了增进教学效果,还开发了远程协助、教学广播等教学互动功能,能够有效支撑学校的教学、科研、管理等各项工作。

1765

1765

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?