实现D触发器,有输入信号d,时钟信号clk,输出信号q

module top(d,clk,q);

input d,clk;

output q;

reg q;

always @(posedge clk)begin

q <= d;

end

module test(

);

reg d,clk;

wire q;

top f(.d(d),.clk(clk),.q(q));

initial begin

clk = 1;d = 0;

#20 d = 1;

#20 d = 0;

#5 d = 1;

#10 d = 0;

#20 d = 1;

#15 d = 0;

#5 d = 1;

#10 $stop;

end

always begin

#5 clk = ~clk;

end

endmodule

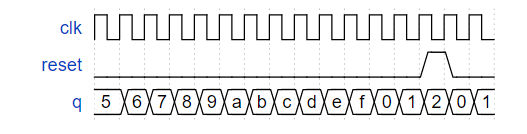

创建8个D触发器。所有DFF应由clk的上升沿触发。

module top(d,clk,q);

input d,clk;

output q;

wire[7:0] d;

reg[7:0] q;

always @(posedge clk)begin

q <= d;

end

module test(

);

reg[7:0] d;

reg clk;

wire[7:0] q;

top f(.d(d),.clk(clk),.q(q));

initial begin

clk <= 1;d <= 0;

#5000 $stop;

end

always begin

#5 clk <= ~clk;

#7 d <= d + 1;

end

endmodule

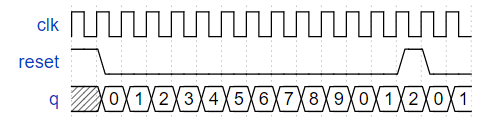

创建具有高电平有效同步复位的8 D触发器。所有DFF应由clk的上升沿触发。

给定一个时钟信号clk上升沿有效,一个复位信号reset高电平有效,一个位宽为8的输入信号d,一个位宽为8的输出信号q

module top(d,clk,reset,q);

input[7:0] d;

input clk,reset;

output q;

reg[7:0] q;

always @(posedge clk)begin

if(reset)

q <= 8'd0;

else

q <= d;

end

module test(

);

reg[7:0] d;

reg clk,reset;

wire[7:0] q;

top f(.d(d),.clk(clk),.reset(reset),.q(q));

initial begin

clk <= 0;d <= 8'd13;reset <= 1;

#15 reset <= 0;

#35 reset <= 1;

#15 reset <= 0;

#10 reset <= 1;

#25 reset <= 0;

#10 $stop;

end

always begin

#5 clk <= ~clk;

#5 d <= d + 1;

end

endmodule

创建具有高电平有效异步复位的 8 个 D 触发器。所有DFF应由clk的上升沿触发。

module top(d,clk,reset,q);

input[7:0] d;

input clk,reset;

output q;

reg[7:0] q;

always @(posedge clk or negedge reset)begin

if(!reset)

q <= 8'd0;

else

q <= d;

//异步复位的触发器(复位与寄存不能一起操作)

end

module test(

);

reg[7:0] d;

reg clk,reset;

wire[7:0] q;

top f(.d(d),.clk(clk),.reset(reset),.q(q));

initial begin

clk <= 1;d <= 8'd13;reset <= 1;

#15 reset <= 0;

#5 reset <= 1;

#14 reset <= 0;

#7 reset <= 1;

#21 reset <= 0;

#4 reset <= 1;

#24 reset <= 0;

#6 reset <= 1;

#16 reset <= 0;

#10 $stop;

end

always #5 clk <= ~clk;

always #10 d <= d + 3;;

endmodule

DFF+gate(Exams/m2014 q4d)

实现以下电路

实际模块

module top(clk,in,out);

input clk,in;

output out;

reg out;

initial begin

out = 0;

end

always@(posedge clk)

out = in ^ out;

endmodule

模块实例化

module test(

);

reg in,clk;

wire out;

top f(.clk(clk),.in(in),.out(out));

initial begin

in = 0;clk = 0;

#200 $stop;

end

always #10 clk = ~clk;

always #7 in = ~in;

endmodule

总结:

reg 不能连接到模块实例化的输出端口;

reg 不能 用作实际模块声明中的输入;

模块实例化的输出端口初始化,要在实际模块中进行

计数器

构建一个4位二进制计数器,其计数范围为0到15(含0和15),其周期为16。复位输入是同步的,应将计数器复位为0。

module top(clk,reset,q);

input clk,reset;

output q;

reg[3:0] q;

initial q <= 0;

always@(posedge clk)begin

if(reset)

q <= 4'd0;

else if(q == 4'd15)

q <= 0;

else

q <= q + 1;

end

module test(

);

reg clk,reset;

wire[3:0] q;

top f(.clk(clk),.reset(reset),.q(q));

initial begin

clk <= 0;reset <= 0;

#500 $stop;

end

always #5 clk <= ~clk;

always begin

# 177 reset <= 1;

#20 reset <= 0;

end

endmodule

建立一个十进制计数器,该计数器的计数范围为0到9(含0和9),周期为10。复位输入是同步的,应将计数器复位为0。

module top(clk,reset,q);

input clk,reset;

output q;

reg[3:0] q;

initial q <= 0;

always@(posedge clk)begin

if(reset)

q <= 4'd0;

else if(q == 4'd9)

q <= 0;

else

q <= q + 1;

end

module test(

);

reg clk,reset;

wire[3:0] q;

top f(.clk(clk),.reset(reset),.q(q));

initial begin

clk <= 0;reset <= 0;

#500 $stop;

end

always #5 clk <= ~clk;

always begin

# 127 reset <= 1;

#14 reset <= 0;

end

endmodule

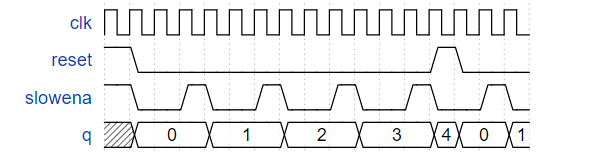

建立一个十进制计数器,该计数器的计数范围为0到9(含0和9),周期为10。复位输入是同步的,应将计数器复位为0。我们希望能够暂停计数器,而不是总是在每个时钟周期都递增,因此,slowena输入指示计数器应何时递增。

module top(clk,reset,slowna,q);

input clk,reset,slowna;

output q;

reg[3:0] q;

initial q <= 0;

always@(posedge clk)begin

if(reset)

q <= 4'd0;

else if(slowna)begin

if(q == 4'd9)

q <= 0;

else

q <= q + 1;

end

end

module test(

);

reg clk,reset,slowna;

wire[3:0] q;

top f(.clk(clk),.reset(reset),.slowna(slowna),.q(q));

initial begin

clk <= 0;reset <= 0;slowna <= 1;

#500 $stop;

end

always #5 clk <= ~clk;

always begin

#70 slowna <= 0;

#10 slowna <= 1;

end

always begin

# 127 reset <= 1;

#14 reset <= 0;

end

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?