数字电路基础

第一章 时序逻辑电路和组合逻辑电路

组合逻辑

组合逻辑一般指的是一些门电路或者选择器、比较器一起组成的逻辑.

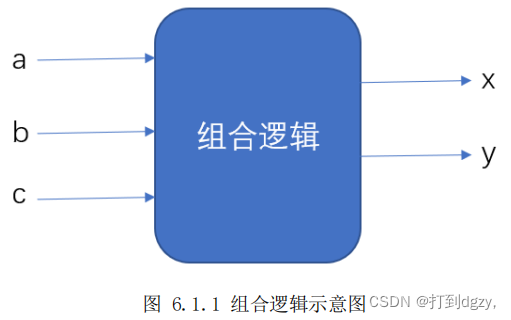

下面我们来看下上面是组合逻辑,如下图所示:

从上图中,我们可以看出,a/b/c 为组合逻辑的输入,x 和 y 为组合逻辑的输出,x 和 y 的值只取决于a/b/c 的当前的输入值,和 a/b/c 的之前的输入是没有任何关系的,这种电路我们就叫做组合逻辑电路。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。组合逻辑电路没有记忆功能,没有反馈环路。时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

组合逻辑电路的一般分析方法(组合逻辑电路图→求解逻辑功能)如下:

⚫ 组合逻辑电路图

⚫ 列出逻辑函数表达式(迭代法,由输入逐级向后推)

⚫ 求标准表达式或简化的表达式(转换或化简)

⚫ 列出相应的真值表→判断电路功能。

组合逻辑毛刺消除

信号在 IC/FPGA 器件中通过逻辑单元连线时,是存在延时的。延时的大小不仅和连线的长短和逻辑单元的数目有关,而且也和器件的制造工艺、工作环境等有关。因此,信号在器件中传输的时候,所需要的时间是不能精确估计的,当多路信号同时发生跳变的瞬间,就产生了“竞争冒险”。这时,往往会出现一些不正确的尖峰信号,这些尖峰信号就是“毛刺”。

毛刺是数字电路设计中的棘手问题,它的出现会影响电路工作的稳定性、可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。

1、组合逻辑输出加寄存器

去毛刺原理就是用一个寄存器去读带毛刺的信号,利用寄存器对输入信号的毛刺不敏感的特点(寄存器一般只在时钟跳变沿对输入信号敏感),去除信号中的毛刺。

2、信号同步法

由于大多数毛刺都比较短(大概几个纳秒),只要毛刺不出现在时钟跳变沿,毛刺信号就不会对系统造成危害了。因此一般认为,只要在整个系统中使用同一个时钟就可以实现系统同步。下面介绍两种具体的信号同步方法。

(1)信号延时同步法

(2)状态机控制

3、格雷码计数器

对于一般的二进制或十进制计数器,在计数时,将有多位信号同时跳变。

本文介绍了组合逻辑电路和时序逻辑电路的基本概念和特点,强调组合逻辑电路的即时输出特性以及时序逻辑电路的记忆功能。针对组合逻辑中的毛刺问题,提出了寄存器消除法、信号同步法等解决方案,包括信号延时同步和状态机控制,并提及格雷码计数器在减少信号跳变冲突中的应用。

本文介绍了组合逻辑电路和时序逻辑电路的基本概念和特点,强调组合逻辑电路的即时输出特性以及时序逻辑电路的记忆功能。针对组合逻辑中的毛刺问题,提出了寄存器消除法、信号同步法等解决方案,包括信号延时同步和状态机控制,并提及格雷码计数器在减少信号跳变冲突中的应用。

1566

1566

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?