Hadd

Create a half adder. A half adder adds two bits (with no carry-in) and produces a sum and carry-out.

Expected solution length: Around 2 lines.

Module Declaration

module top_module(

input a, b,

output cout, sum );

Write your solution here

module top_module(

input a, b,

output cout, sum );

assign cout = a&b;

assign sum = a ^ b;

endmoduleFadd

Create a full adder. A full adder adds three bits (including carry-in) and produces a sum and carry-out.

Expected solution length: Around 2 lines.

Module Declaration

module top_module(

input a, b, cin,

output cout, sum );

Write your solution here

module top_module(

input a, b, cin,

output cout, sum );

assign cout = a&b | a&cin | b&cin;

assign sum = a^b^cin;

endmodule

Adder3

Now that you know how to build a full adder, make 3 instances of it to create a 3-bit binary ripple-carry adder. The adder adds two 3-bit numbers and a carry-in to produce a 3-bit sum and carry out. To encourage you to actually instantiate full adders, also output the carry-out from each full adder in the ripple-carry adder. cout[2] is the final carry-out from the last full adder, and is the carry-out you usually see.

Module Declaration

module top_module(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

Write your solution here

module top_module(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

full_adder f1(a[0], b[0], cin, cout[0], sum[0]);

full_adder f2(a[1], b[1], cout[0], cout[1], sum[1]);

full_adder f3(a[2], b[2], cout[1], cout[2], sum[2]);

endmodule

module full_adder(

input a,

input b,

input cin,

output cout,

output sum );

assign sum = a ^ b ^ cin;

assign cout = a&b | a&cin | b&cin;

endmoduleExams/m2014 q4j

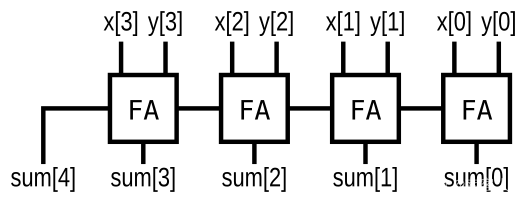

Implement the following circuit:

("FA" is a full adder)

Module Declaration

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

Write your solution here

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

wire [3:0]cout;

full_adder f1(x[0], y[0], 0, cout[0], sum[0]);

full_adder f2(x[1], y[1], cout[0], cout[1], sum[1]);

full_adder f3(x[2], y[2], cout[1], cout[2], sum[2]);

full_adder f4(x[3], y[3], cout[2], cout[3], sum[3]);

assign sum[4] = cout[3];

endmodule

module full_adder(

input x,

input y,

input cin,

output cout,

output sum);

assign cout = x&y | x&cin | y&cin;

assign sum = x^y^cin;

endmodule网页答案:

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum

);

// This circuit is a 4-bit ripple-carry adder with carry-out.

assign sum = x+y; // Verilog addition automatically produces the carry-out bit.

// Verilog quirk: Even though the value of (x+y) includes the carry-out, (x+y) is still considered to be a 4-bit number (The max width of the two operands).

// This is correct:

// assign sum = (x+y);

// But this is incorrect:

// assign sum = {x+y}; // Concatenation operator: This discards the carry-out

endmoduleExams/ece241 2014 q1c

Assume that you have two 8-bit 2's complement numbers, a[7:0] and b[7:0]. These numbers are added to produce s[7:0]. Also compute whether a (signed) overflow has occurred.

Module Declaration

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

);

Hint...

A signed overflow occurs when adding two positive numbers produces a negative result, or adding two negative numbers produces a positive result. There are several methods to detect overflow: It could be computed by comparing the signs of the input and output numbers, or derived from the carry-out of bit n and n-1.

Write your solution here

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

); //

assign s = a + b;

assign overflow = a[7]&b[7]&~s[7] | ~a[7]&~b[7]&s[7];

endmodule

Adder100

Create a 100-bit binary adder. The adder adds two 100-bit numbers and a carry-in to produce a 100-bit sum and carry out.

Expected solution length: Around 1 line.

Module Declaration

module top_module(

input [99:0] a, b,

input cin,

output cout,

output [99:0] sum );

Hint...

There are too many full adders to instantiate, but behavioural code works well here. Also see the solution to Adder

Write your solution here

module top_module(

input [99:0] a, b,

input cin,

output cout,

output [99:0] sum );

assign {cout, sum} = a + b + cin;

endmodule网页答案:

module top_module (

input [99:0] a,

input [99:0] b,

input cin,

output cout,

output [99:0] sum

);

// The concatenation {cout, sum} is a 101-bit vector.

assign {cout, sum} = a+b+cin;

endmoduleBcdadd4

You are provided with a BCD (binary-coded decimal) one-digit adder named bcd_fadd that adds two BCD digits and carry-in, and produces a sum and carry-out.

module bcd_fadd (

input [3:0] a,

input [3:0] b,

input cin,

output cout,

output [3:0] sum );

Instantiate 4 copies of bcd_fadd to create a 4-digit BCD ripple-carry adder. Your adder should add two 4-digit BCD numbers (packed into 16-bit vectors) and a carry-in to produce a 4-digit sum and carry out.

Module Declaration

module top_module (

input [15:0] a, b,

input cin,

output cout,

output [15:0] sum );

Hint...

- The BCD representation for the 5-digit decimal number 12345 is 20'h12345. This is not the same as 14'd12345 (which is 14'h3039).

- The circuit is structured just like a binary ripple-carry adder, except the adders are base-10 rather than base-2.

Write your solution here

module top_module (

input [15:0] a, b,

input cin,

output cout,

output [15:0] sum );

wire [2:0]t;

bcd_fadd add1(a[3:0], b[3:0], cin, t[0], sum[3:0]);

bcd_fadd add2(a[7:4], b[7:4], t[0], t[1], sum[7:4]);

bcd_fadd add3(a[11:8], b[11:8], t[1], t[2], sum[11:8]);

bcd_fadd add4(a[15:12], b[15:12], t[2], cout, sum[15:12]);

endmodule

159

159

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?