写在前面:本章主要内容为理解七点数码管显示的概念,并使用 Verilog 实现。生成输入信号后通过仿真确认各门的动作,通过 FPGA 检查在 Verilog 中实现的电路的操作。

Ⅰ. 前置知识

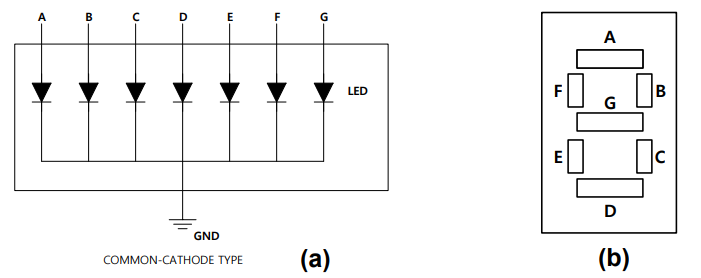

七段数码管是利用多重输出功能的非常有用的元件。该元件用于字符化,如十进制、十六进制数等。适当配置 7 个 元件,如图(a)所示,在每个端子上施加电压(logic "1"),使其发光,从而呈现字形(图b)。

数码管的一种是半导体发光器件,数码管可分为七段数码管和八段数码管,区别在于八段数码管比七段数码管多一个用于显示小数点的发光二极管单元 (decimal point)。

七段数码管的工作原理

多个发光二极管封装在一起的七

订阅专栏 解锁全文

订阅专栏 解锁全文

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?