DDS与并行DAC与ADC

实验目标:

1、掌握并行DAC、ADC的接口时序2、用DDS合成信号,经过DAC输出

3、用ADC采集信号 4、使用SignalTAP在时域观察信号 5、使用Matlab在频域观察信号。

第一部分:

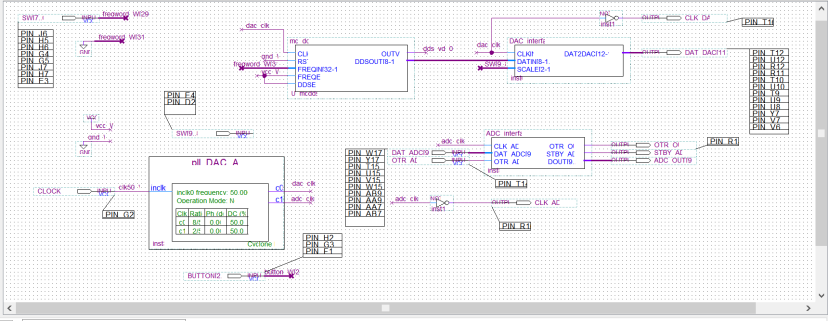

BDF文件

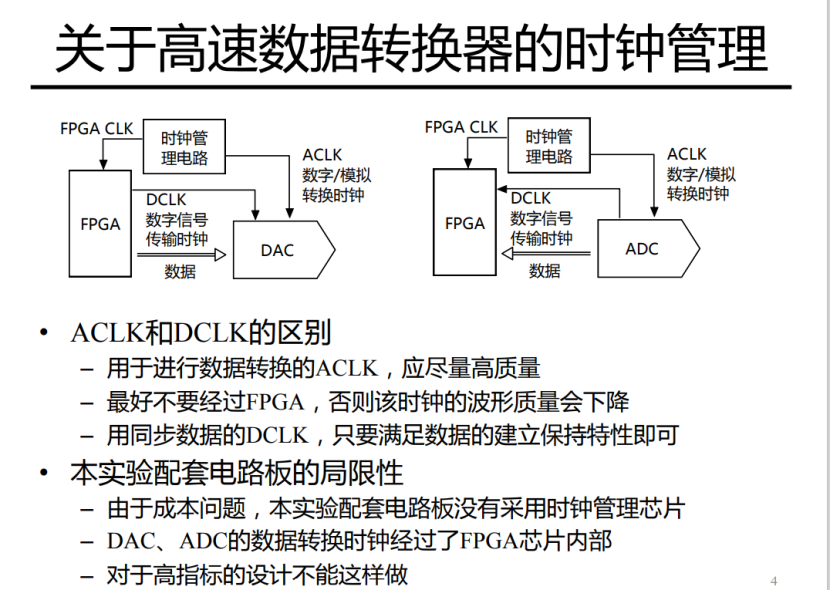

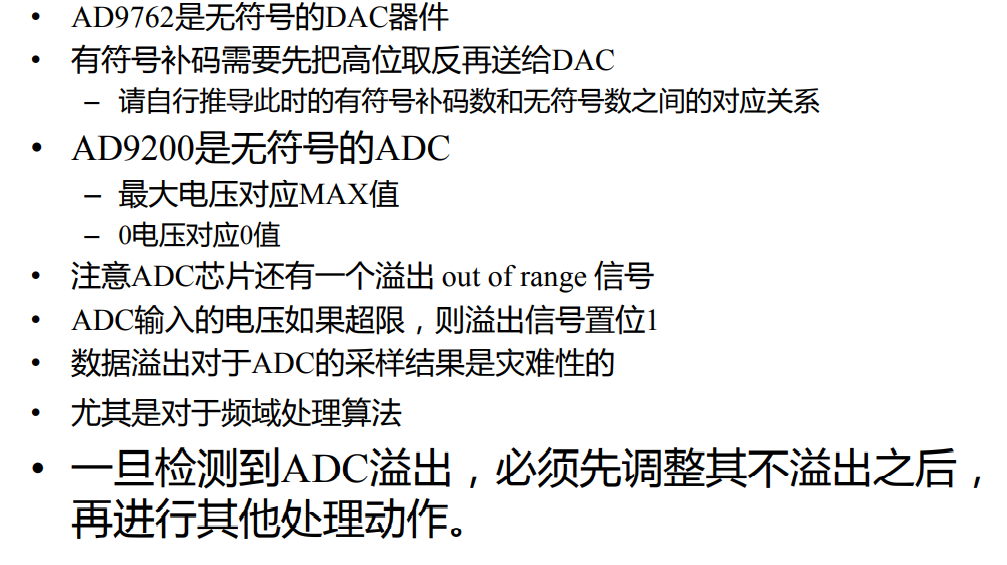

1.该设计由一个PLL从50MHz晶振生成80MHz的DAC时钟、20MHz的ADC时钟

2.一个单周期的DDS生成补码正弦波转成无符号后送至DAC,

3.拨码开关SW9、SW8用于控制DAC的输出幅度,其余的SW开关用于控制DDS频率字

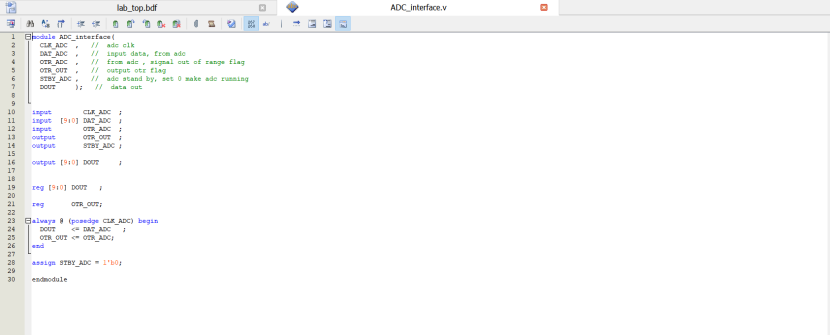

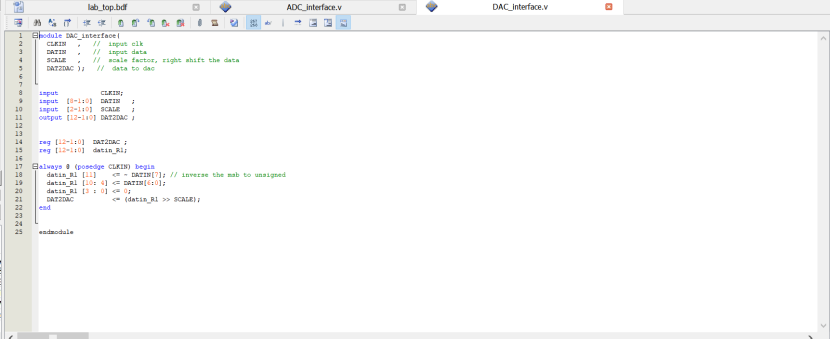

相关模块代码:

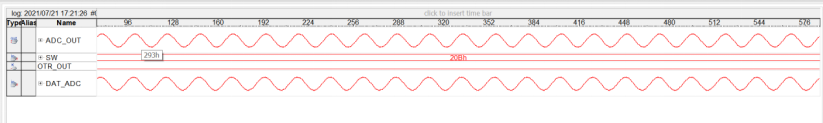

signalTap:

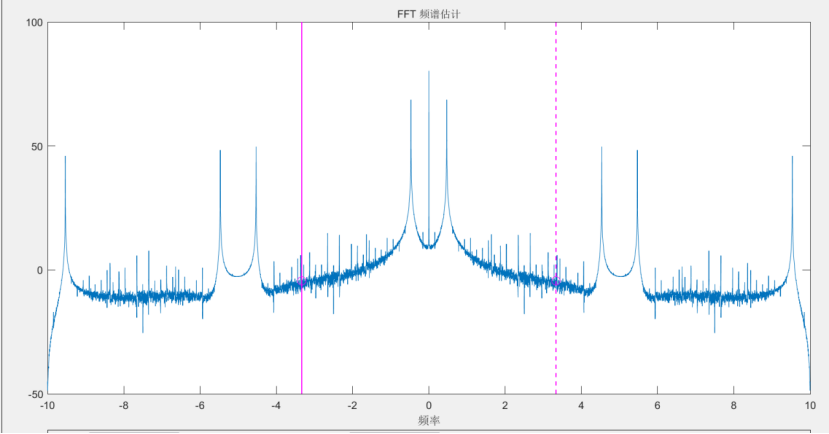

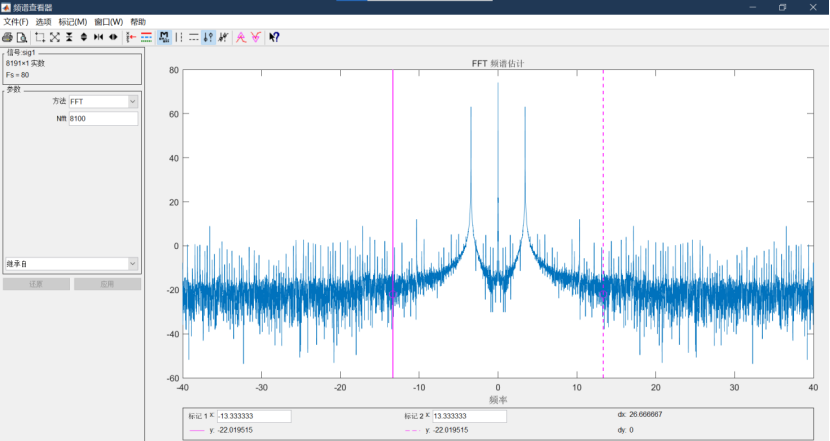

MATLAB频谱分析:

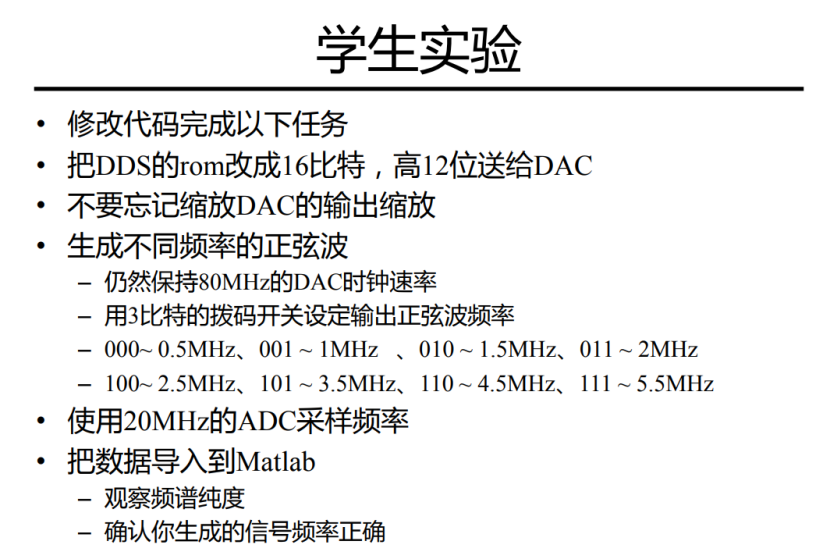

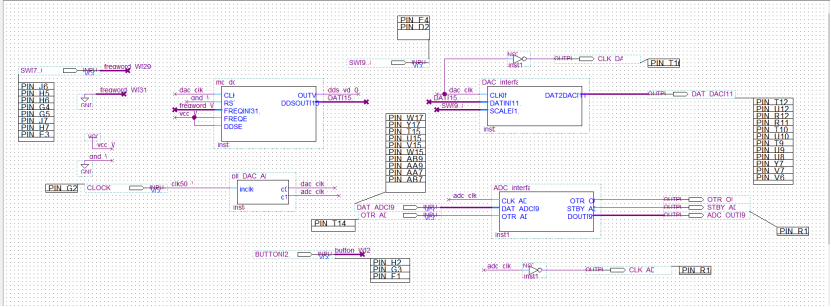

第二部分:

BDF

部分修改后代码:

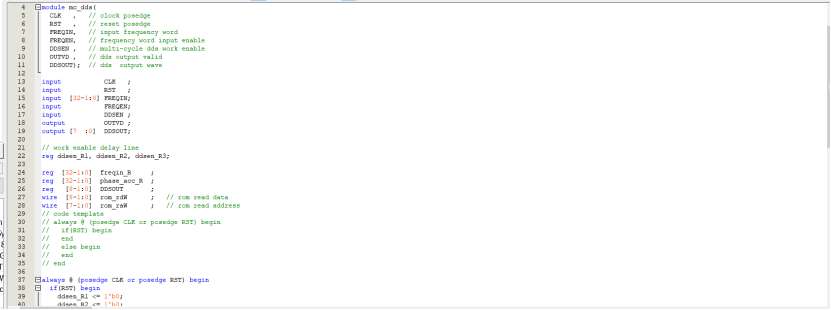

DDS模块

module mc_dds(

CLK , // clock posedge

RST , // reset posedge

FREQIN, // input frequency word

FREQEN, // frequency word input enable

DDSEN , // multi-cycle dds work enable

OUTVD , // dds output valid

DDSOUT); // dds output wave

input CLK ;

input RST ;

input [32-1:0] FREQIN;

input FREQEN;

input DDSEN ;

output OUTVD ;

output [16-1<

本文详细介绍了使用DDS合成信号并通过并行DAC输出,同时利用ADC进行信号采集。实验中,从50MHz晶振生成80MHz DAC时钟和20MHz ADC时钟,并通过SignalTAP时域观察及MATLAB频域分析信号。内容涵盖了DDS频率字控制、DAC输出幅度调节以及针对不同拨码开关状态的信号分析。

本文详细介绍了使用DDS合成信号并通过并行DAC输出,同时利用ADC进行信号采集。实验中,从50MHz晶振生成80MHz DAC时钟和20MHz ADC时钟,并通过SignalTAP时域观察及MATLAB频域分析信号。内容涵盖了DDS频率字控制、DAC输出幅度调节以及针对不同拨码开关状态的信号分析。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3825

3825

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?