实验一:项目创建,编译下载

实验内容:–用1个拨码开关控制所有的LED灯亮灭

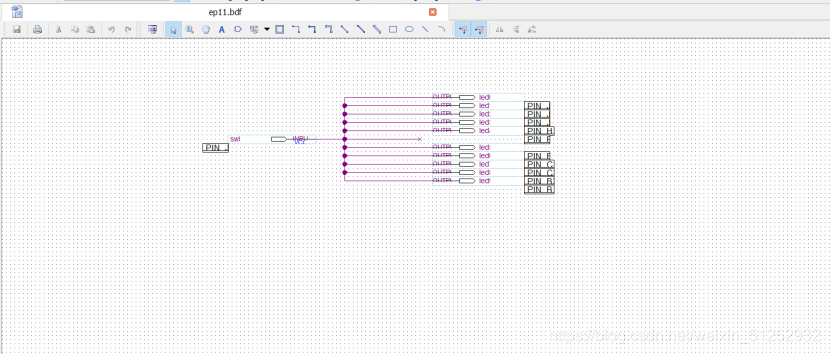

BDF文件

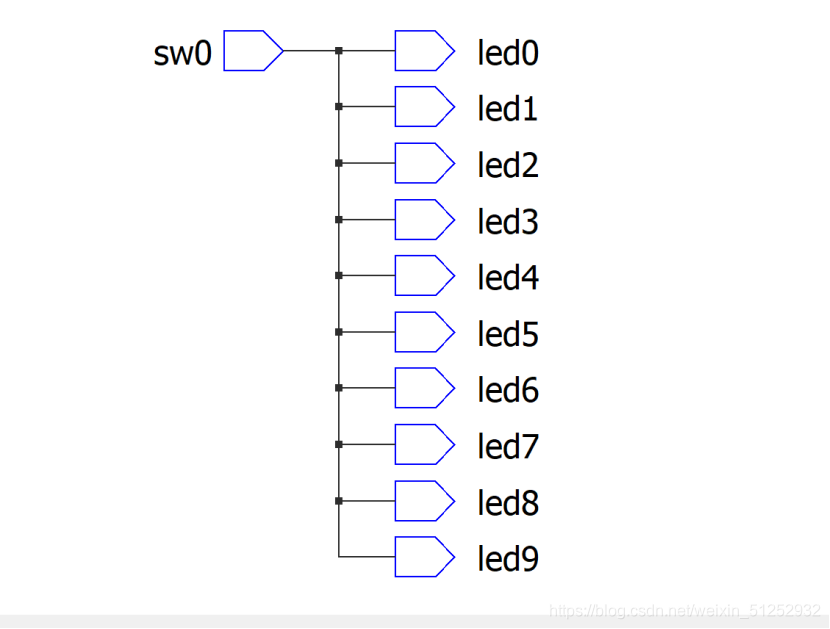

RTL

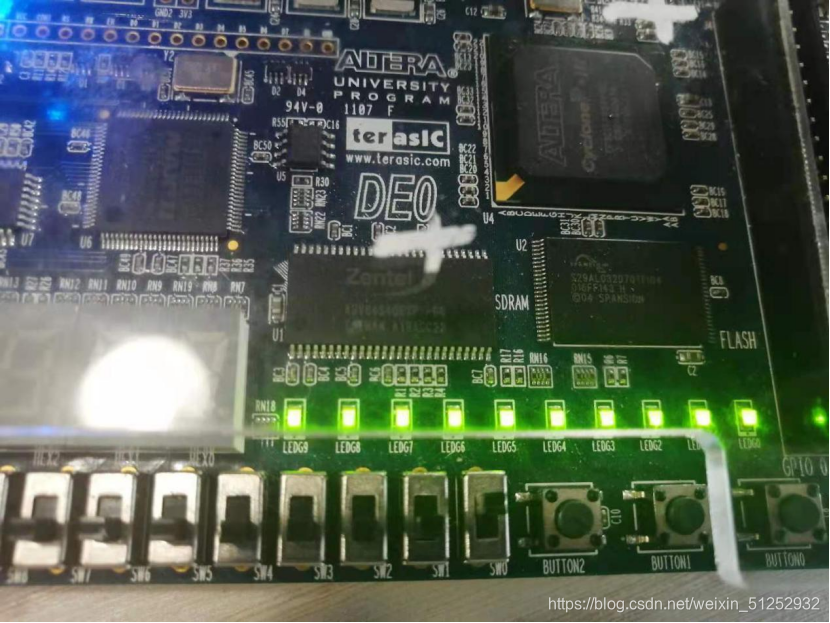

硬件编译仿真:

当按下sw0时,小灯全部亮起

实验二:FPGA译码器组合逻辑

实验内容:

• 1、放置2个2-4译码器模块,则总共有2组SW,每组2个,2组LED,每组4个,每组SW分别控制其对应的LED组。 •

2、参照代码,设计一个3-8译码器,完成类似的拨码开关实验。注意代码中的信号宽度设定。 •

3、自行查阅手册中的7段译码器管脚对应关系,用4个拨码开关控制一个7段译码器的数字,从0-9-A-F,共16个数字和字母。

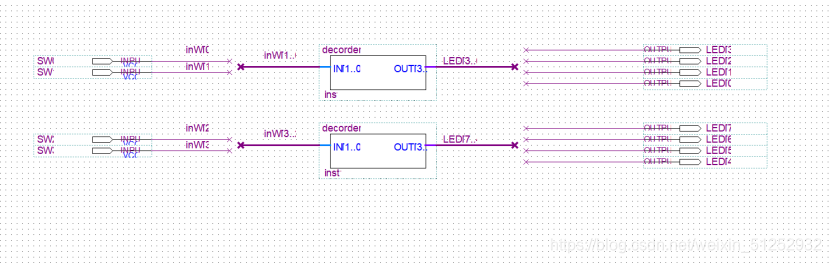

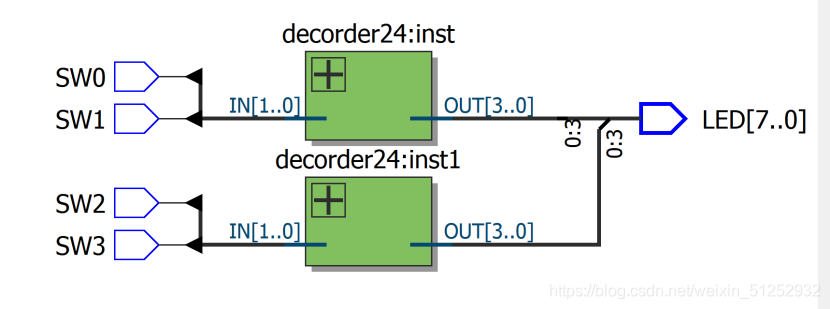

1.放置两个2-4译码器模块

BDF

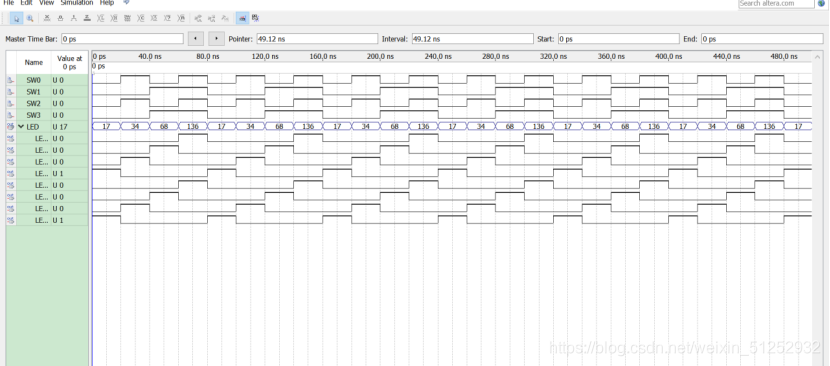

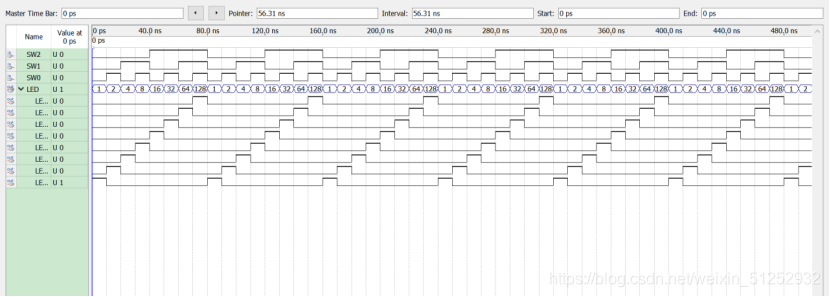

波形仿真

RTL

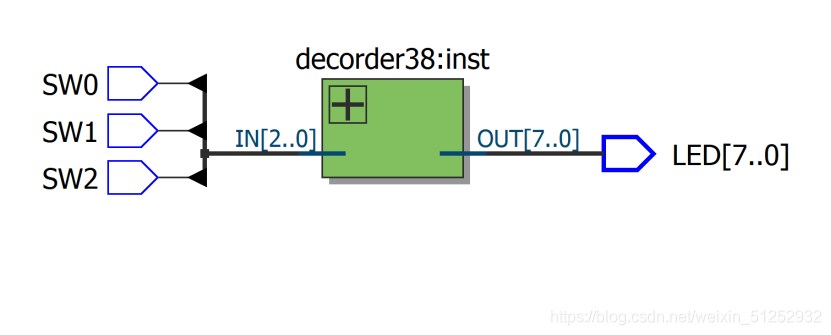

- 3-8译码器

RTL

BDF

波形仿真

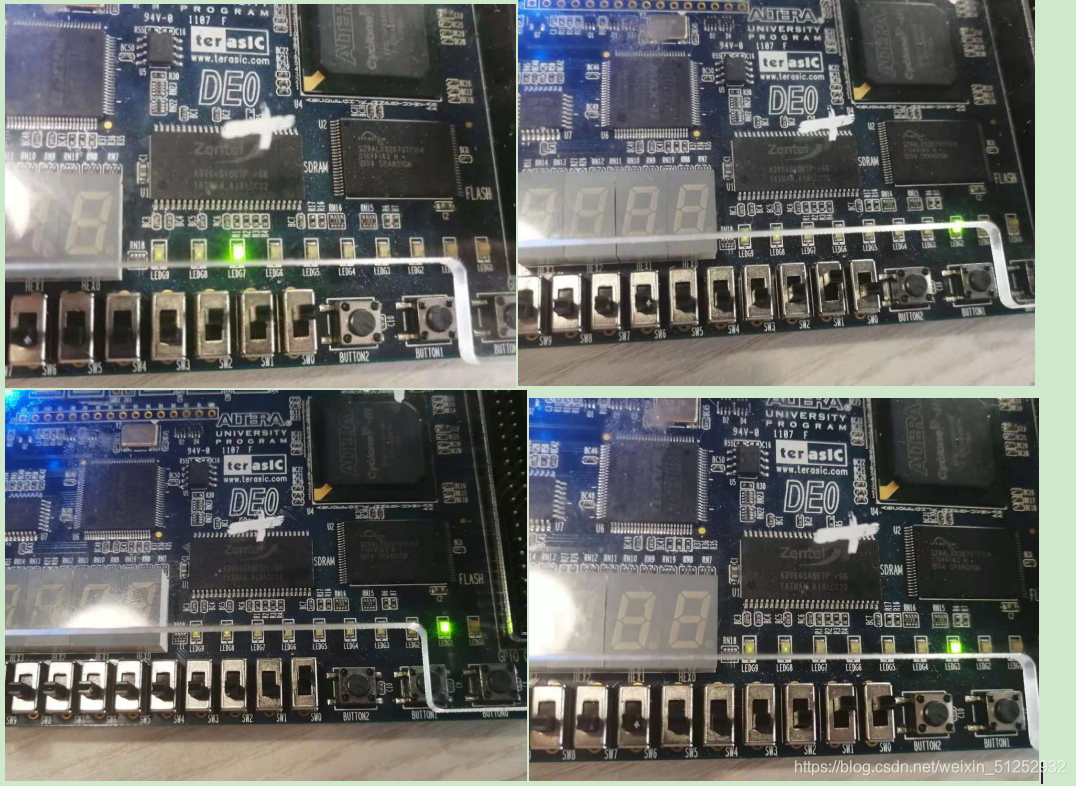

硬件仿真验证:

1.当sw0,sw1,sw2均为1时,LED7亮,其余灯灭。(111)

2.当sw0,sw2为0,sw1为1时,LED2亮,其余灯灭。(010)

3.当sw1,sw2为0,sw0为1时,LED1亮,其余灯灭。(001)

4.当sw2为0,sw1,sw0为1时,LED3亮,其余灯灭。(011)

3.用4个拨码开关控制一个7段译码器的数字

代码

module decorder14(

IN , // input

OUT ); // output

input [3:0] IN;

output[7:0] OUT;

reg [7:0] OUT;

// get the OUT

always @ (IN) begin

case(IN)

4'b0000: OUT = 8'b11000000; //0

4'b0001: OUT = 8'b11111001; //1

4'b0010: OUT = 8'b10100100; //2

4'b0011: OUT = 8'b10110000; //3

4'b0100: OUT = 8'b10011001; //4

4'b0101: OUT = 8'b10010010; //5

4'b0110: OUT = 8'b10000010; //6

4'b0111: OUT = 8'b11111000; //7

4'b1000: OUT = 8'b10000000; //8

4'b1001: OUT = 8'b10010000; //9

4'b1010: OUT = 8'b00001000; //A

4'b1011: OUT = 8'b00000000; //B

4'b1100: OUT = 8'b01000110; //C

4'b1101: OUT = 8'b01000000; //D

4'b1110: OUT = 8'b00000110; //E

4'b1111: OUT = 8'b00001110; //F

// full case 不需要写default,否则一定要有default

endcase

end

endmodule

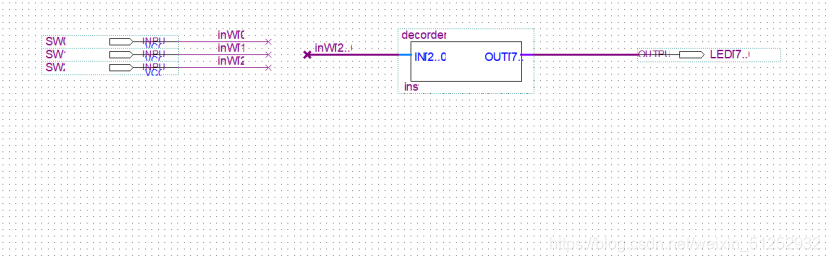

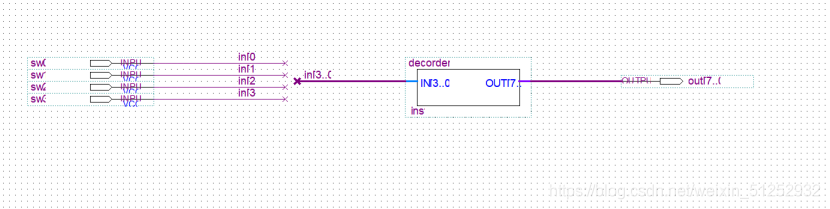

BDF

RTL

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3316

3316

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?