本节重点介绍DRAM的基本array存储结构。

1966年,罗伯特·登纳德在IBM发明了DRAM,它的工作原理与其他类型的内存大不相同。DRAM中的基本存储单元由两个元件组成:晶体管和电容器。

- MOSFET(场效应管)是作为切换(选择)开关

- 电容存储数据/传输设备的bit位信息

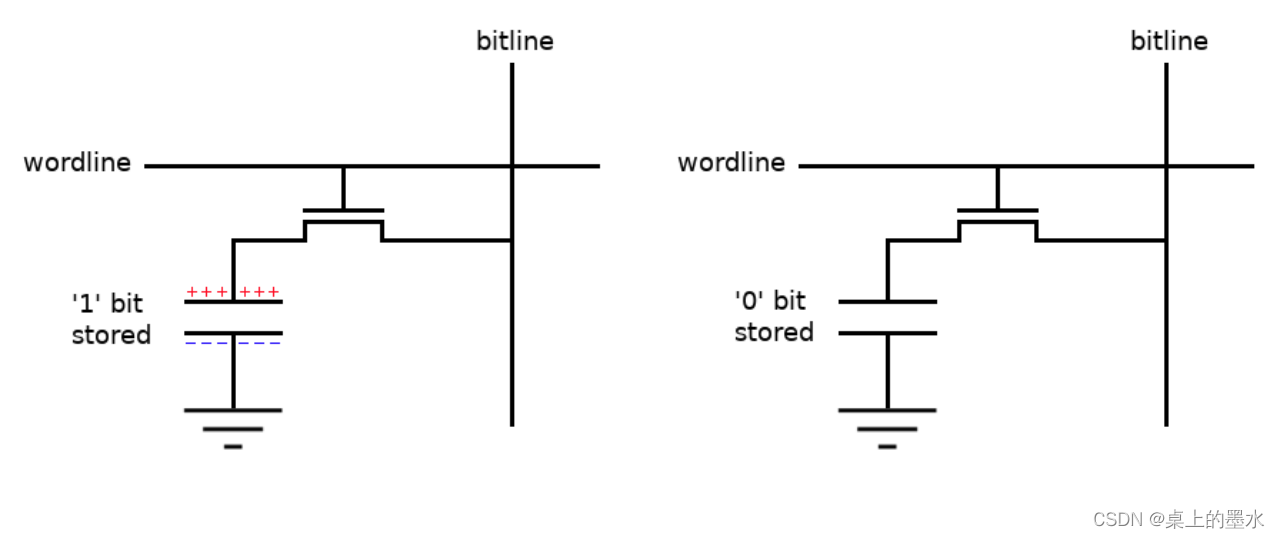

Cell的电容上的电荷水平决定了该特定位是逻辑上的“1”还是“0”-电容中电荷的存在表示逻辑上的“1”,电荷的缺失表示逻辑上的“0”。

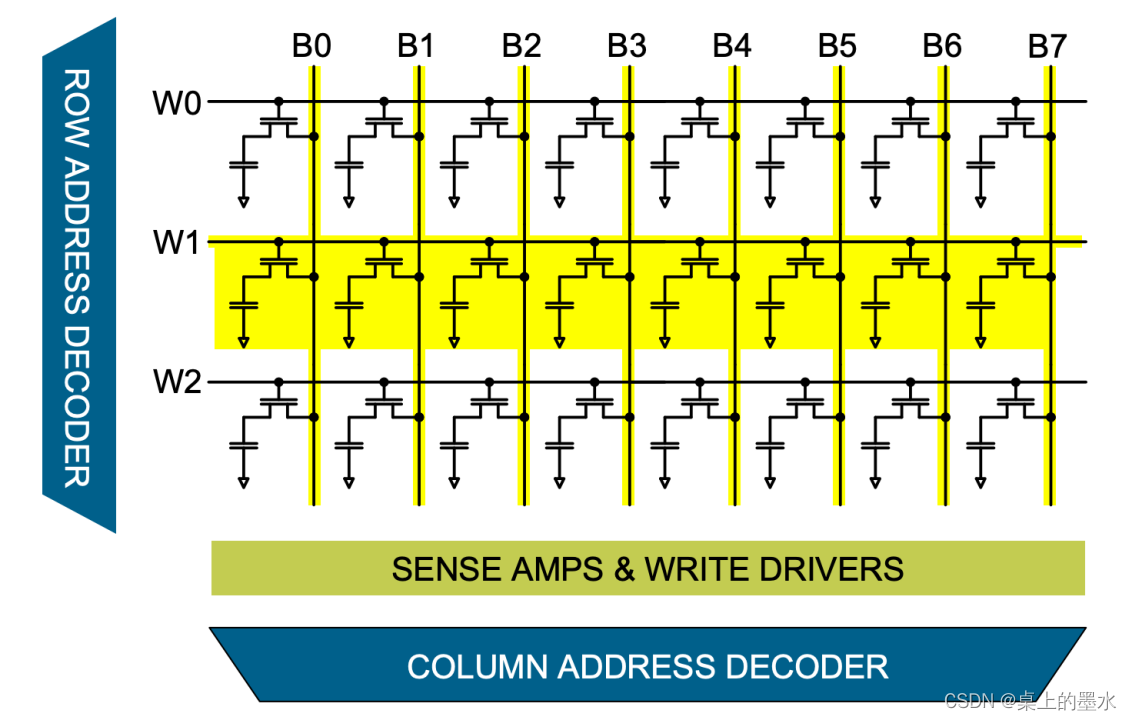

当需要在存储器中放入比特时,晶体管用来对电容器进行充放电。充电电容代表逻辑高电平,即“1”,而放电电容代表逻辑低电平,即“0”。充电/放电通过字行和位行完成,如图1所示。因为漏电流的存在,DRAM单元必须refresh(自刷新),而且功耗要比SRAM大。

早期的DRAM的基本结构是3T1C(3transistor,1capacitor)。使用3个晶体管作为开关: 优点是读操作不会破坏cell的信息。当读取cell电容的位信息时,不会影响电容的电荷,从而读后不需要对cell进行precharge。但1T1C比3T1C结构面积节省很多,现代DRAM还是常用1T1C.

- 读写操作的方式:2种line

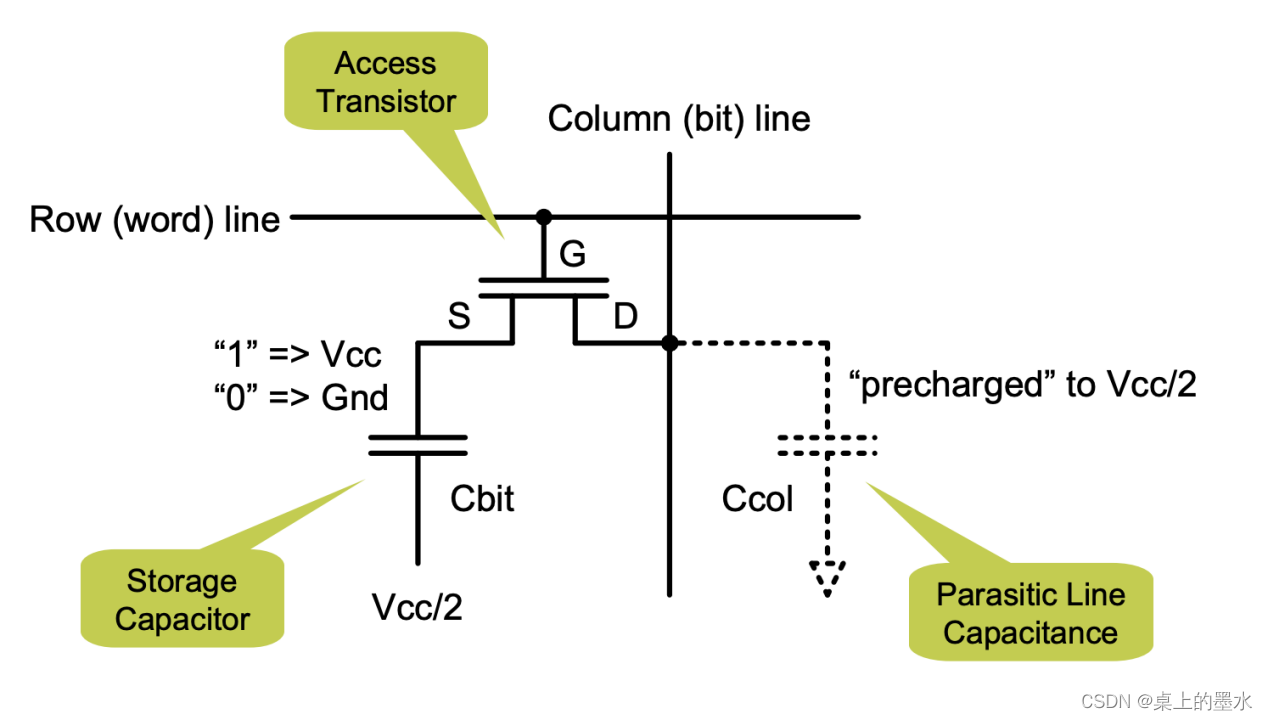

每个DRAM cell 都要有字线(WL)和位线(BL),连接如图1所示,以便矩阵中所需的cell单元可以读取或写入数据。

为了提高读写能力和速度,可以将整个DRAM拆分为子阵列。多个子阵列的存在缩短了WL和BL,减少了访问单个Cell的时间。例如一个256M DRAM, 可以被分割成16个较小的16M阵列Array。

WL(world line) 控制选通(MOSFET的门极),而BL(bit line)连接MOSFET的漏极,并最终连接到感测放大器(sense amplifiers)。

从逻辑上简单理解:WL 是选通该行; BL 是把该列的bit 存储成“1”或者“0 ”的数据。

图1 - 位信息的存储方式:电容上有无电荷

图2 - cell的基本结构

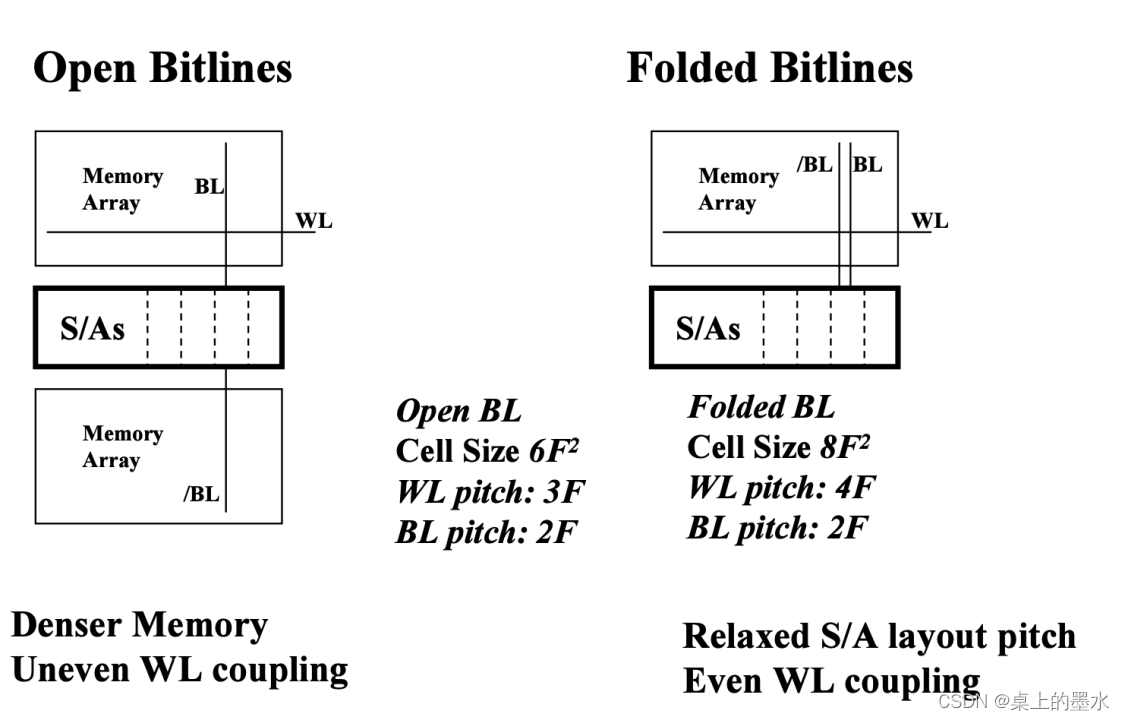

BL有两种组织方式:

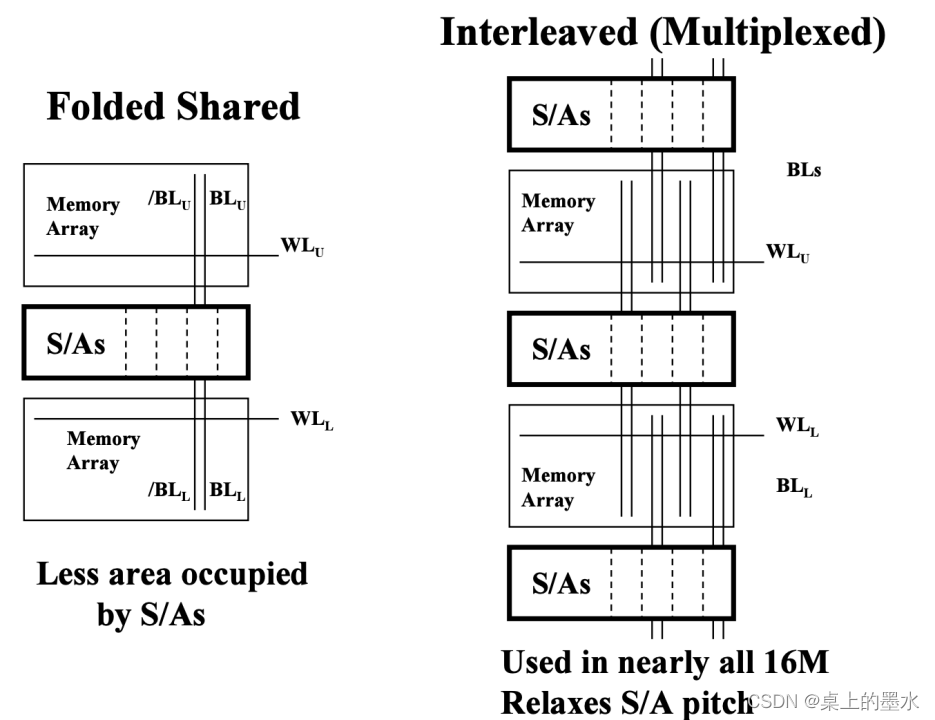

折叠位线(Folder Bitline): 将1个Array的2个相邻的 BL连接到共享感测放大器。差分比较器的2个输入来自同1个array。这种格式提供了额外的抗噪声能力,但代价是不够紧凑,面积大。

开放位线(Open Bitline): 每个Array中的1个BL连接到sense amplifer。差分比较器的2个输入来自2个不同array。这提供了一个更紧凑的解决方案,面积小但代价是抗噪声能力差。

图3 - Bitlines的2种方式

图4 - Folder line方式的2种结构

现代DRAM大部分采用folder方式。随着工艺的发展,open方式的抗干扰性也越来越好。

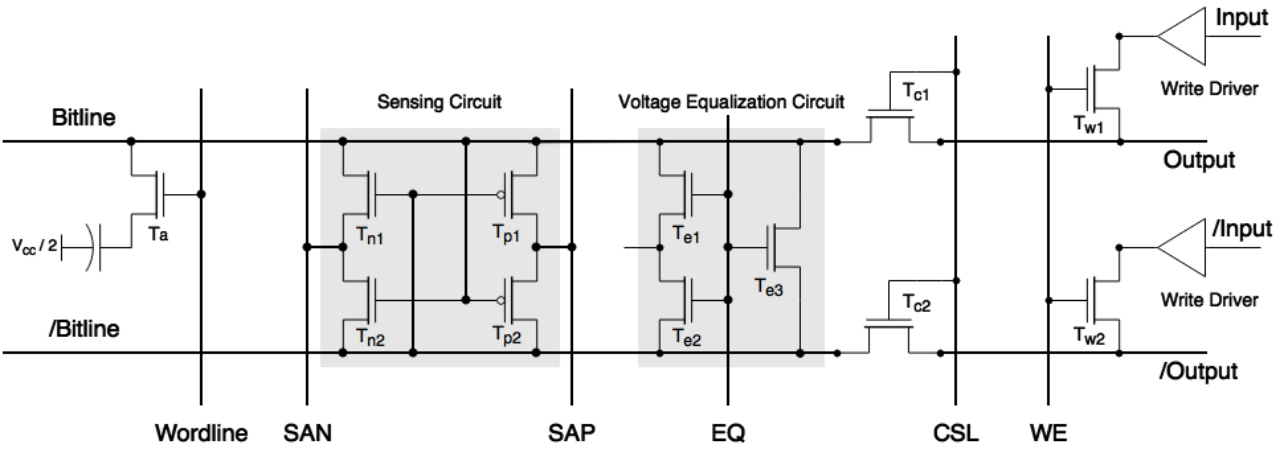

Storage Capacitor 的 Common 端接在 Vcc/2。

当 Storage Capacitor 存储的信息为 1 时,另一端电压为 Vcc,此时其所存储的电荷

Q = +Vcc/2 / C

当 Storage Capacitor 存储的信息为 0 时,另一端电压为 0,此时其所存储的电荷

Q = -Vcc/2 / C

2.Array阵列的结构:

图5 - array的结构图

2.1.数据读写原理

从上面的结构图上分析,我们可以很容易的推测出 DRAM Storage Cell 的数据读写流程:

- 读数据时,Wordline 设为逻辑高电平,打开 Access Transistor,然后读取 Bitline 上的状态

- 写数据时,先把要写入的电平状态设定到 Bitline 上,然后打开 Access Transistor,通过 Bitline 改变 Storage Capacitor 内部的状态。

2.2.遇到问题:电荷量不匹配

然而,在具体实现上,如果按照上面的流程对 DRAM Storage Cell 进行读写,会遇到以下的问题:

1.外界的逻辑电平与 Storage Capacitor 的电平不匹配,由于 Bitline 的电容值(如图2的寄生电容)比 Storage Capacitor 要大的多(通常为 10 倍以上),当 Access Transistor 导通后,如果 Storage Capacitor 存储的信息为 1 时,Bitline 电压变化非常小。外界电路无法直接通过 Bitline 来读取 Storage Capacitor 所存储的信息。

2.进行一次读取操作后,Storage Capacitor 存储的电荷会变化。在进行一次读取操作的过程中,Access Transistor 导通后,由于 Bitline 和 Storage Capacitor 端的电压不一致,会导致 Storage Capacitor 中存储的电荷量被改变。最终可能会导致在下一次读取操作过程中,无法正确的判断 Storage Capacitor 内存储的信息。

3.由于 Capacitor 的物理特性,即使不进行读写操作,其所存储的电荷都会慢慢变少。这个特性要求 DRAM 在没有读写操作时,也要主动对 Storage Capacitor 进行电荷恢复的操作。

2.3. 解决问题:Differential Sense Amplifier

为解决上述的问题,DRAM 在设计上,引入了 Differential Sense Amplifier。

Differential Sense Amplifier 包含 Sensing Circuit 和 Voltage Equalization Circuit 两个主要部分。它主要的功能就是将 Storage Capacitor 存储的信息转换为逻辑 1 或者 0 所对应的电压,并且呈现到 Bitline 上。同时,在完成一次读取操作后,通过 Bitline 将 Storage Capacitor 中的电荷恢复到读取之前的状态。

2.3.1差分感应放大器sense amplifierg功能

- 将bitline上的微小电压变化放大,并转化成数字信号

- 将被读的bit位所在的那一行基本单元cell的值重新存入cell(刷新),因为在transistor打开时,存储在存储电容中的电荷将于bitline共享了(内存cell行bit信息读取的物理本质是并联分流),存储在存储电容中的电荷变少了,因此需要将值再次存入cell(无论该bit是否被读,只要是同一行的都需要进行该步操作)

- 临时存储器的作用,临时存储bitline上的值 。

当row选通后,该bank的sense amplifier缓存这行的内容。

在后面的小节中,我们通过完整的数据读取和写入过程,来了解 Differential Sense Amplifier 工作原理。

参考连接:

本文深入介绍了DRAM的基本存储单元结构,包括电容存储数据的原理,以及读写操作中遇到的电荷量不匹配问题。针对此问题,文章详细阐述了差分感应放大器(Differential Sense Amplifier)的角色,如何放大微小电压变化并恢复存储单元的电荷。此外,还探讨了DRAM阵列的组织方式,如折叠位线和开放位线的不同优缺点。

本文深入介绍了DRAM的基本存储单元结构,包括电容存储数据的原理,以及读写操作中遇到的电荷量不匹配问题。针对此问题,文章详细阐述了差分感应放大器(Differential Sense Amplifier)的角色,如何放大微小电压变化并恢复存储单元的电荷。此外,还探讨了DRAM阵列的组织方式,如折叠位线和开放位线的不同优缺点。

1115

1115

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?