1、问题的提出

超高设计时,很多人的关注点是最大超高取值多少,超高渐变从什么地方开始,是否能进入直线段等等,但就超高渐变段的计算取值等问题,却很少人关注,本文将带你一同进行探讨。

2、超高渐变段计算中存在的争议

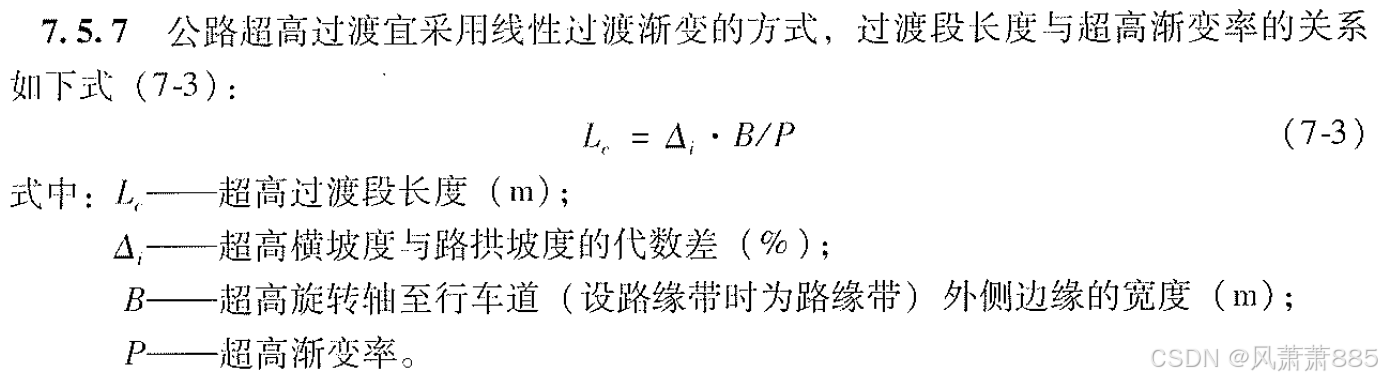

1)关于超高渐变段,《公路路线设计规范》(JTG D20-2017)的条文解释中,有如下规定:

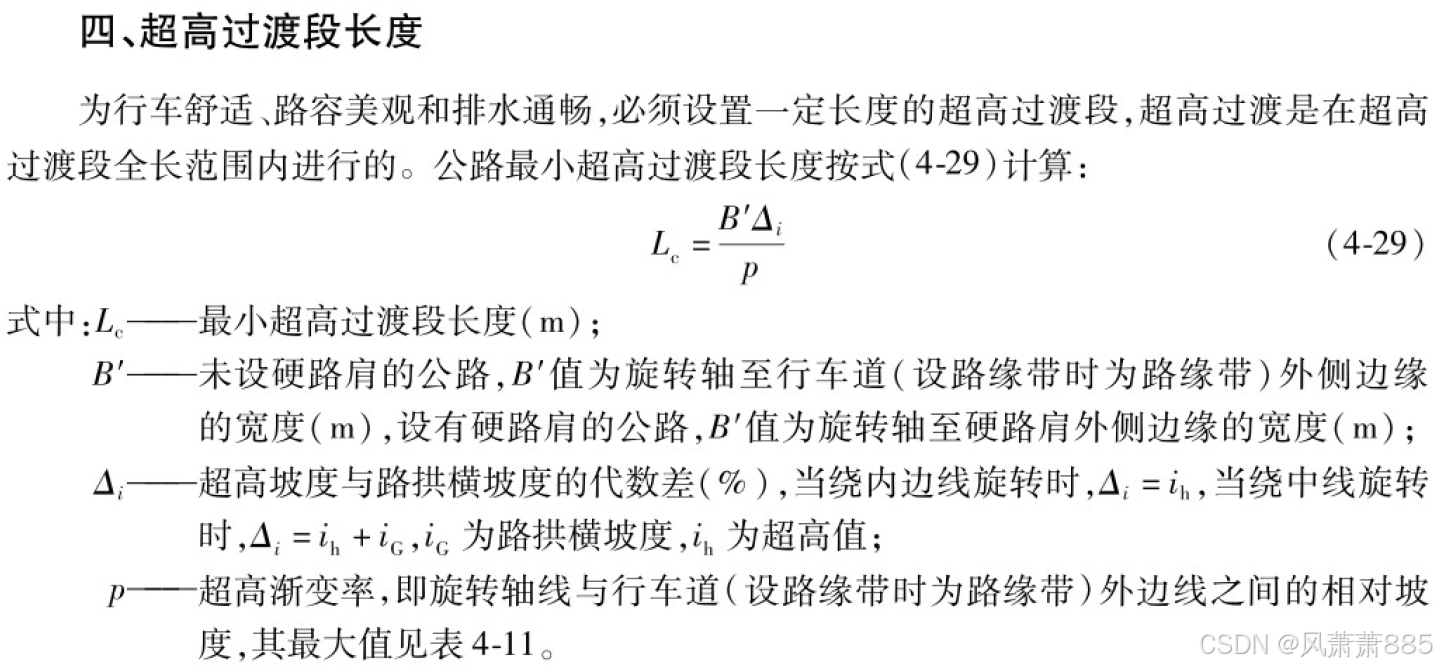

2)在道路勘测设计教材中(以人民交通出版社第五版为例),关于超高过渡段的长度计算,描述如下:

从上面的对比中,我们可以看出,主要区别在于Δi的取值问题,在道路勘测设计教材中,做了更为具体的规定,即当绕内边线旋转时,Δi=ih,当绕中线旋转时,Δi=ih+iG。

有无这个备注,对于绕中线旋转时,没有什么差别,但对于绕内边线旋转时,则存在一定的差异。

3)举例

一条二级公路,设计车速60km/h,双向两车道,车道宽3.5m,右侧硬路肩0.75m,一般路段路拱横坡2%,超高段横坡4%,要计算所需的最小超高渐变段长度。

(1)按公路路线设计规范

当绕内边线旋转时,P取1/100,Lc=(0.75+3.5+3.5+0.75)*(0.04+0.02)/P=51m

当绕中心线旋转时,P取1/150,Lc=(0.75+3.5)*(0.04+0.02)/P=38.25m

(2)按道路勘测设计教材

当绕内边线旋转时,P取1/100,Lc=(0.75+3.5+3.5+0.75)*(0.04)/P=34m

当绕中心线旋转时,P取1/150,Lc=(0.75+3.5)*(0.04+0.02)/P=38.25m

可以看出,当绕内边线旋转时,两种方法计算出来的分别是51m和34m,相差还是比较大,那么,究竟应该采用那种计算方法呢?

3、超高渐变段相关计算推导

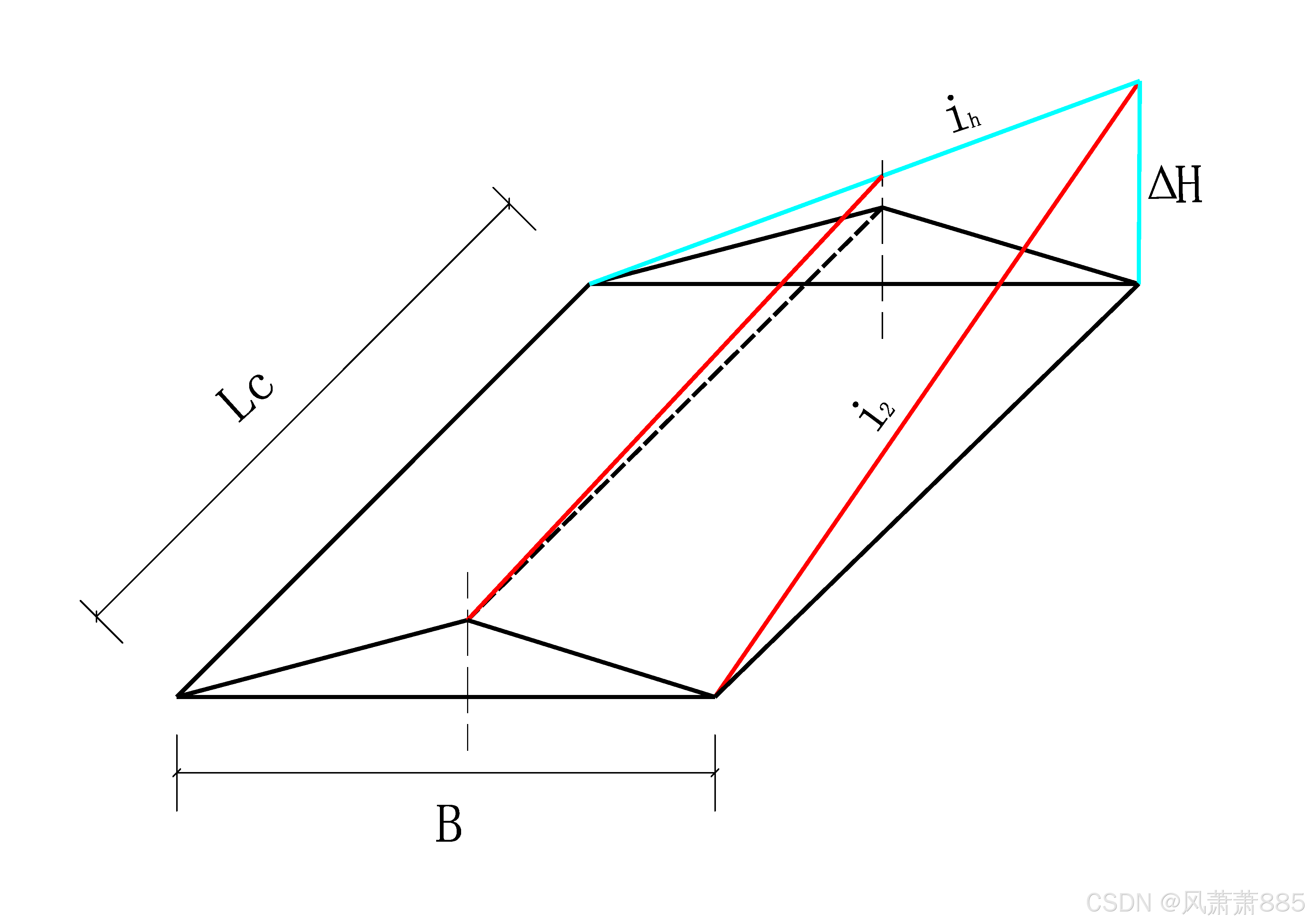

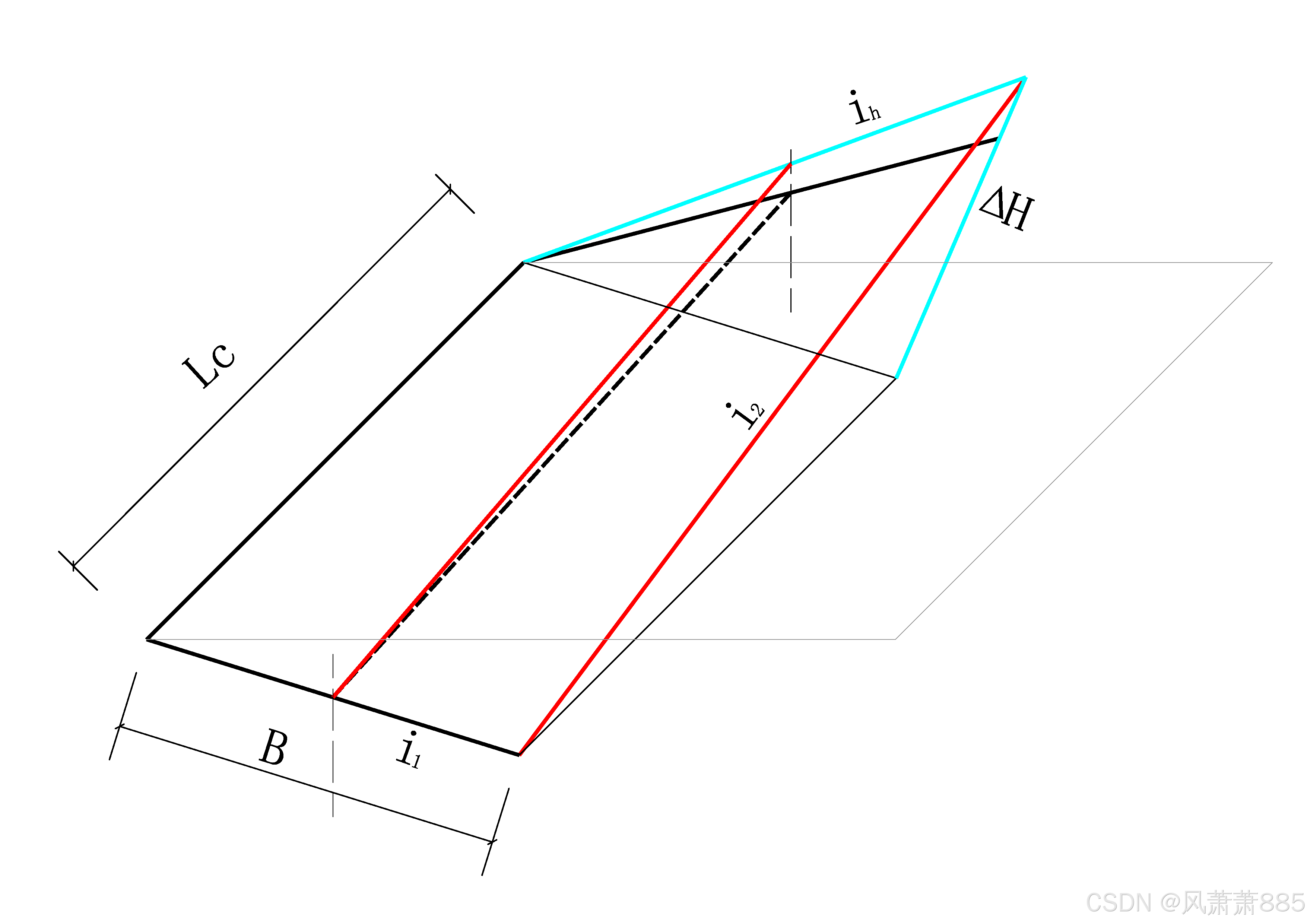

1)绕内边线旋转

i2=ΔH/Lc=B*ih/Lc

从而得出:Lc=B*ih/i2=B*ih/P

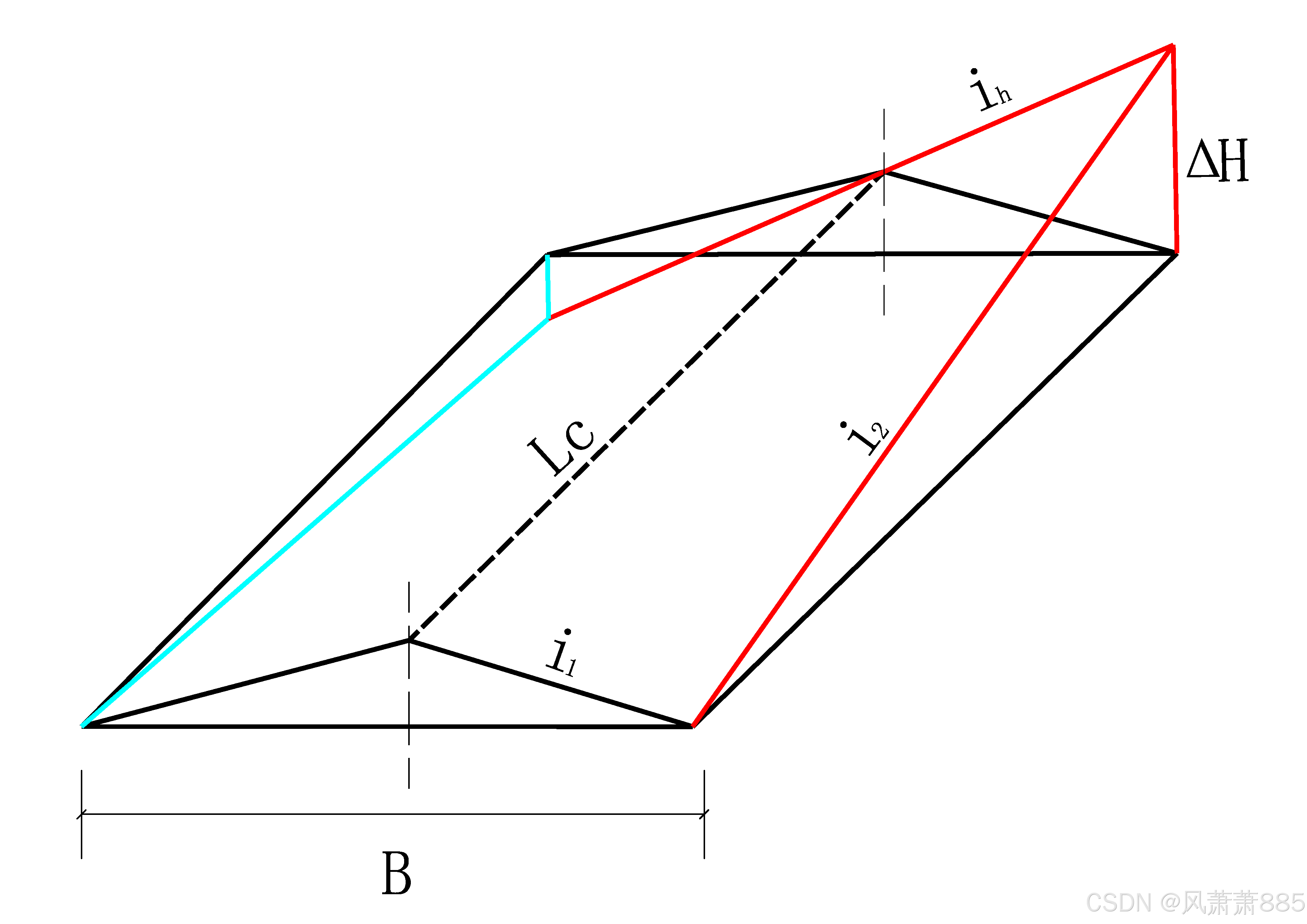

2)绕中心线旋转

i2=ΔH/Lc=0.5*B*(i1+ih)/Lc

推导得出:Lc=0.5*B*(i1+ih)/i2=0.5*B*(i1+ih)/P

从以上公式中,可以看出,结论与道路勘测设计教材中的内容吻合。是不是就说明,以后在超高计算时,当绕边线旋转时,Δi就取超高横坡ih呢?

实际上,上述公式推导时,我们采用的是无中央分隔带的道路作为例子,当有中央分隔带时,会不会有所不同呢?

3)有中央分隔带时

当有中央分隔带时,如果采用绕道路中心线旋转,这个时候和无中央分隔带时是一样的,唯一的区别是B值中需包含中分带宽度,这里不再赘述,而当采用绕分隔带边线旋转时,图示如下:

i2=ΔH/Lc=B*(i1+ih)/Lc

推导得出:Lc=B*(i1+ih)/i2=B*(i1+ih)/P

注意,这里的B是半幅车道宽度。

4)小结

对于无中央分隔带道路而言,道路勘测设计中的说法是正确的,即当绕内边线旋转时,Δi=ih,当绕中线旋转时,Δi=ih+iG;而当有中央分隔带时,不管是绕中线线旋转还是绕分隔带边线旋转,Δi=ih+iG。

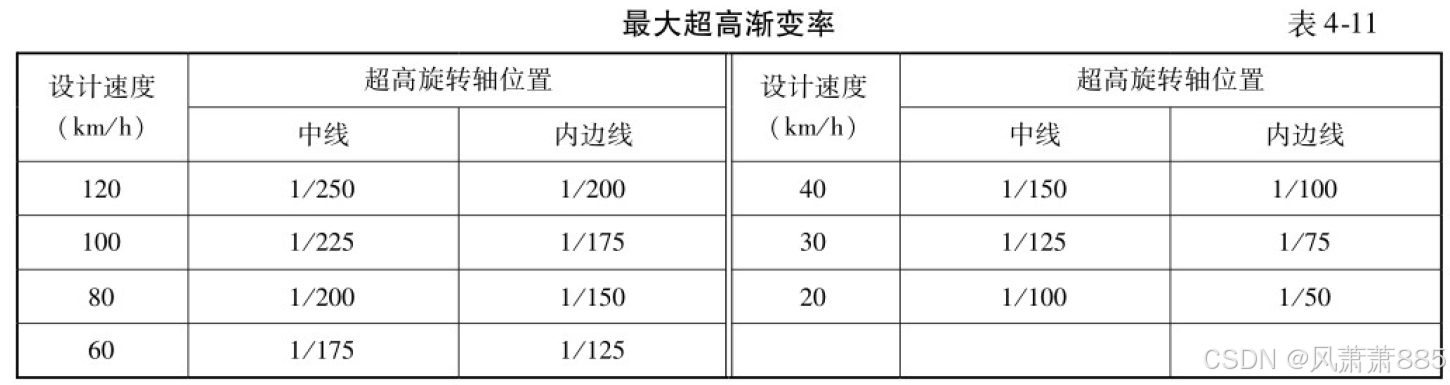

4、最大超高渐变率旋转轴位置的选取

最大超高渐变率取值分为2种情况,分别是绕中线旋转和绕边线旋转。

对于无中央分隔带时的情形,最大超高渐变率取值没有争议,但对于有中央分隔带,且绕中央分隔带边线旋转时,最大超高渐变率是取中线还是边线,规范上没有明确的说法,存在一定的争议,接下来我们来做个推导:

假设半幅中央分隔带宽b1,半幅车行道宽b2;

当采用绕中心线旋转时,Lc1=(b1+b2)*(ih+iG)/P1

P1为绕中心线旋转的超高渐变率。

当采用绕分隔带边线旋转时,Lc2=b2*(ih+iG)/P2

P2为绕分隔带边线旋转时的超高渐变率。

当半幅分隔带宽度b1=0时,绕中心线旋转和绕分隔带旋转实际上是一回事,那么Lc1=Lc2

则可以得出P2=P1。

因此,当有中央分隔带时,绕分隔带边线旋转时,超高渐变率建议取表格中的中线一栏中的数值。

(Ps:这个结论与部分专家的结论不一致,实际使用时,由于中线一栏的超高渐变率比边线一栏更小,所以同等情况下,采用中线一栏计算得出的超高缓和段长度会更长,只要不会导致超高渐变率小于1/330,就是偏安全的。)

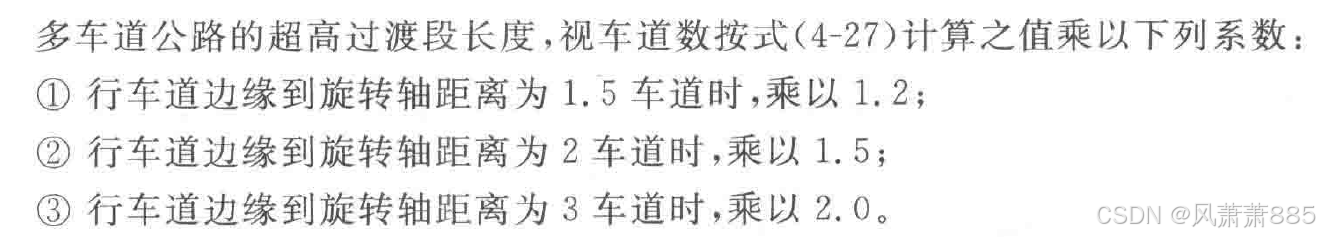

5、是否要考虑多车道修正系数

在一些教材中,如《道路勘测设计》(中国矿业大学出版社),关于超高缓和段,有如下说明:

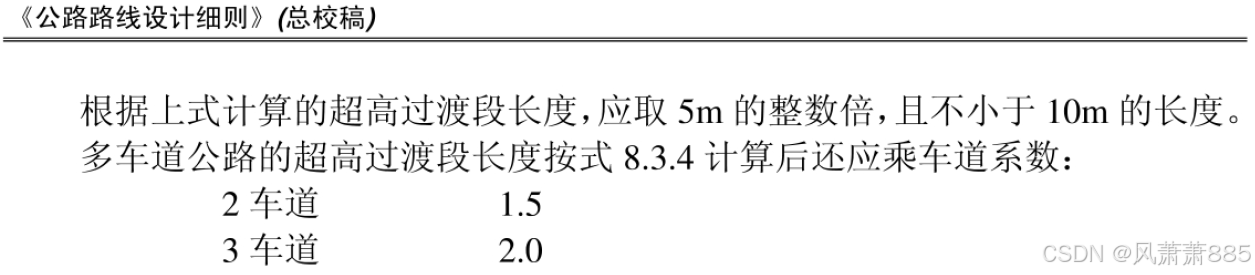

在未正式出版的公路路线设计细则中,也有如下规定:

那么,计算超高缓和段的长度时,是否需要考虑多车道系数呢?

经过溯源,我们可以查出,Lc=Δi*B/P 这个公式是从94版规范中延续下来的,在94版路线设计规范中,条文如下:

该公式特指双车道公路,但在之后的06版规范和17版的规范中,再介绍这个公式时,就不再特指双车道公路了,而实际应用时,对于多车道公路,B值的取值已经考虑了多根车道的情况,如果再考虑多车道系数,会导致超高缓和段较长,在地形困难条件下难以布线,因此,在超高缓和段长度计算时,不用再考虑多车道修正系数。

6、主要结论

1)对于无中央分隔带公路,当绕边线旋转时,超高横坡度与路拱坡度的代数差,取超高值ih;当绕中心线旋转时,超高横坡度与路拱坡度的代数差,取ih+iG。(iG为路拱横坡)

2)对于有中央分隔带公路,不管是绕中央分隔带边线旋转还是绕中心线旋转,超高横坡度与路拱坡度的代数差,均取ih+iG。

3)对于有中央分隔带公路,当绕中央分隔带边线旋转时,最大超高渐变率按照表格中超高旋转轴位置为中线来选取。

4)公式中B值已经考虑了多车道的情况,无需再考虑多车道修正系数。

以上为个人观点,欢迎大家批评指正!

4179

4179

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?