一、设计题目

8位16进制频率计设计

二、设计要求

(1)选择实验电路模式5

(2)设计仿真文件,进行软件验证

(3)用Verilog程序设计方法实现8位16进制频率计设计

(4)通过下载线下载到实验系统上进行硬件测试验证

三、分析过程

频率测量原理及 8 位 16 进制频率计各子模块功能分解:

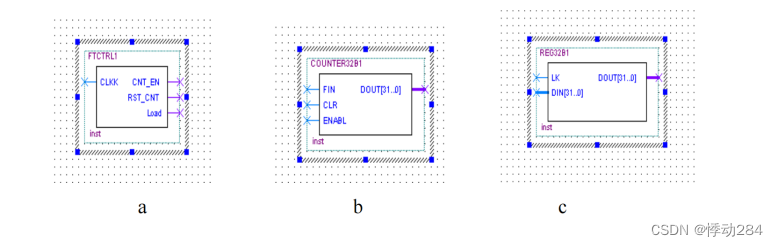

测定信号的频率必须有一个脉宽为 1 秒的输入信号脉冲计数允许的信号;1 秒计数结束后,计数值被锁入锁存器,计数器清0,为下一测频计数周期作好准备。测频控制信号可以由一个独立的发生 器来产生,即图 2-1 中的 FTCTRL1。测频控制模块可以如图 2—1(a)所示。设计要求是:FTCTRL1的计数使能信号 CNT_EN 能产生一个 1 秒脉宽的周期信号,并对频率计中的 32 位二进制计数器 COUNTER32B1(图 2—1 b)的 ENABL 使能端进行同步控制。当 CNT_EN 高电平时允许计数;低电平时 停止计数,并保持其所计的脉冲数。在停止计数期间,首先需要一个锁存信号 LOAD 的上跳沿将计数 器在前 1 秒钟的计数值锁存进锁存器 REG32B1(图 2—1 c)中,并由外部的 16 进制 7 段译码器译出, 显示计数值。设置锁存器的好处是数据显示稳定,不会由于周期性的清 0 信号而不断闪烁。锁存信号后,必须有一清 0 信号 RST_CNT 对计数器进行清零,为下 1 秒的计数操作作准备。根据测频原理,测频控制时序可以如图(图 2—1 d)所示:

要设计一个8位十六进制频率计,我们需要将之前的各个模块结合起来,并添加一些额外的逻辑以实现频率计的功能。频率计的主要功能是测量输入信号的频率,并将结果以8位十六进制显示。

频率计设计思路:

· 控制信号模块(FTCTRL1) - 控制计数器使能、复位和结果锁存。

· 8位计数器模块(COUNTER8B1) - 计数输入信号的周期数。

· 锁存器模块(REG8B1) - 锁存计数结果。

四、仿真程序

//顶层文件

module freqtest1 (

input CLK,

input FSIN,

output [31:0] DOUT

);

wire TSTEN1;

wire CLR_CNT1;

wire LOAD1;

wire [31:0] DTO1;

FTCTRL FTCTRL (

.CLKK(CLK),

.CNT_EN(TSTEN1),

.RST_CNT(CLR_CNT1),

.Load(LOAD1)

);

REG32B REG32B (

.LK(LOAD1),

.DIN(DTO1),

.DOUT(DOUT)

);

COUNTER32B COUNTER32B (

.FIN(FSIN),

.CLR(CLR_CNT1),

.ENABL(TSTEN1),

.DOUT(DTO1)

);

endmodule //32位计数器模块

module COUNTER32B (

input FIN, // 时钟信号

input CLR, // 清零信号

input ENABL, // 使能信号

output reg [31:0] DOUT // 计数输出

);

reg [31:0] CQI;

always @(posedge FIN or posedge CLR) begin

if (CLR)

CQI <= 32'b0; // 清零

else if (ENABL)

CQI <= CQI + 1; // 计数递增

end

always @(*) begin

DOUT = CQI;

end

endmodule // 32位锁存器模块

module REG32B (

input LK,

input [31:0] DIN,

output reg [31:0] DOUT

);

always @(posedge LK) begin

DOUT <= DIN;

end

endmodule// 频率控制电路

module FTCTRL (

input CLKK, // 1Hz 时钟

output wire CNT_EN, // 计数器使能控制

output reg RST_CNT, // 计数器清零

output wire Load // 输出锁存信号

);

reg Div2CLK;

// 分频时钟产生

always @(posedge CLKK)

Div2CLK <= ~Div2CLK; // 1Hz 时钟的2分频

// 清零信号产生

always @( CLKK or Div2CLK) begin

if (CLKK == 1'b0 & Div2CLK == 1'b0)

RST_CNT <= 1'b1; // 产生清零信号

else

RST_CNT <= 1'b0;

end

// Load 和 CNT_EN 信号产生

assign

Load = ~Div2CLK;

assign

CNT_EN = Div2CLK;

endmodule五、仿真结果

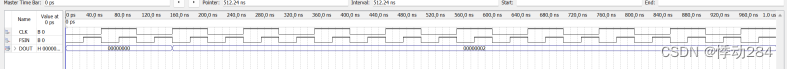

第一次仿真测试:基频信号CLK给10MHZ,待测信号FIN给20MHZ,输出DOUT以十六进制显示,观察波形图

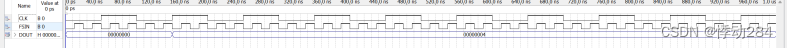

第二次仿真测试:基频信号CLK给10MHZ,待测信号FIN给40MHZ,输出DOUT以十六进制显示,观察波形图

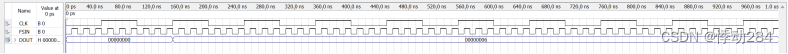

第三次仿真测试:基频信号CLK给10MHZ,待测信号FIN给60MHZ,输出DOUT以十六进制显示,观察波形图

结果分析:

波形图结果分析:根据频率计的原理,实质就是计数器。在测频控制信号CLK下进行计数,并将数据存到32位的锁存器REG32B1中,第一次仿真测试,基频信号CLK给10MHZ,待测信号FIN给20MHZ,那么应该累计计数2次待测信号FIN,输出结果十六进制为00000002符合期望。第二次仿真测试,基频信号CLK给10MHZ,待测信号FIN给40MHZ,那么应该累计计数4次待测信号FIN,输出结果十六进制为00000004符合期望。

六、实验结果

第一次测试:1HZ的测频控制信号CLK由CKLB1输入,待测信号输入FIN由主系统上单线连接CLKB0,我们将CLKB0接到16HZ上,如图显示:

第二次测试:1HZ的测频控制信号CLK由CKLB1输入,待测信号输入FIN由主系统上单线连接CLKB0,我们将CLKB0接到64HZ上,如图显示:

第三次测试:1HZ的测频控制信号CLK由CKLB1输入,待测信号输入FIN由主系统上单线连接 CLKB0,我们将CLKB0接到128HZ上,如图显示:

第四次测试:1HZ的测频控制信号CLK由CKLB1输入,待测信号输入FIN由主系统上单线连接 CLKB0,我们将CLKB0接到256HZ上,如图显示:

结果分析:

第一次测试:1HZ的测频控制信号CLK由CKLB1输入,待测信号输入FIN由主系统上单线连接CLKB0,频率选择16HZ,结果可以看出数码管对应的数是0000010,...16×1+0×1=16HZ,与待测信号频率相一致,输出频率符合期望。

第二次测试:1HZ的测频控制信号CLK由CKLB1输入,待测信号输入FIN由主系统上单线连接CLKB0,频率选择64HZ,结果可以看出数码管对应的数是0000040,...16×4+0×1=64HZ,与待测信号频率相一致,输出频率符合期望。

第三次测试:1HZ的测频控制信号CLK由CKLB1输入,待测信号输入FIN由主系统上单线连接CLKB0,频率选择128HZ,结果可以看出数码管对应的数是0000010,...16×8+0×1=128HZ,与待测信号频率相一致,输出频率符合期望。

第四次测试:1HZ的测频控制信号CLK由CKLB1输入,待测信号输入FIN由主系统上单线连接CLKB0,频率选择256HZ,结果可以看出数码管对应的数是00000100,...16²×1+16×0+0=256HZ,与待测信号频率相一致,输出频率符合期望。

百度网盘:链接:https://pan.baidu.com/s/1CM9KwnM-29LeFw33E6zoLA?pwd=nn88

提取码:nn88

http://链接:https://pan.baidu.com/s/1CM9KwnM-29LeFw33E6zoLA?pwd=nn88 提取码:nn88

3001

3001

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?