目录

1、总体架构

期待实现的功能:在PC端使用串口助手发送一幅分辨率为 640*480 的图片数据给 FPGA,FPGA 以外接 SDRAM 做缓存,将接收到的图片数据通过 VGA 显示器显示出来。

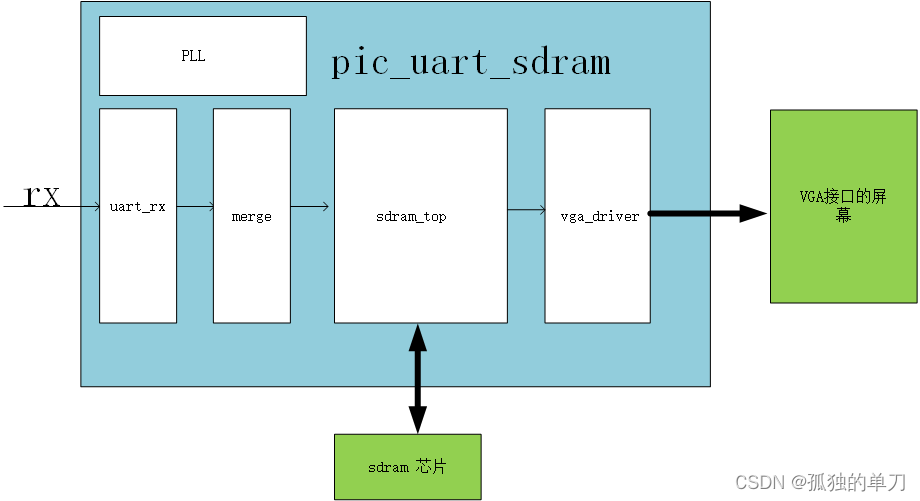

总体架构示意图如下:

- PLL模块:时钟生成模块。由于各个模块的时钟不尽相同,通过PLL统一生成时钟,全部接到全局时钟网络上

- uart_rx:串口接收模块。将接收到的串行信号,转换成8bit并行信号

- merge:数据拼接模块。将2个输入的8bit数据转换成16bit数据

- sdram_top:sdram读写控制器。可以实现高速、大量的数据缓存

- vga_driver:VGA接口驱动。实现图片(RGB565像素值)的VGA显示

这工程一看好像还挺多挺复杂的,那么我接下来就对整个图片的传送显示流程做

该博客介绍了如何通过FPGA实现串口接收图片数据,利用SDRAM缓存,并通过VGA显示。博主详细阐述了设计的总体架构,包括PLL模块、串口接收模块、数据拼接模块、SDRAM控制模块和VGA驱动模块的实现,并跳过了仿真部分,直接进行了上板验证。最终展示了FPGA如何逐行显示接收到的640x480 RGB565格式图像。

该博客介绍了如何通过FPGA实现串口接收图片数据,利用SDRAM缓存,并通过VGA显示。博主详细阐述了设计的总体架构,包括PLL模块、串口接收模块、数据拼接模块、SDRAM控制模块和VGA驱动模块的实现,并跳过了仿真部分,直接进行了上板验证。最终展示了FPGA如何逐行显示接收到的640x480 RGB565格式图像。

订阅专栏 解锁全文

订阅专栏 解锁全文

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?