名称:Quartus简易等精度频率计设计verilog代码仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

简易等精度频率计设计

二)要求

被測信号:TTL方波

A.频率测量范围:100HZ~MHz

B.测试误差:≤0.1%(全量程);

C.时钟频率:50kI1z

D.预闸门时间:0.1s

E.系统时钟频率:50MHz

F频率计算:保留1位小数

G顶层设计采用图形输入,各模块可以用功能模块或HDL语言等设计

评价标准

(一)提交设计过程和实验仿真等照片及大作业报告的电子文档,正文不得少于3000字符,网络复制率需小于40%,报告中的图片需清晰无水印

(二)细则。

1、频率测量误差分析(10%);2、分颍电路设计(10%);3、闸门电路设计(10%);4、计数电路设计(10%);5、计算电路设计(10%);6、仿真等验证(30%);

7、格式规范等(20%)

等精度频率计结题报告

1. 设计要求

本设计为等精度频率计,频率计指标要求如下:

1.频率测量范围:100Hz~1MHz;

2.被测信号为TTL方波;

3.测试误差:小于等于0.1%(全量程);

4.时钟频率:50KHz;

5.预闸门时间:0.1s;

6.系统时钟频率:50MHz;

7.频率计算:保留1位小数;

2. 设计原理

等精度测频方法是在直接测频方法的基础上发展起来的。它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,避除了对被测信号计数所产生的1个时钟误差,并且达到了在整个测试频段的等精度测量。等精度测量的核心思想在于如何保证在实际测量门闸内被测信号为整数个周期,这就需要在设计中让实际测量门闸信号与被测信号建立一定的关系。基于这种思想,设计中以被测信号的上升沿作为开启门闸和关闭门闸的驱动信号,只有在被测信号的上升沿才将图1中预置的“闸门”的状态锁存,因此在“实际闸门”内被测信号的个数就能保证整数个周期,这样就避免普通测量方法中被测信号的±1的误差,但会产生高频的标准频率信号的±1周期误差,由于标准频率的频率远高于被测信号,因此它产生的±1周期误差对测量精度的影响十分有限,特别是在中低频测量的时候,相较于传统的频率测量和周期测量方法,可以大大提高测量精度。

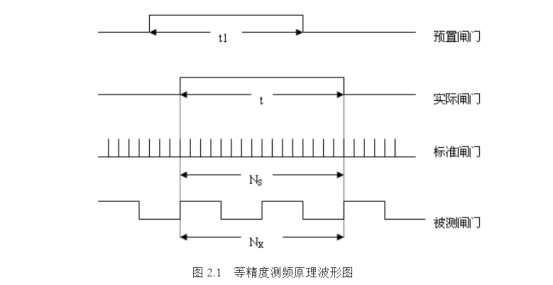

其测频原理如图2.1所示。在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。然后预置闸门关闭信号,下降沿到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次测量过程。可以看出,实际闸门时间t与预置闸门时间t1并不严格相等,但差值不超过被测信号的一个周期。

3. 测量误差分析

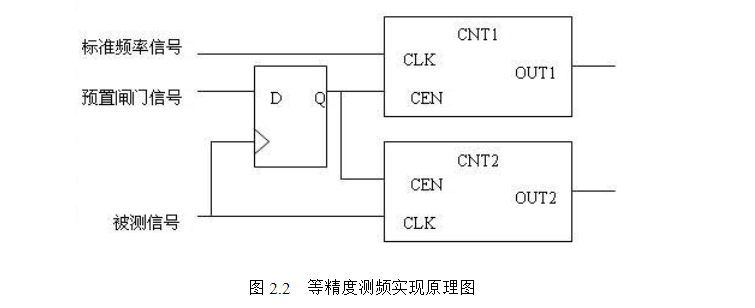

等精度测频的实现方法可简化为图2.2所示。CNT1和CNT2是两个可控计数器,标准频率信号从CNT1的时钟输入端CLK输入;经整形后的被测信号从CNT2的时钟输入端CLK输入。当预置门控信号为高电平时,经整形后的被测信号的上升沿通过D触发器的Q端同时启动CNT1和CNT2。CNT1、CNT2同时对标准频率信号和经整形后的被测信号进行计数,分别为Ns与Nx。当预置门信号为低电平的时候,后而来的被测信号的上升沿将使两个计数器同时关闭,所测得的频率为(Fs/Ns)*NX。则等精度测量方法测量精度与预置门宽度的标准频率有关,与被测信号的频率无关。在预置门时间和常规测频闸门时间相同而被测信号频率不同的情况下,等精度测量法的测量精度不变。

首先,被测信号频率fx的相对误差与被测信号的频率无关;其次,增大测量时间段“软件闸门”或提高标准频率,可以减小相对误差,提高测量精度;最后,由于一般提供标准频率的石英晶振稳定性很高,所以标准信号的相对误差很小,可忽略。假设标准信号的频率为50 KHz,只要实际闸门时间大于或等于0.1s,就可使测量的精度达到1/5 KHz。

4. 工作原理

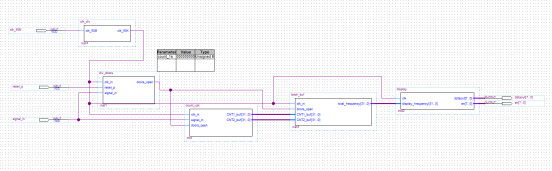

根据上述设计思想,对等精度频率计进行具体设计,整体设计框图如下图所示。

整体设计电路图

包括分频电路模块(clk_div),闸门电路模块(div_doors),计数电路模块(count_cal),运算电路模块(latch_buf),数码管显示模块(display)等,分频电路将时钟50M分频为50KHz作为标准时钟控制其他模块,闸门电路实现0.1s的闸门信号,计数电路按闸门时间分别采用标准时钟和被测信号进行计数,并将计数结果输入到运算电路模块,最终通过运算电路的计算得到频率结果,显示模块将最终的频率结果显示到数码管上。

各个模块具体功能介绍如下:

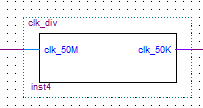

4.1 分频电路设计

分频模块用于将系统时钟50MHz分频为50KHz,本设计将50KHz作为标准频率信号。分频方法为计数法,即50M除以50K等于1000,则分频系数为1000.因此使用计数器对50MHz进行计数,当计数到1000后回0。计数值前500输出高电平,后500输出低电平,最终得到的输出信号就是50KHz。

分频模块框图

4.2 闸门电路设计

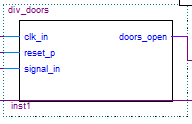

闸门信号产生模块用于产生周期为0.1s的闸门信号,并将闸门信号同步于被测信号,使闸门宽度为被测信号周期的整数倍。50KHz要得到0.1s的信号即10Hz,故分频系数为50K/10=5000。也使用计数法产生,计数2500后信号翻转,得到的就是一共计数5000的周期信号。得到的闸门周期则为0.1s,其中高电平时间就是闸门开启时间,为0.05秒。

闸门电路框图

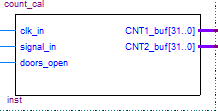

4.2 计数电路设计

计数模块使用标准频率和被测频率分别对闸门进行计数,得到2个计数值。使用CNT1计数标注频率信号,使用CNT2计数被测信号,然后将两个计数信号输出。计数CNT1使用clk_in作为计数时钟,当door_1s为1时开始计数,door_1s为0时计数清零。CNT2使用signal_in作为计数时钟,当door_1s为1时开始计数,door_1s为0时计数清零。

计数电路框图

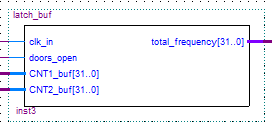

4.2 计算电路设计

运算锁存模块接收2个计数值,依据频率计算公式计算被测信号的频率。CNT1和CNT2得到后需要将数据锁存,以便于进行后续的频率计算,锁存信号为闸门信号的下降沿。闸门信号的下降沿获取方法是先将doors_open信号在clk_in时钟下打一拍得到door_1s_buf信号,再将door_1s_buf与上doors_open的非。

锁存后依据:待测频率=CNT2_buf*50000*10/CNT1_buf的计算公式进行计算,得到的频率值包含一位小数点。

运算电路框图

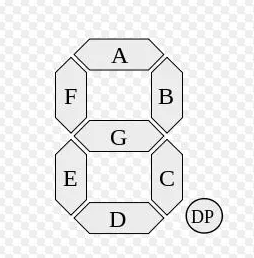

4.2 数码管显示电路设计

数码管显示模块用于控制数码管将被测频率显示出来。数码管显示使用动态扫描的方式,依次显示频率的不同位。使用8段数码管显示,每个数码管输入为8位,对应下图中的abcdefg7段加上小数点dp,当输入0时对应的段点亮,当输入为1时,对应的段灭。

根据上图可以观察到,若要显示数字0,需要DP灭,G灭,ABCDEF亮,也就是对应编码为“11000000”,其中从左到右依次对应DP-GFEDCBA。以此类推可以得到0~9的所有编码。一共有8个数码管,8个数码管共用一组段选信号(seg_select),因此为了同时显示8个数码管,需要对8个数码管依次切换,控制位选信号(bit_select)按顺序循环选通,低电平时对应数码管点亮。

部分代码展示:

// Copyright (C) 1991-2013 Altera Corporation // Your use of Altera Corporation's design tools, logic functions // and other software and tools, and its AMPP partner logic // functions, and any output files from any of the foregoing // (including device programming or simulation files), and any // associated documentation or information are expressly subject // to the terms and conditions of the Altera Program License // Subscription Agreement, Altera MegaCore Function License // Agreement, or other applicable license agreement, including, // without limitation, that your use is for the sole purpose of // programming logic devices manufactured by Altera and sold by // Altera or its authorized distributors. Please refer to the // applicable agreement for further details. // PROGRAM"Quartus II 64-Bit" // VERSION"Version 13.0.1 Build 232 06/12/2013 Service Pack 1 SJ Full Version" // CREATED"Wed Jun 15 23:50:45 2022" module frequency_detect( reset_p, signal_in, clk_50M, dataout, en ); input wirereset_p; input wiresignal_in; input wireclk_50M; output wire[7:0] dataout; output wire[7:0] en; wireSYNTHESIZED_WIRE_9; wireSYNTHESIZED_WIRE_10; wire[31:0] SYNTHESIZED_WIRE_4; wire[31:0] SYNTHESIZED_WIRE_7; wire[31:0] SYNTHESIZED_WIRE_8; count_calb2v_inst( .clk_in(SYNTHESIZED_WIRE_9), .signal_in(signal_in), .doors_open(SYNTHESIZED_WIRE_10), .CNT1_buf(SYNTHESIZED_WIRE_7), .CNT2_buf(SYNTHESIZED_WIRE_8)); div_doorsb2v_inst1( .clk_in(SYNTHESIZED_WIRE_9), .reset_p(reset_p), .signal_in(signal_in), .doors_open(SYNTHESIZED_WIRE_10)); defparamb2v_inst1.count_1s = 32'b00000000000000000110000110101000; displayb2v_inst2( .clk(SYNTHESIZED_WIRE_9), .display_frequency(SYNTHESIZED_WIRE_4), .dataout(dataout), .en(en)); latch_bufb2v_inst3( .clk_in(SYNTHESIZED_WIRE_9), .doors_open(SYNTHESIZED_WIRE_10), .CNT1_buf(SYNTHESIZED_WIRE_7), .CNT2_buf(SYNTHESIZED_WIRE_8), .total_frequency(SYNTHESIZED_WIRE_4)); clk_divb2v_inst4( .clk_50M(clk_50M), .clk_50K(SYNTHESIZED_WIRE_9)); endmodule

完整代码

扫描文章末尾的公众号二维码

5260

5260

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?