名称:基于FPGA的简易等精度频率计设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:简易等精度频率计设计

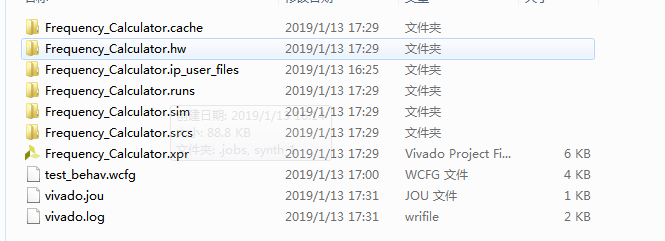

1. 工程文件

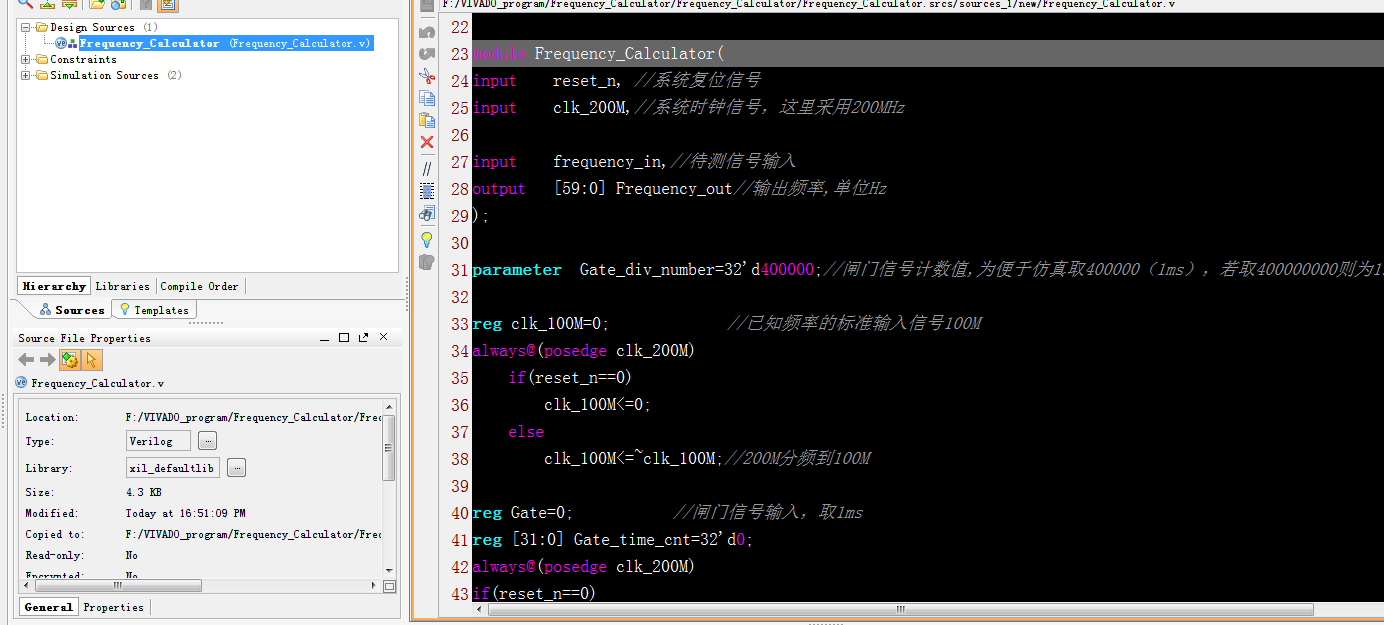

2. 程序代码

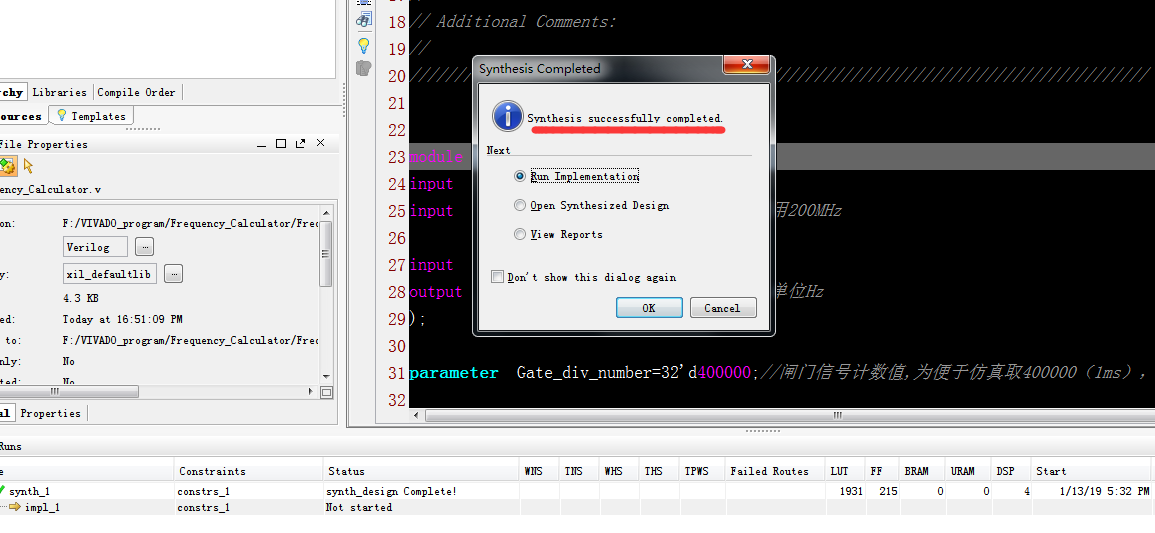

3. 程序综合

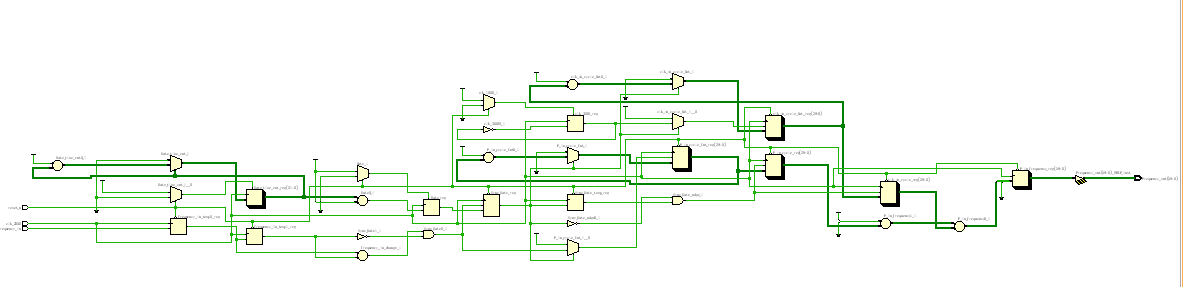

4. RTL图

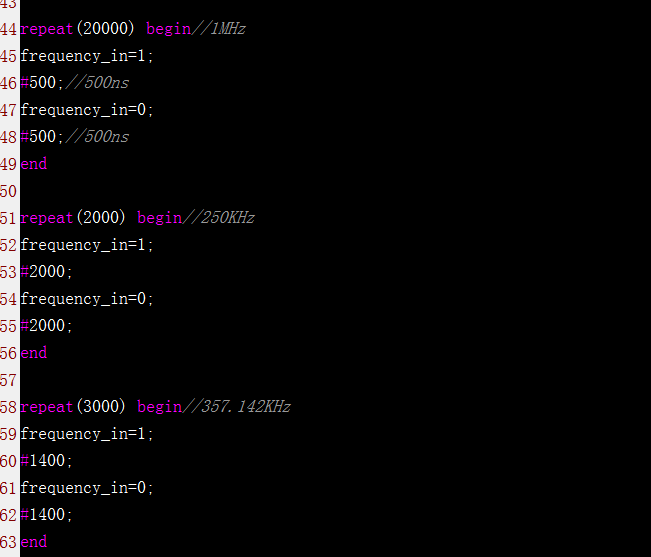

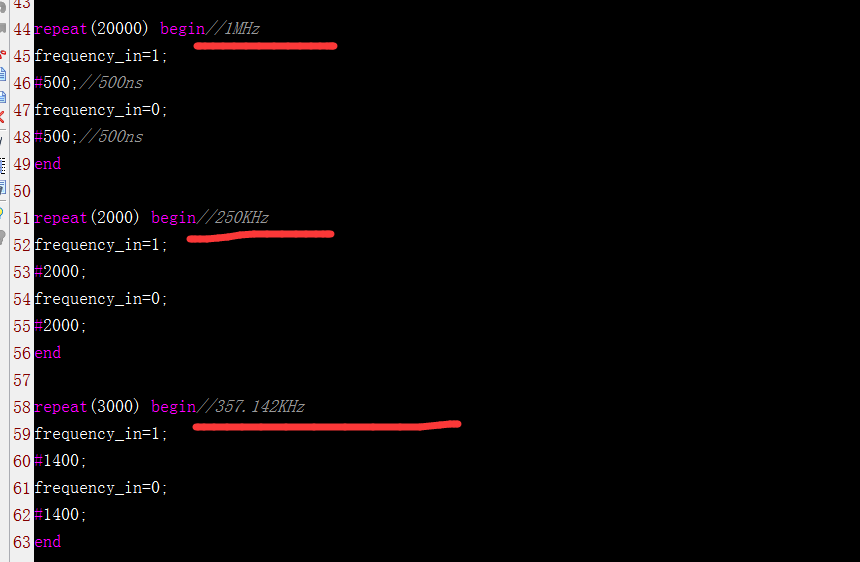

5. 测试代码

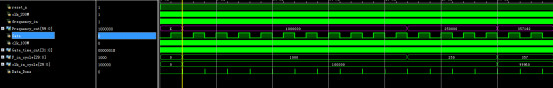

6. 仿真图

部分代码展示:

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2019/01/13 15:33:36 // Design Name: // Module Name: Frequency_Calculator // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module Frequency_Calculator( input reset_n, //系统复位信号 input clk_200M,//系统时钟信号,这里采用200MHz input frequency_in,//待测信号输入 output [59:0] Frequency_out//输出频率,单位Hz ); parameter Gate_div_number=32'd400000;//闸门信号计数值,为便于仿真取400000(1ms),若取400000000则为1s reg clk_100M=0; //已知频率的标准输入信号100M always@(posedge clk_200M) if(reset_n==0) clk_100M<=0; else clk_100M<=~clk_100M;//200M分频到100M reg Gate=0; //闸门信号输入,取1ms reg [31:0] Gate_time_cnt=32'd0; always@(posedge clk_200M) if(reset_n==0) Gate_time_cnt<=32'd0; else if(Gate_time_cnt==Gate_div_number-1) Gate_time_cnt<=32'd0; else Gate_time_cnt<=Gate_time_cnt+32'd1; always@(posedge clk_200M) if(reset_n==0) Gate<=0; else if(Gate_time_cnt>=Gate_div_number/2) Gate<=1;//闸门信号输入 else Gate<=0; reg[29:0]F_in_cycle; //待测信号的周期个数 reg[29:0]clk_in_cycle; //标准输入信号周期个数 reg Data_Done; //待测信号和标准输入信号的周期数计算完成 //同步待测信号输入 reg frequency_in_temp0,frequency_in_temp1; always@(posedge clk_200M or negedge reset_n) if(!reset_n)begin frequency_in_temp0 <= 1'b0; frequency_in_temp1 <= 1'b0; end else begin frequency_in_temp0 <= frequency_in; frequency_in_temp1 <= frequency_in_temp0; end //检测待测信号变化 wire frequency_in_change; assign frequency_in_change = (frequency_in_temp0 != frequency_in_temp1)?1'b1:1'b0; //同步闸门信号输出 reg Sync_Gate=0; always@(posedge clk_200M or negedge reset_n) if(!reset_n) Sync_Gate <= 1'b0; else if(frequency_in_change && (!frequency_in_temp1))begin if(Gate)

源代码

扫描文章末尾的公众号二维码

5263

5263

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?