名称:可控脉冲发生器VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

可控脉冲发生器

一.目的

1.了解可控脉冲发生器的实现原理

2.学习用VHDL编写复杂功能的代码。

二.简单设计原理

脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是要产生一个周

期和占空比可变的脉冲波形。可控脉冲发生器的实现原理比较简单,可以理解为计数器对输入的时钟信号进行分频的过程。通过改变计数器的上限值来达到改变周期的目的,通过改变电平翻转的阈值来达到改变占空比的目的

三.课题内容

1.查找资料,理解设计原理

2.用VHDL语言设计可控脉冲发生器(周期和占空比由设计者自行设定)

3.在 Quartusll上完成设计输入、全程编译和功能仿真

1. 设计思路

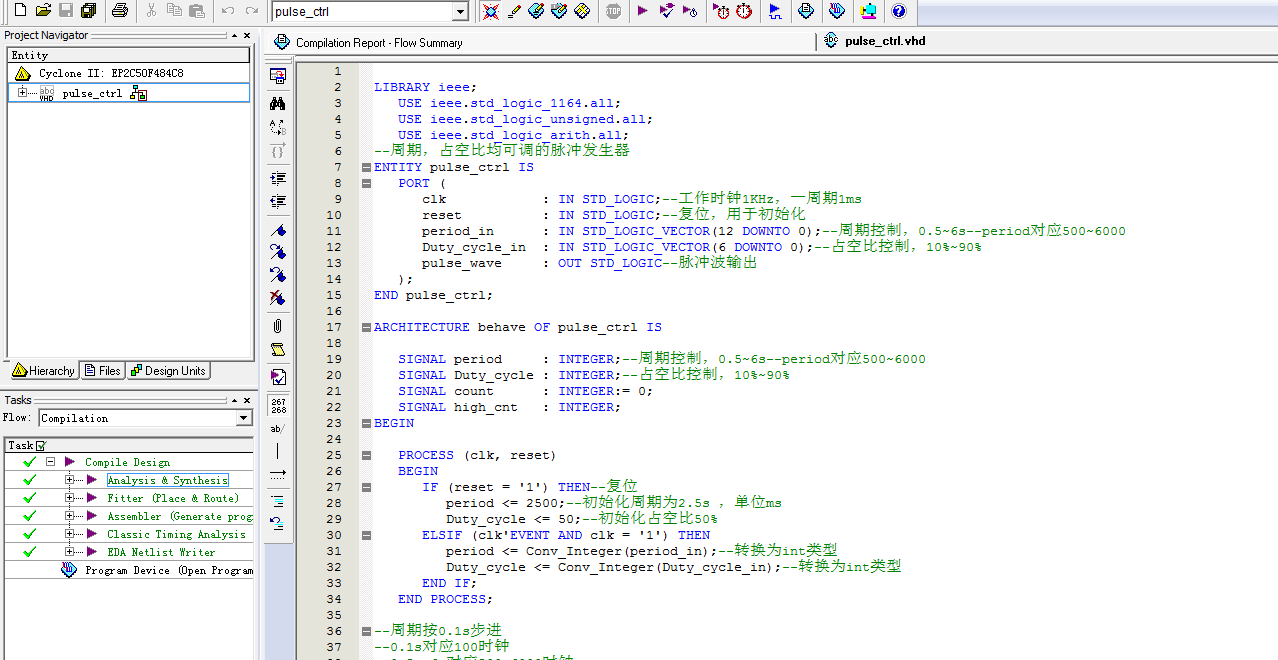

采用1KHz的工作时钟,脉冲周期为0.5s~6s,占空比10%~90%。复位后初始周期为2.5s,占空比50%。

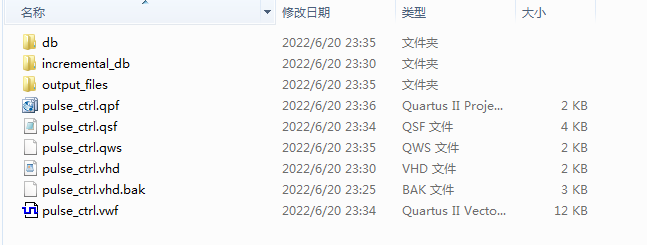

2. 工程文件

3. 程序文件

4. 程序编译

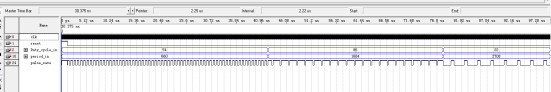

5. 仿真图

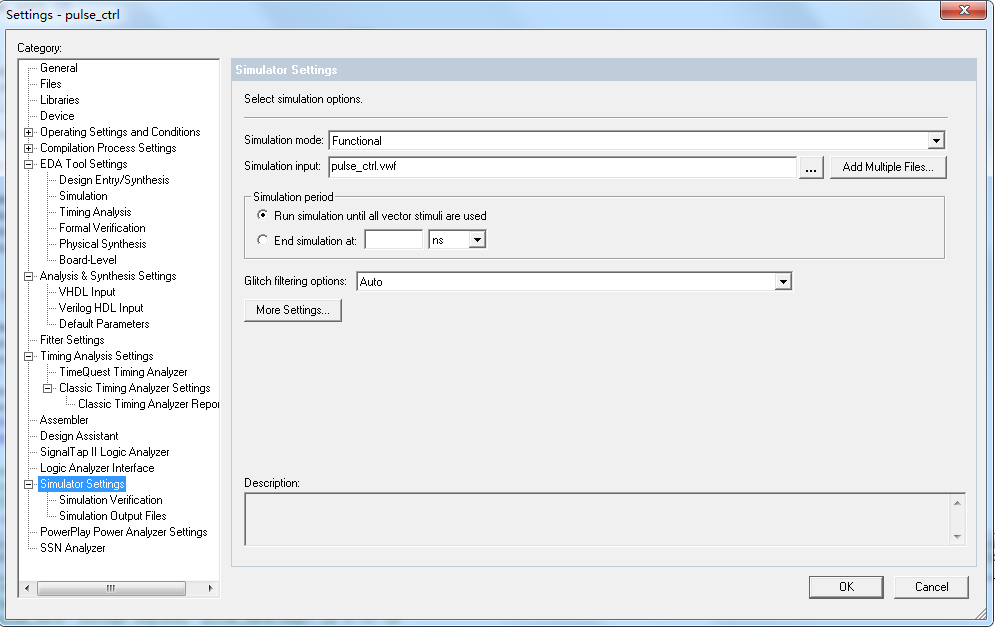

仿真设置

仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; USE ieee.std_logic_arith.all; --周期,占空比均可调的脉冲发生器 ENTITY pulse_ctrl IS PORT ( clk : IN STD_LOGIC;--工作时钟1KHz,一周期1ms reset : IN STD_LOGIC;--复位,用于初始化 period_in : IN STD_LOGIC_VECTOR(12 DOWNTO 0);--周期控制,0.5~6s--period对应500~6000 Duty_cycle_in : IN STD_LOGIC_VECTOR(6 DOWNTO 0);--占空比控制,10%~90% pulse_wave : OUT STD_LOGIC--脉冲波输出 ); END pulse_ctrl; ARCHITECTURE behave OF pulse_ctrl IS SIGNAL period : INTEGER;--周期控制,0.5~6s--period对应500~6000 SIGNAL Duty_cycle : INTEGER;--占空比控制,10%~90% SIGNAL count : INTEGER:= 0; SIGNAL high_cnt : INTEGER; BEGIN PROCESS (clk, reset) BEGIN IF (reset = '1') THEN--复位 period <= 2500;--初始化周期为2.5s ,单位ms Duty_cycle <= 50;--初始化占空比50% ELSIF (clk'EVENT AND clk = '1') THEN period <= Conv_Integer(period_in);--转换为int类型 Duty_cycle <= Conv_Integer(Duty_cycle_in);--转换为int类型 END IF; END PROCESS;

源代码

扫描文章末尾的公众号二维码

3057

3057

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?