名称:可调的脉冲发生器Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

内容及要求

实现周期、占空比均可调的脉冲发生器

(1)采用1khz的工作时钟

(2)脉冲周期0.5s~6s,占空比10%~90%

(3)可初始化:周期2.5s,占空比50%

(4)使用实验室的开发箱或自备开发板完成设计

(5)完成全部流程:设计规范文档、模块设计、代码输入、功能仿真、约束与综合、时序仿真、下载验证等

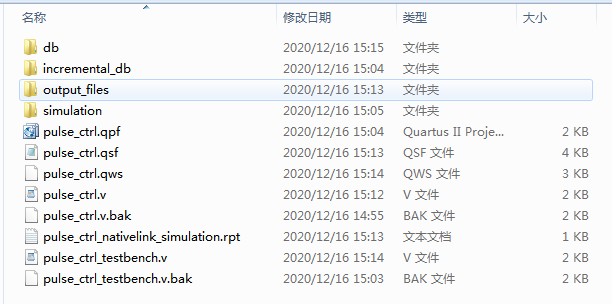

1. 工程文件

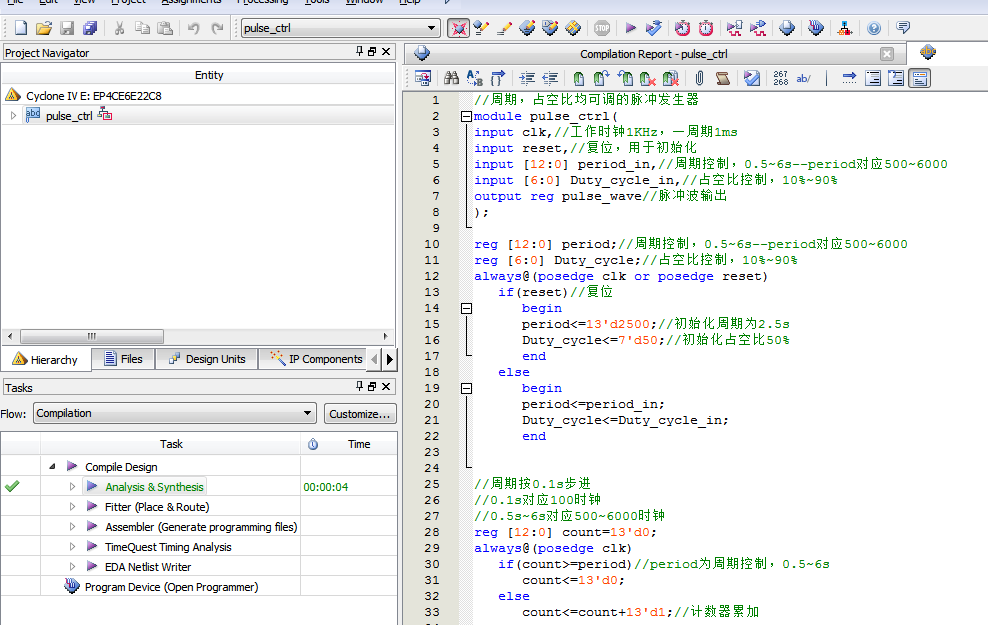

2. 程序文件

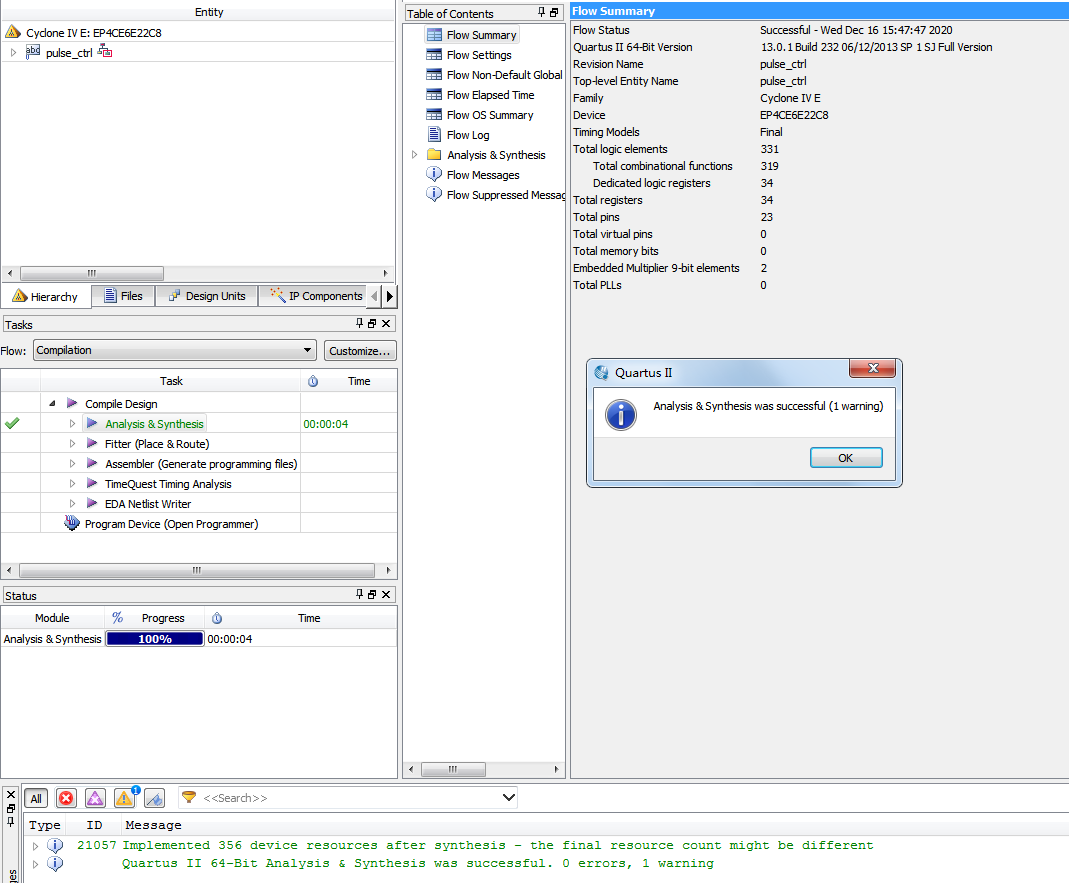

3. 程序编译

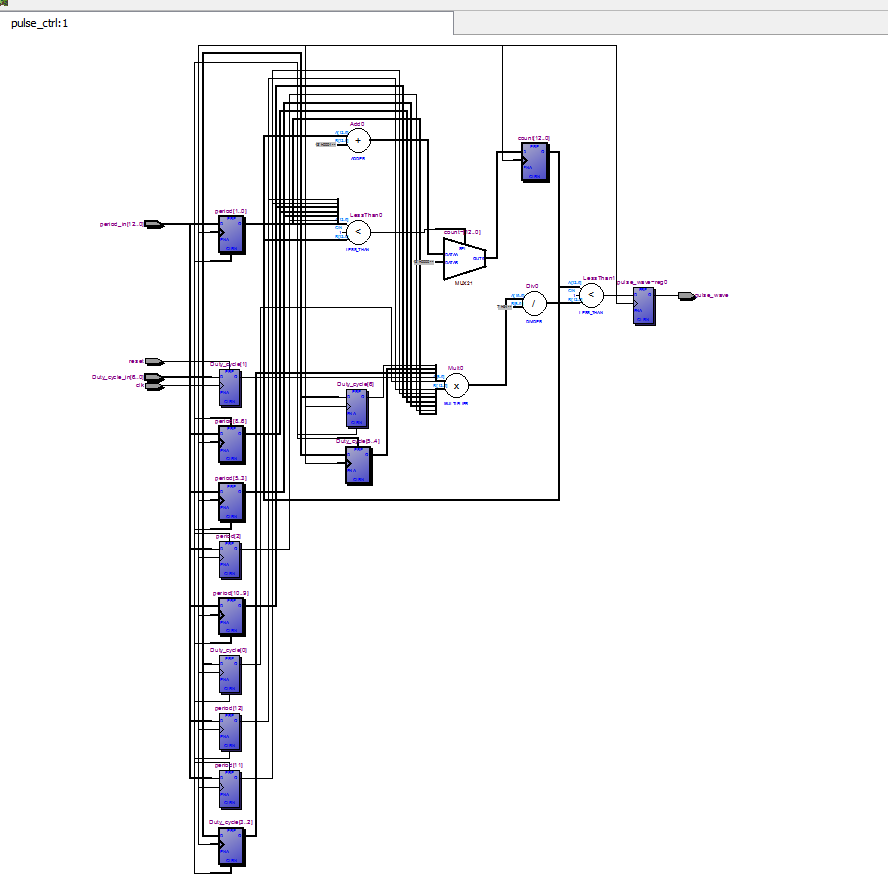

4. RTL图

5. Testbench

6. 仿真图

部分代码展示:

//周期,占空比均可调的脉冲发生器 module pulse_ctrl( input clk,//工作时钟1KHz,一周期1ms input reset,//复位,用于初始化 input [12:0] period_in,//周期控制,0.5~6s--period对应500~6000 input [6:0] Duty_cycle_in,//占空比控制,10%~90% output reg pulse_wave//脉冲波输出 ); reg [12:0] period;//周期控制,0.5~6s--period对应500~6000 reg [6:0] Duty_cycle;//占空比控制,10%~90% always@(posedge clk or posedge reset) if(reset)//复位 begin period<=13'd2500;//初始化周期为2.5s Duty_cycle<=7'd50;//初始化占空比50% end else begin period<=period_in; Duty_cycle<=Duty_cycle_in; end //周期按0.1s步进 //0.1s对应100时钟 //0.5s~6s对应500~6000时钟 reg [12:0] count=13'd0; always@(posedge clk) if(count>=period)//period为周期控制,0.5~6s count<=13'd0; else count<=count+13'd1;//计数器累加 //占空比控制10%~90% //Duty_cycle控制占空比,占空比乘以周期等于高电平时间 wire [12:0] high_cnt; assign high_cnt=Duty_cycle*period/100;//计算高电平时间 always@(posedge clk) if(count<=high_cnt)//小于等于高电平时间 pulse_wave<=1;//输出高电平 else pulse_wave<=0;//输出低电平 endmodule

源代码

扫描文章末尾的公众号二维码

本文详细描述了如何在Quartus环境下,使用Verilog语言编写一个周期和占空比可调的脉冲发生器。代码示例展示了如何设置初始条件、周期和占空比控制,以及通过计数器实现脉冲输出。最后,介绍了完整的工程流程,包括设计文档、模块设计和仿真验证。

本文详细描述了如何在Quartus环境下,使用Verilog语言编写一个周期和占空比可调的脉冲发生器。代码示例展示了如何设置初始条件、周期和占空比控制,以及通过计数器实现脉冲输出。最后,介绍了完整的工程流程,包括设计文档、模块设计和仿真验证。

754

754

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?