名称:基于FPGA的占空比检测功能VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

FPGA实现功能

(1)比较电路输出的方波信号输入到FPGA,方波信号的频率范围是

100Hz~5kHz,占空比范围5%~95%

(2)使用硬件描述语言对FPGA编程,设计数字电路实现对输入的方波信号

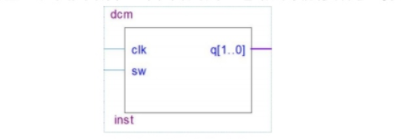

进行占空比范围判断并显示判断结果,电路的顶层实体参考如图5所示;

图5顶层实体参考

(3)当方波占空比范围在5%~25%时,电路输出“00”;当方波占空比范围在

26%~50%时,电路输出“01”;当方波占空比范围在51%~75%时,电路输出“10”;当方波占空比范围在76%95%时,电路输出“11”;

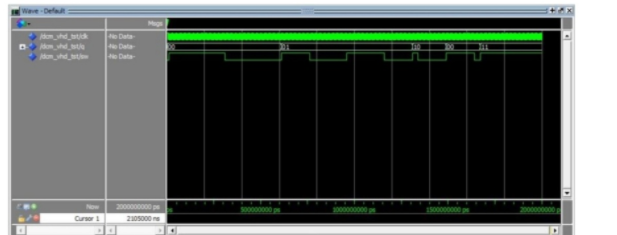

(4)每当输入信号的方波上升沿到来时,输岀占空比范围判断结果(此结果为方波上一个周期的占空比判断结果),参考时序图如图6所示。

图6参考时序图

1. 工程文件

2. 程序文件

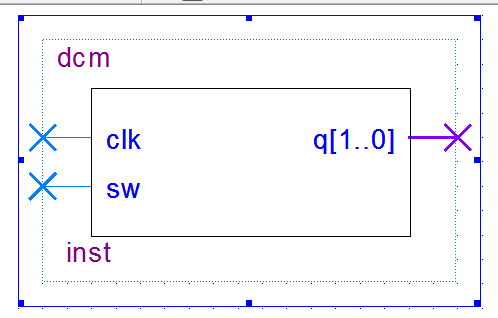

端口图

3. 程序编译

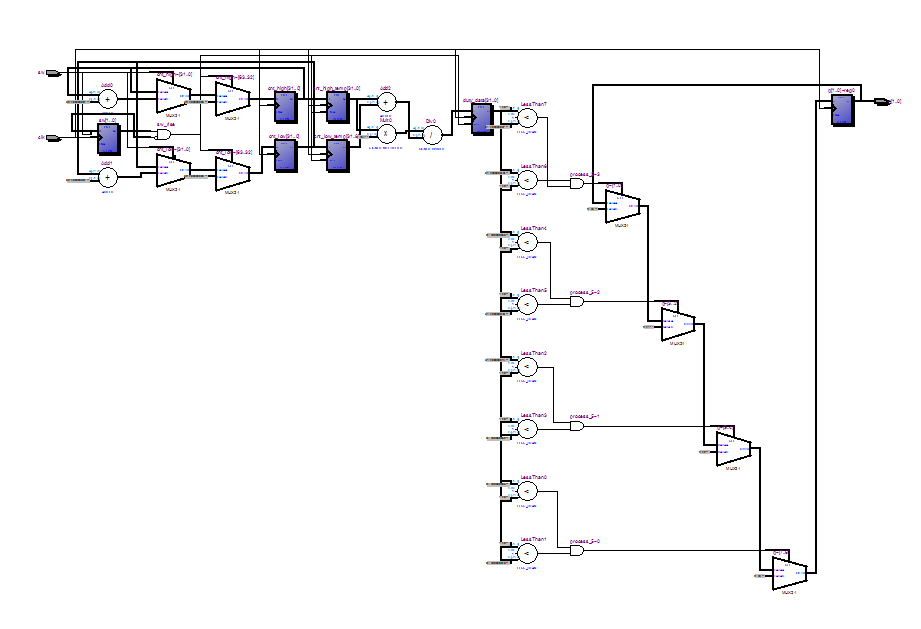

4. RTL图

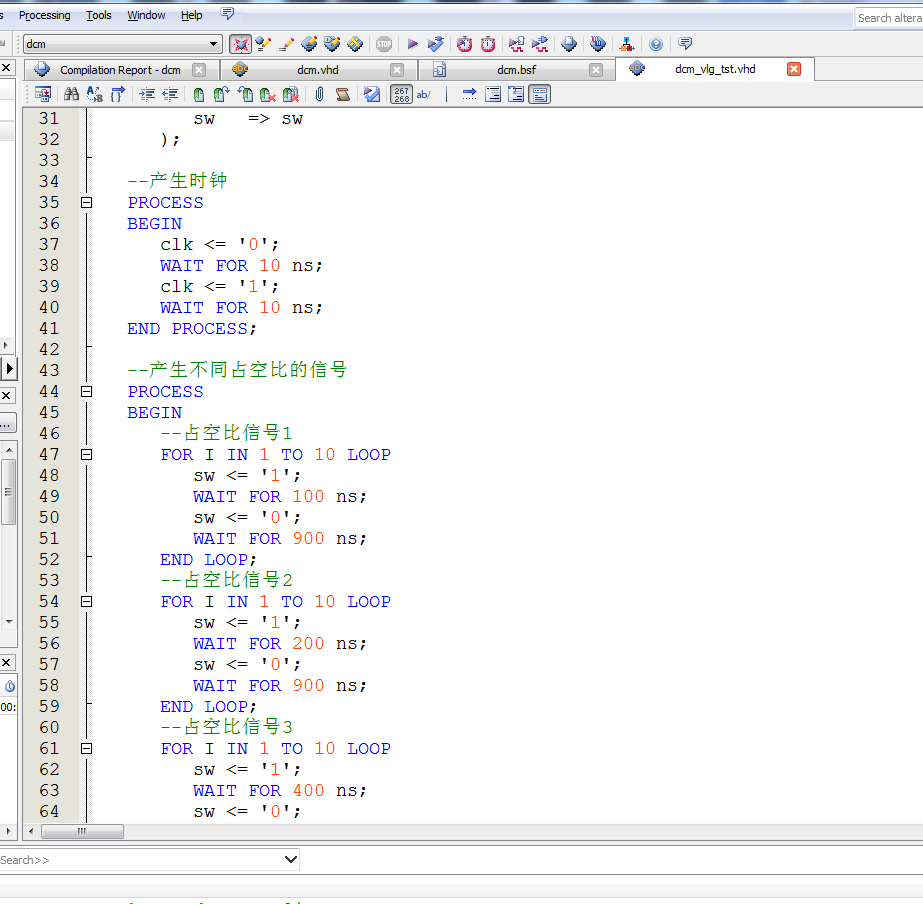

5. Testbench

6. 仿真图

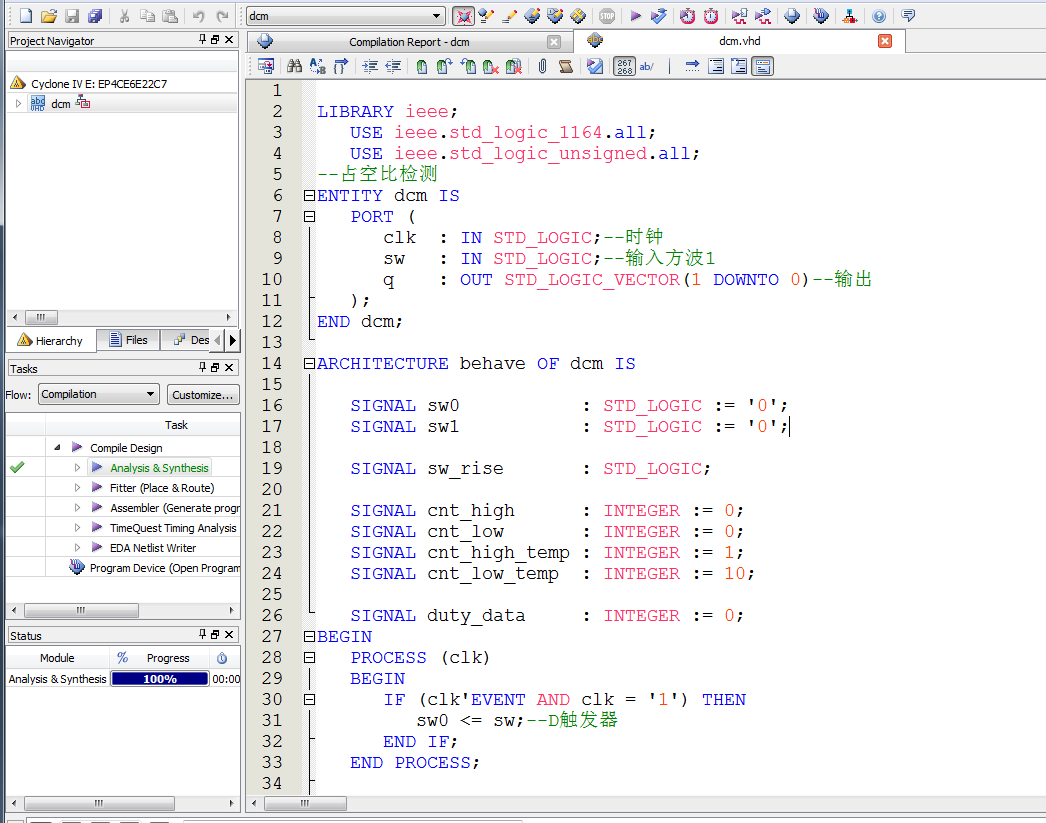

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --占空比检测 ENTITY dcm IS PORT ( clk : IN STD_LOGIC;--时钟 sw : IN STD_LOGIC;--输入方波1 q : OUT STD_LOGIC_VECTOR(1 DOWNTO 0)--输出 ); END dcm; ARCHITECTURE behave OF dcm IS SIGNAL sw0 : STD_LOGIC := '0'; SIGNAL sw1 : STD_LOGIC := '0'; SIGNAL sw_rise : STD_LOGIC; SIGNAL cnt_high : INTEGER := 0; SIGNAL cnt_low : INTEGER := 0; SIGNAL cnt_high_temp : INTEGER := 1; SIGNAL cnt_low_temp : INTEGER := 10; SIGNAL duty_data : INTEGER := 0; BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN sw0 <= sw;--D触发器 END IF; END PROCESS; PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN sw1 <= sw0;--D触发器 END IF; END PROCESS; sw_rise <= sw0 AND NOT(sw1);--得到方波的上升沿信号 PROCESS (clk) BEGIN

源代码

扫描文章末尾的公众号二维码

5410

5410

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?