名称:基于FPGA的AD5444时序设计Verilog代码ISE仿真(文末获取)

软件:ISE

语言:Verilog

代码功能:

要求

1.产生调制信号,即控制DA,每路调制信号率为1000Hz

系统上电后,波形就能够产生,用示波器测量能查看到

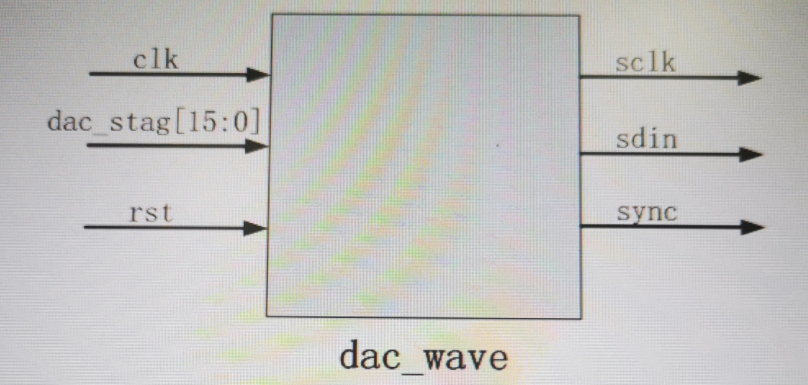

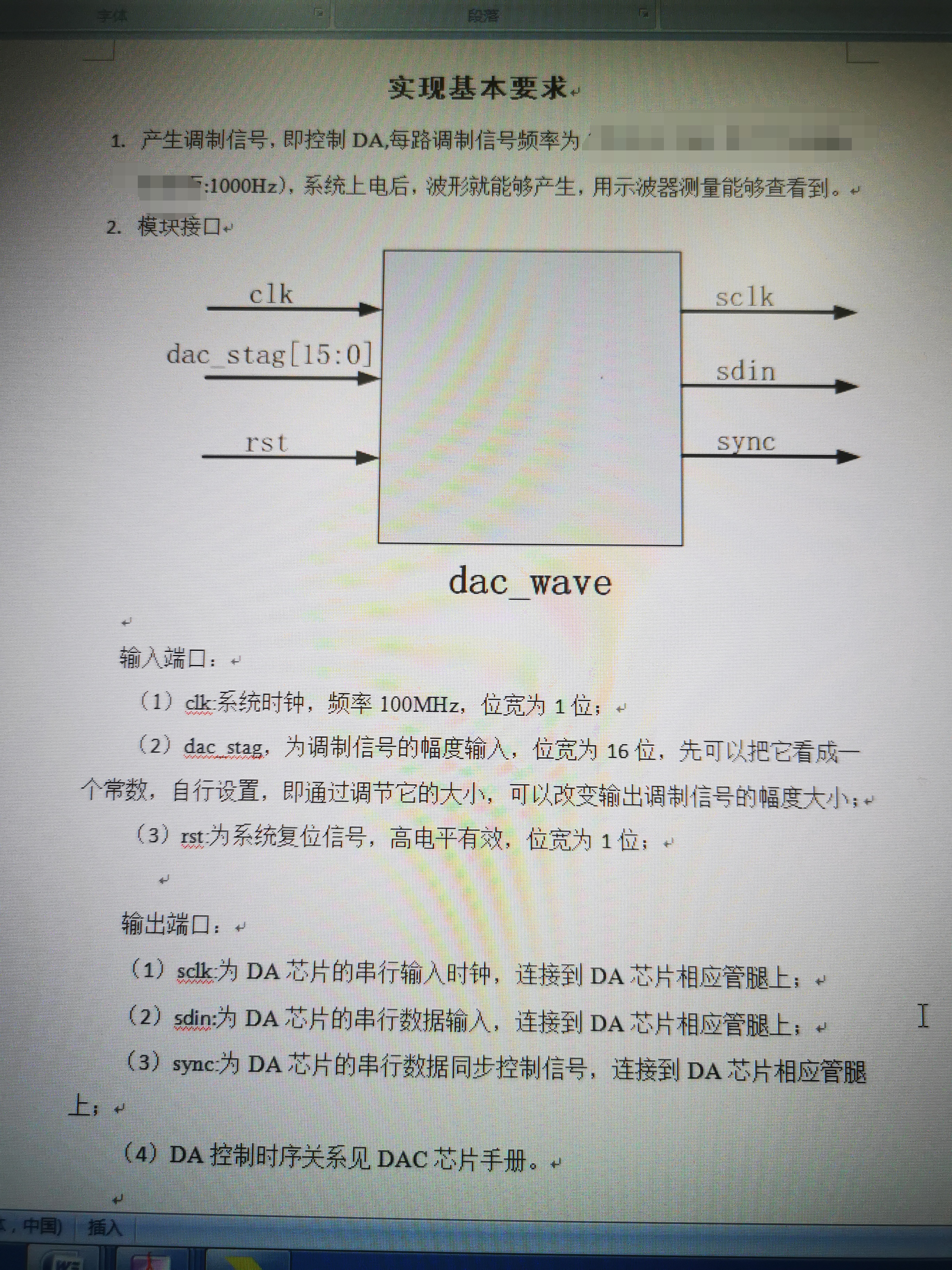

2.模块接口

输入端口

(1)clk系统时钟,频率100MHz,位宽为1位

(2)dac stag,,为调制信号的幅度输人,位宽为16位,先可以把它看成个常数,自行设置,即通过调节它的大小,可以改变输出调制信号的幅度大小

(3)rst为系统复位信号,高电平有效,位宽为1位:

输出端口:

(1)sclk为DA芯片的串行输入时钟,连接到DA芯片相应管腿上

(2)sdin为DA芯片的串行数据输入,连接到DA芯片相应管腿上

(3)sync为DA芯片的串行数据同步控制信号,连接到DA芯片相应管腿

(4)DA控制时序关系见DAC芯片手册

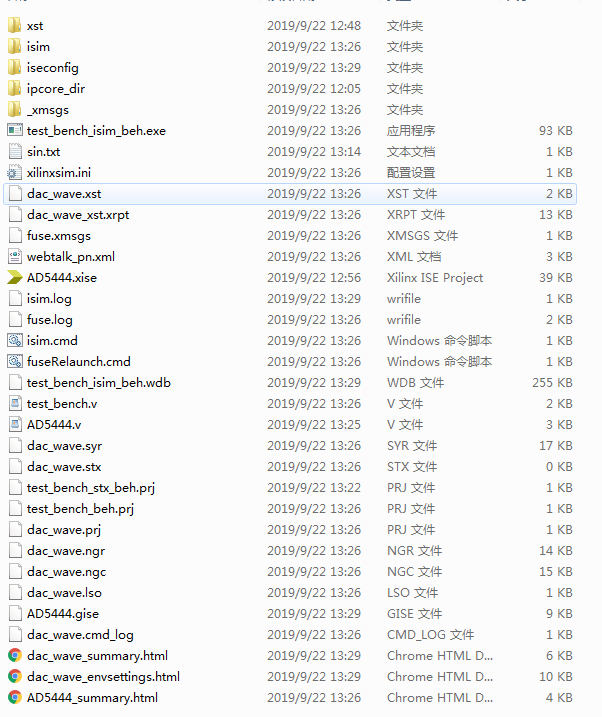

1. 工程文件

2. 程序文件

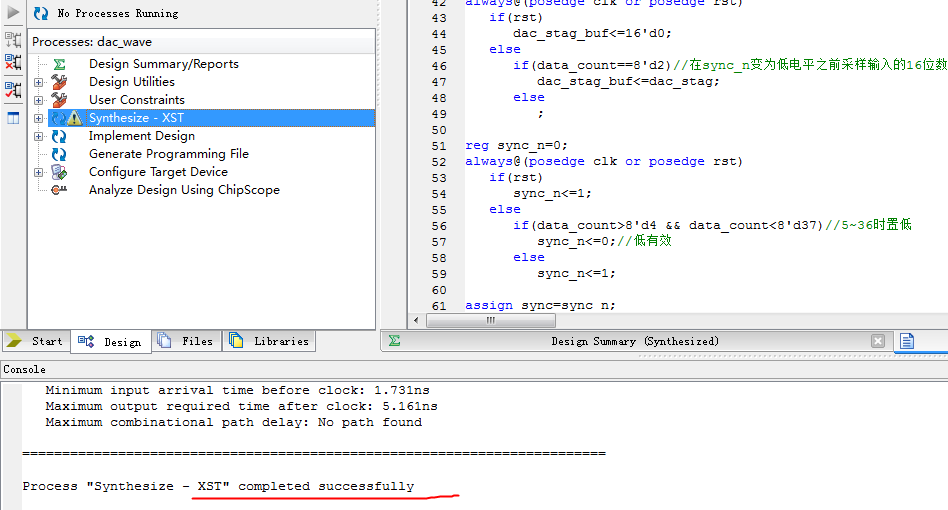

3. 程序编译

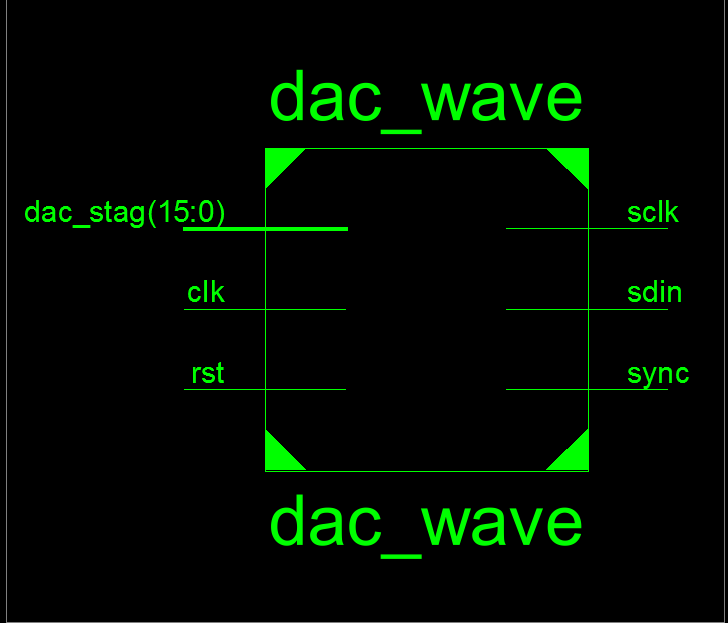

4. RTL图

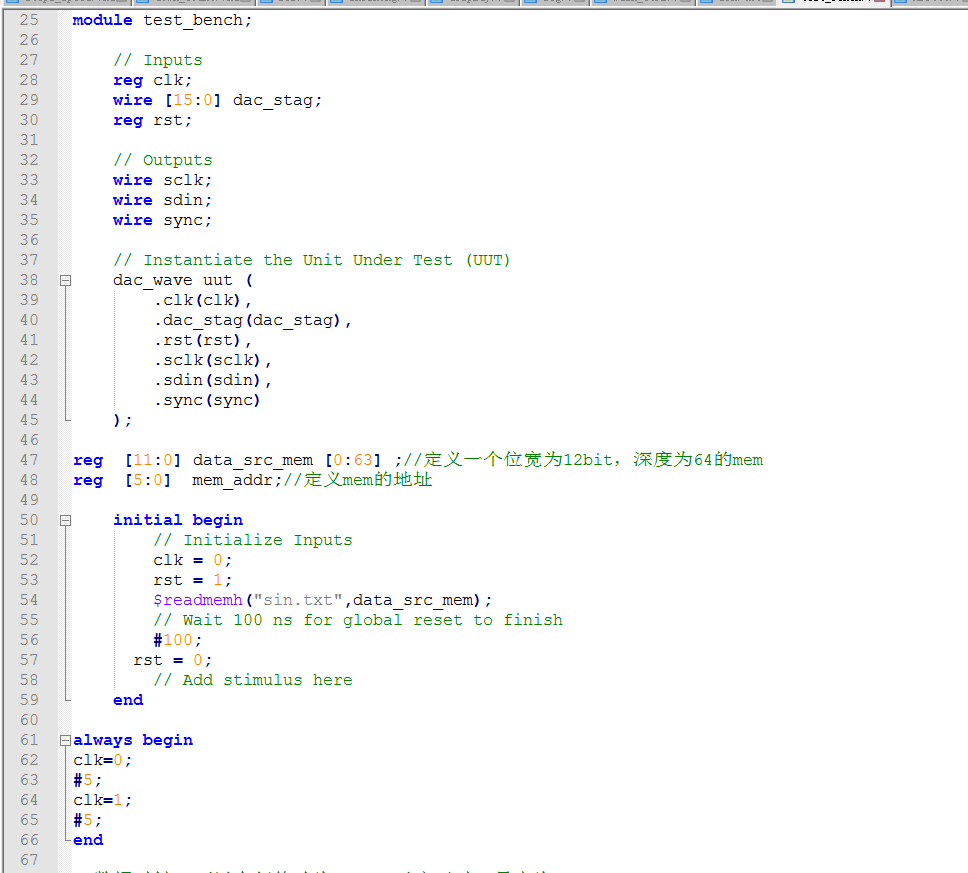

5. Testbench

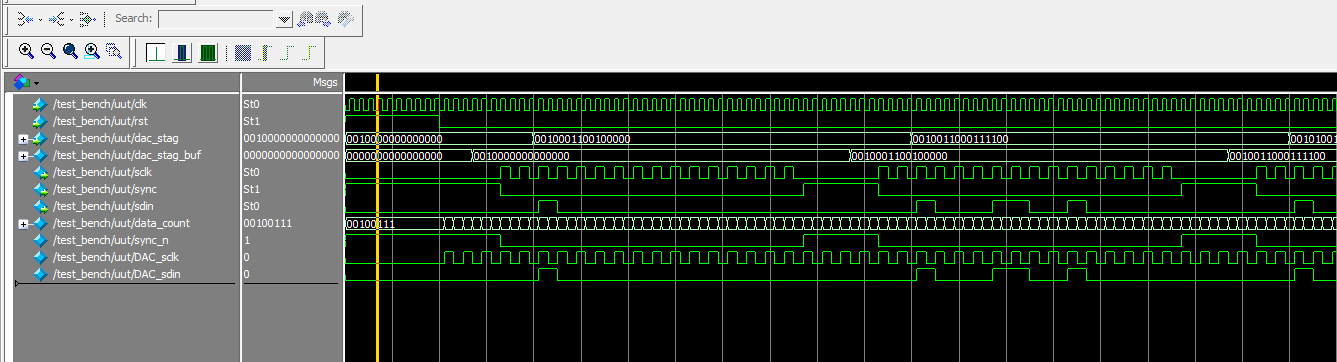

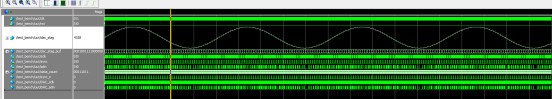

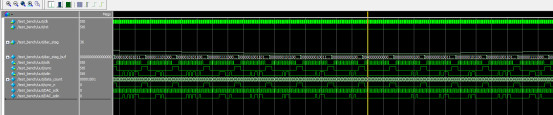

6. modelsim仿真图

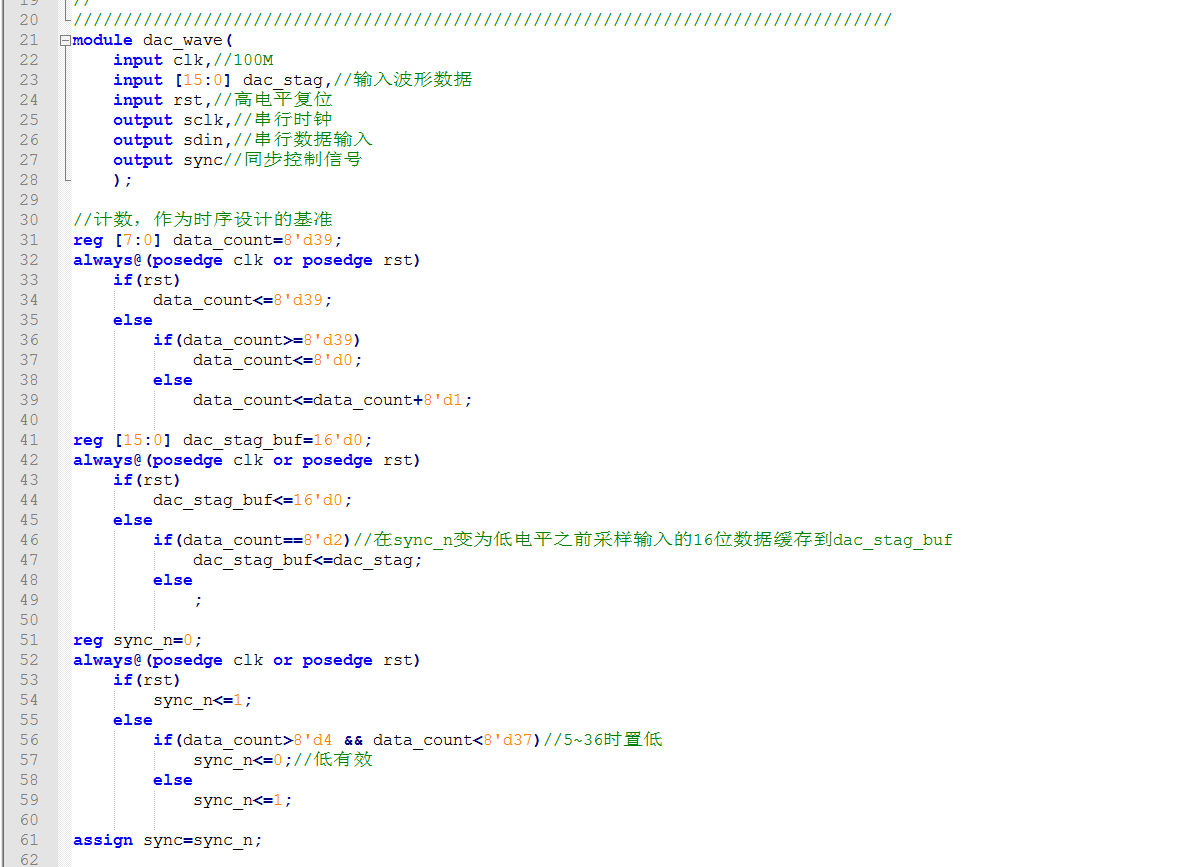

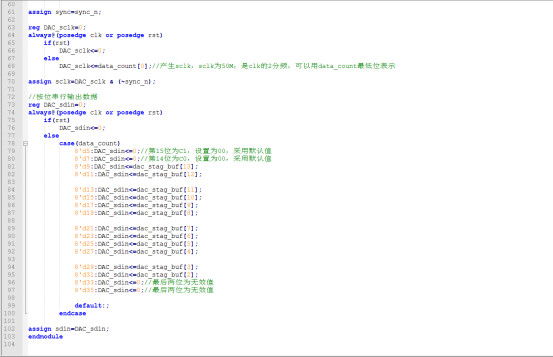

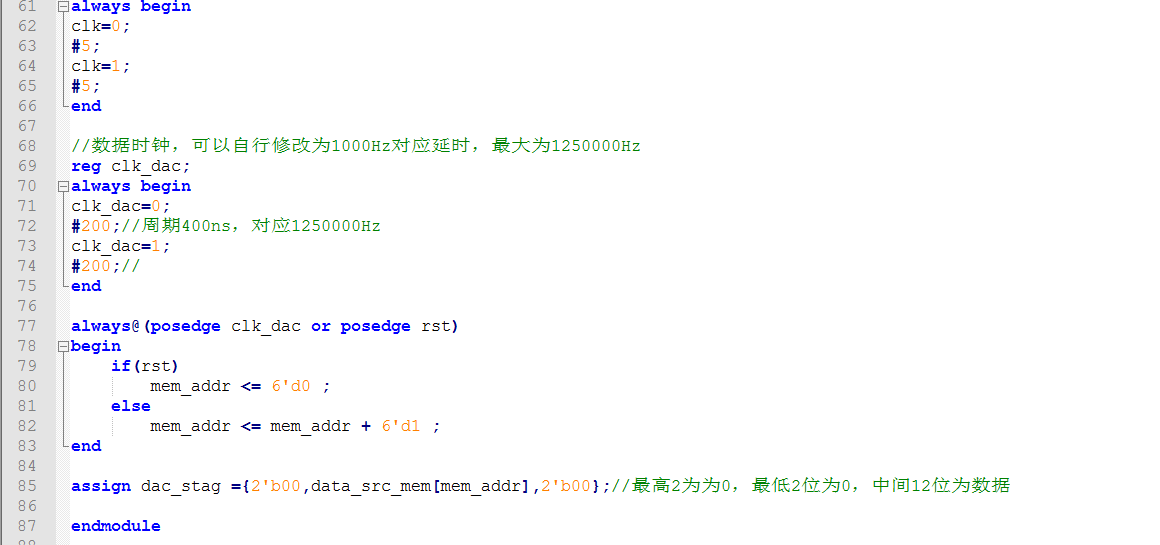

部分代码展示:

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 12:08:32 09/22/2019 // Design Name: // Module Name: AD5444 // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module dac_wave( input clk,//100M input [15:0] dac_stag,//输入波形数据 input rst,//高电平复位 output sclk,//串行时钟 output sdin,//串行数据输入 output sync//同步控制信号 ); //计数,作为时序设计的基准 reg [7:0] data_count=8'd39; always@(posedge clk or posedge rst) if(rst) data_count<=8'd39; else if(data_count>=8'd39) data_count<=8'd0; else data_count<=data_count+8'd1; reg [15:0] dac_stag_buf=16'd0; always@(posedge clk or posedge rst) if(rst) dac_stag_buf<=16'd0; else if(data_count==8'd2)//在sync_n变为低电平之前采样输入的16位数据缓存到dac_stag_buf dac_stag_buf<=dac_stag; else ; reg sync_n=0; always@(posedge clk or posedge rst) if(rst) sync_n<=1; else if(data_count>8'd4 && data_count<8'd37)//5~36时置低 sync_n<=0;//低有效 else sync_n<=1; assign sync=sync_n; reg DAC_sclk=0; always@(posedge clk or posedge rst) if(rst) DAC_sclk<=0; else

源代码

扫描文章末尾的公众号二维码

3205

3205

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?