名称:基于FPGA的量程自动转换数字式频率计的设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

一、设计的主要技术参数

1.频率计的测量范围为1KHZ,量程分10KHZ、100KHZ和1000KHZ三档(最大读数分别为9.99KHZ、99.9KHZ、999KHZ)。

2.要求量程可根据被测量的大小自动转换。即当计数器溢出时,产生一个换档信号,让整个计数时间减少为原来的1/10,从而实现换档功能。

3.要求实现溢出报警功能。即当频率高于999KHZ时,产生一报警信号,点亮LED灯,从而实现溢出报警功能。

二、设计任务

1.频率计的系统设计可以分为4位10进制计数模块、闸门控制模块、译码显示模块和可自动换档基准时钟模块。

2.可自动换档模块为闸门控制模块提供3个档也就是3个测量范围的基准时钟信号,通过计数器的最高位溢出情况来判定工作在第几档。

3.闸门控制模块根据基准时钟信号产生基准时钟信号周期2倍的周期使能信号,随后为锁存器产生一周期性地锁存信号,再然后为计数模块产生一周期性地清零信号。

4. 4位10进制计数模块在使能信号和清零信号的控制下对被测信号的波形变化进行计数,若产生溢出则为自动换档模块输出一换档信号。

译码显示模块负责不闪烁的显示被测信号的频率以及数字频率计目前工作的档位。

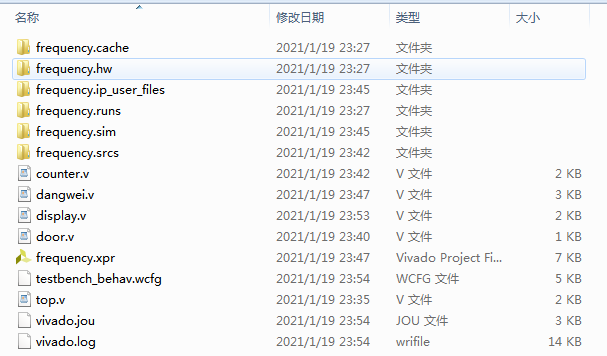

1. 工程文件

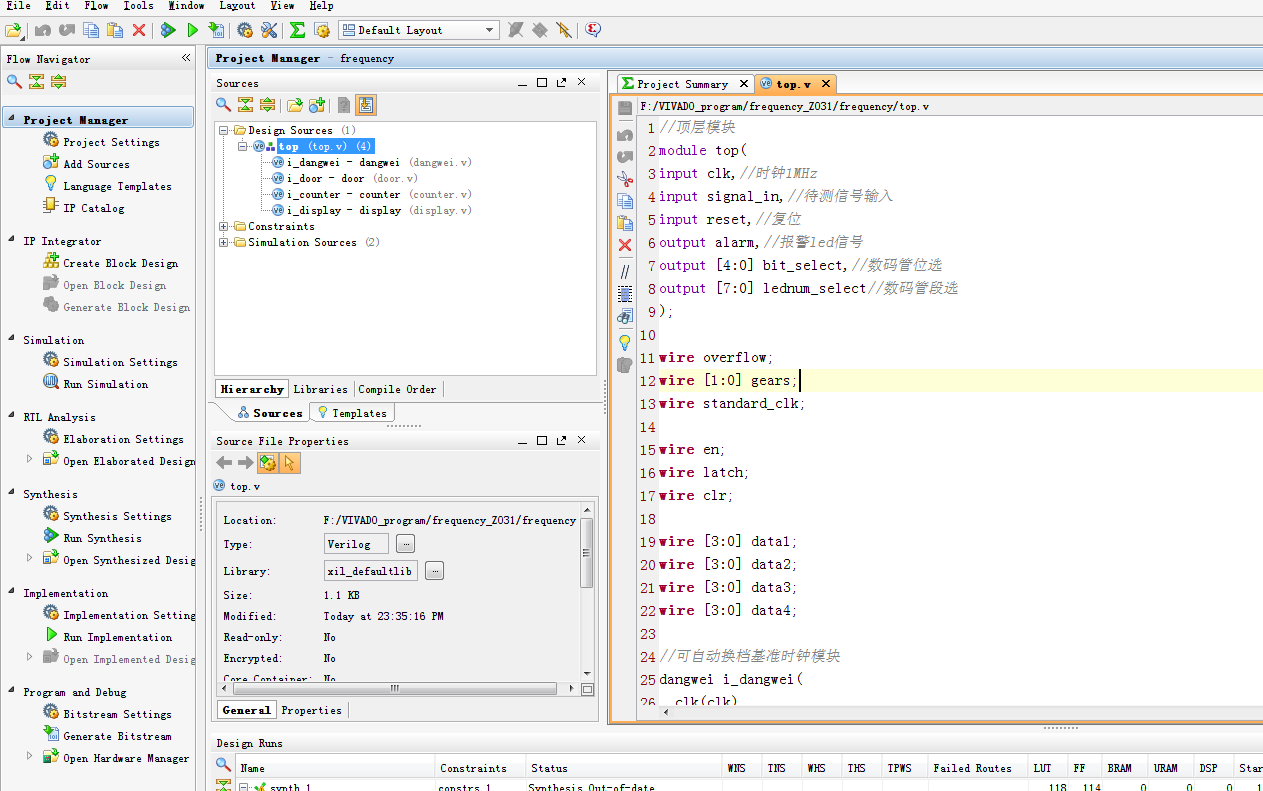

2. 程序文件

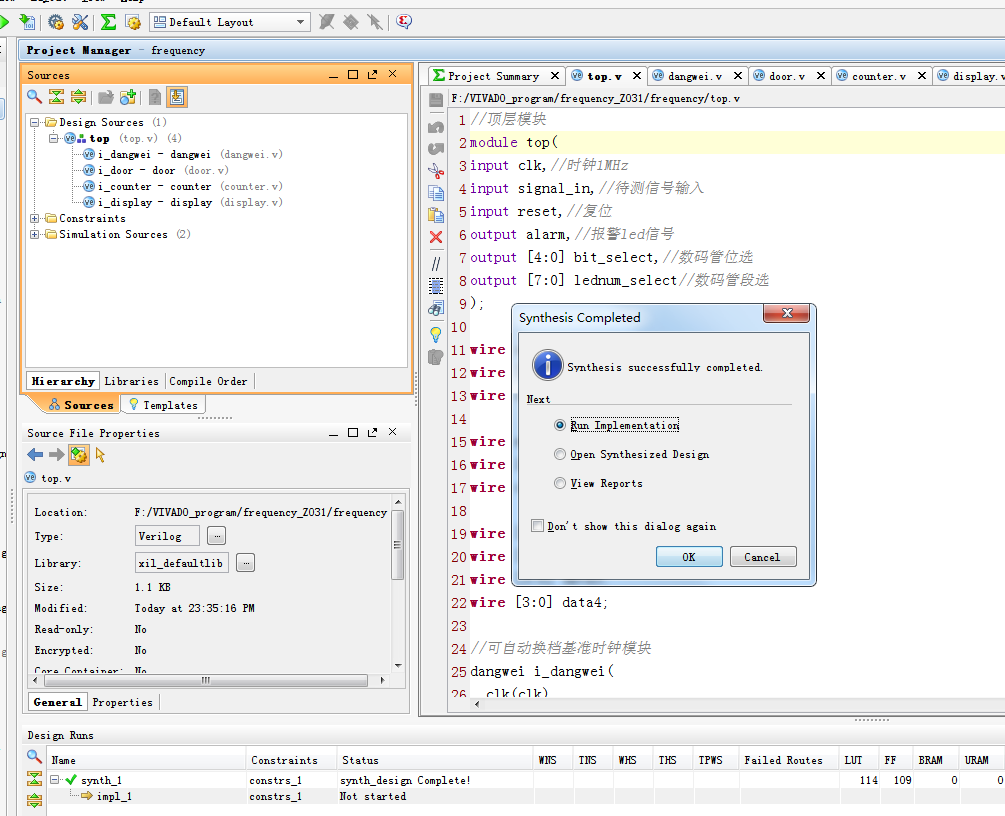

3. 程序编译

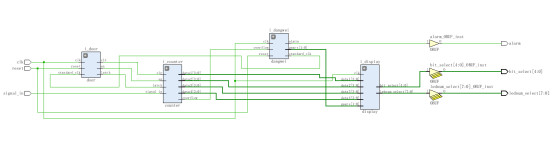

4. RTL图

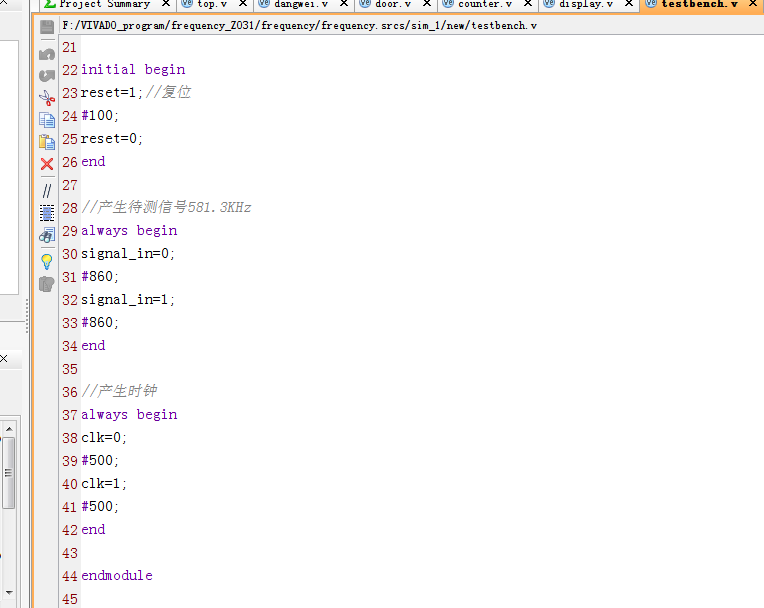

5. Testbench

6. 仿真图

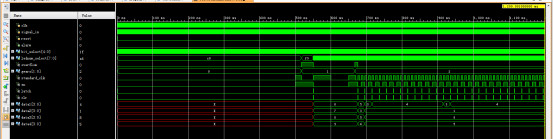

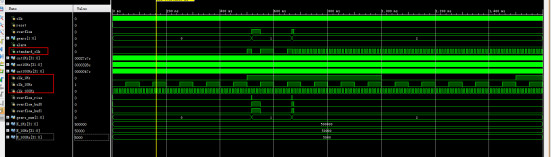

顶层模块仿真图(整体仿真图)

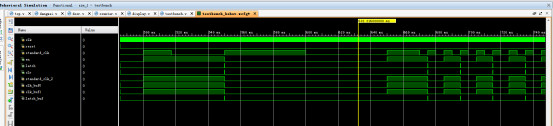

可自动换档基准时钟模块(仿真图)

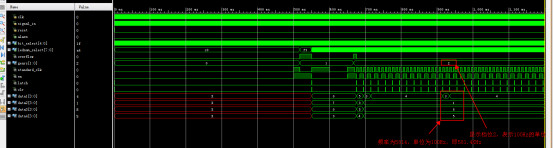

闸门控制模块(仿真图)

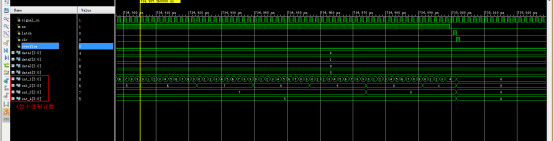

4位10进制计数模块(仿真图)

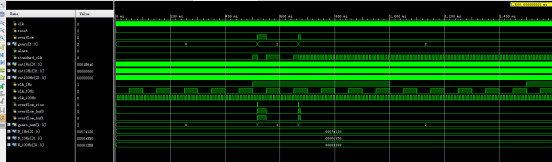

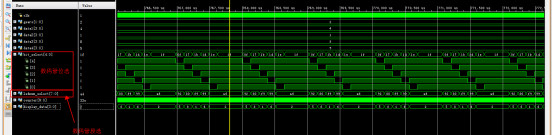

译码显示模块(仿真图)

部分代码展示:

//4位10进制计数模块 //4位10进制计数模块在使能信号和清零信号的控制下对被测信号的波形变化进行计数,若产生溢出则为自动换档模块输出一换档信号 module counter( input signal_in,//待测信号 input en, input latch, input clr, output reg overflow,//输出一换档信号 output reg [3:0] data1,//4位计数值1 output reg [3:0] data2,//4位计数值2 output reg [3:0] data3,//4位计数值3 output reg [3:0] data4//4位计数值4 ); reg [3:0] cnt_1=4'd0; reg [3:0] cnt_2=4'd0; reg [3:0] cnt_3=4'd0; reg [3:0] cnt_4=4'd0; always@(*) if(clr) overflow=0;//清零 else if(en) if(cnt_4==4'd9 && cnt_3==4'd9 && cnt_2==4'd9 && cnt_1==4'd9)//计数到9999,溢出 overflow=1;//若产生溢出则为自动换档模块输出一换档信号 else overflow=overflow; else overflow=0; always@(posedge signal_in or posedge clr) if(clr) begin//计数清零 cnt_1<=4'd0; cnt_2<=4'd0; cnt_3<=4'd0; cnt_4<=4'd0; end else if(en) if(cnt_4==4'd9 && cnt_3==4'd9 && cnt_2==4'd9 && cnt_1==4'd9)//计数到9999 begin cnt_1<=4'd0; cnt_2<=4'd0; cnt_3<=4'd0; cnt_4<=4'd0; end else if(cnt_3==4'd9 && cnt_2==4'd9 && cnt_1==4'd9)//计数到999 begin cnt_1<=4'd0; cnt_2<=4'd0; cnt_3<=4'd0; cnt_4<=cnt_4+4'd1;//千位加1 end else if(cnt_2==4'd9 && cnt_1==4'd9)//计数到99 begin cnt_1<=4'd0; cnt_2<=4'd0; cnt_3<=cnt_3+4'd1;//百位加1 cnt_4<=cnt_4; end else if(cnt_1==4'd9)//计数到9 begin cnt_1<=4'd0; cnt_2<=cnt_2+4'd1;//十位加1 cnt_3<=cnt_3; cnt_4<=cnt_4; end else begin cnt_1<=cnt_1+4'd1;//个位加1 cnt_2<=cnt_2; cnt_3<=cnt_3; cnt_4<=cnt_4; end always@(latch) if(latch)//锁存信号 begin//将计数器锁存 data1<=cnt_1; data2<=cnt_2; data3<=cnt_3; data4<=cnt_4; end endmodule

源代码

扫描文章末尾的公众号二维码

5271

5271

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?