名称:时钟设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

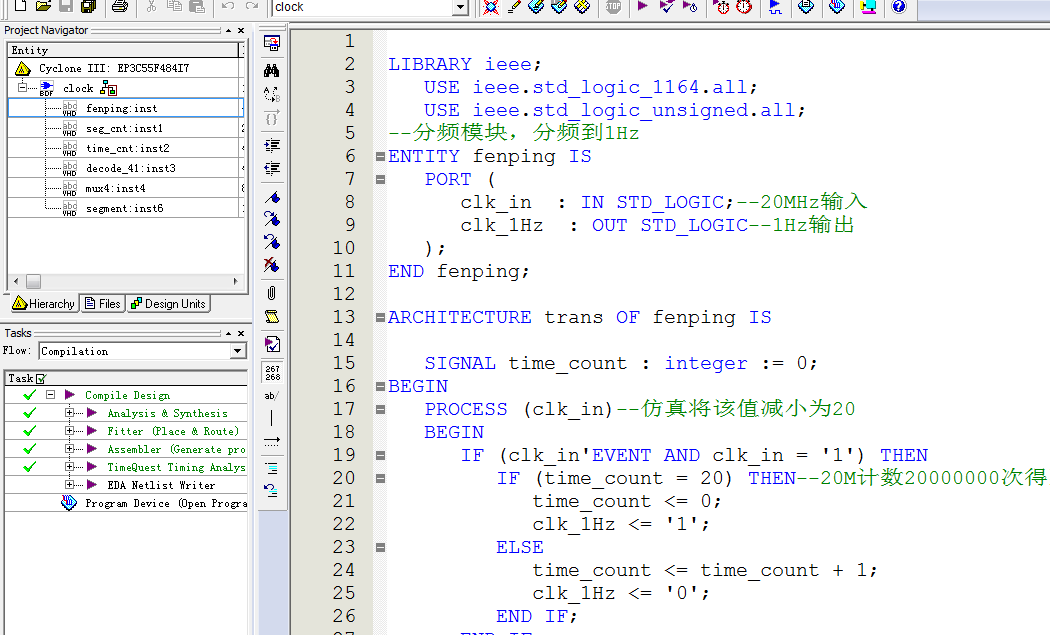

语言:VHDL

代码功能:

时钟设计

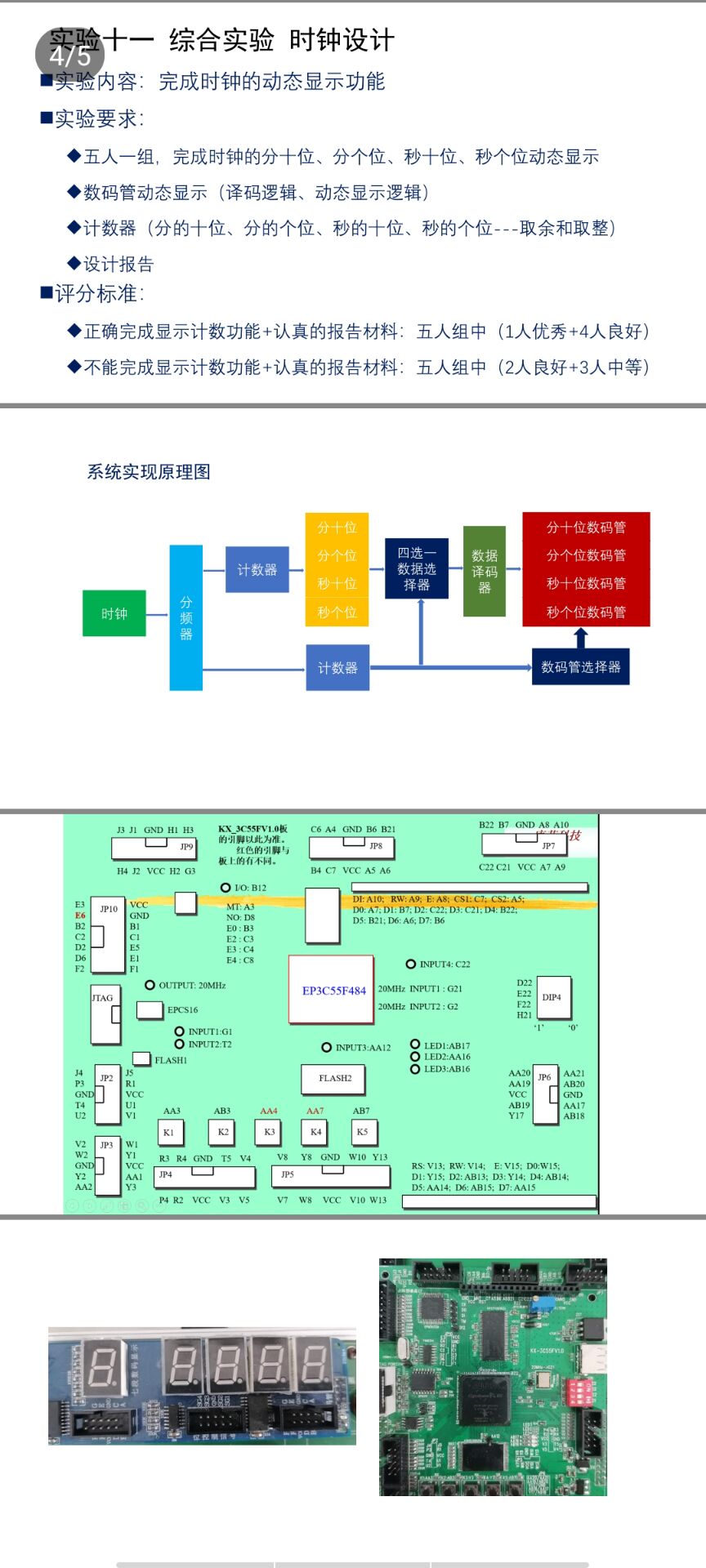

实验内容 完成时钟的动态显示功能

■实验要求

◆五人一组,完成时钟的分十位、分个位、秒十位、秒个位动态显示

◆数码管动态显示(译码逻辑、动态显示逻辑)

◆计数器(分的十位、分的个位、秒的十位、秒的个位--取余和取整)

◆设计报告

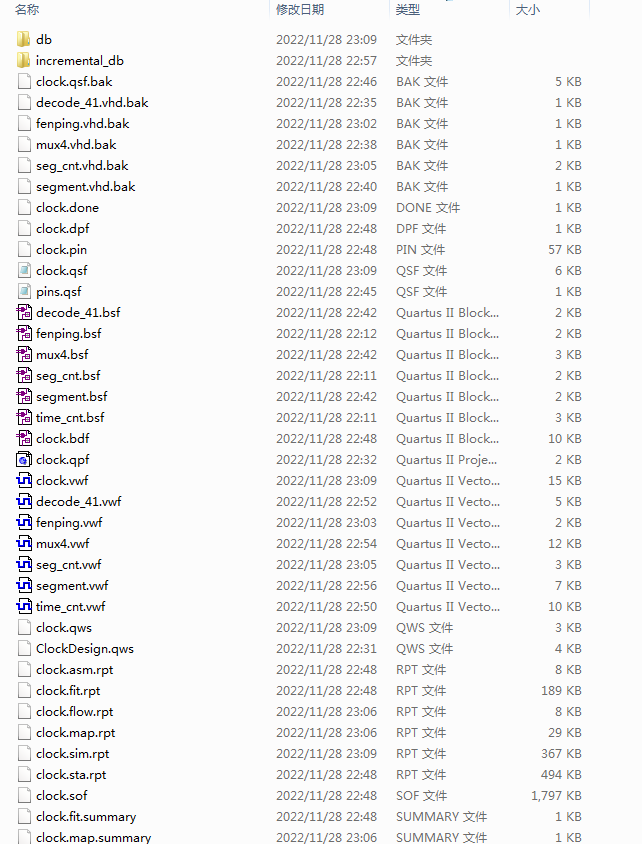

1. 工程文件

2. 程序文件

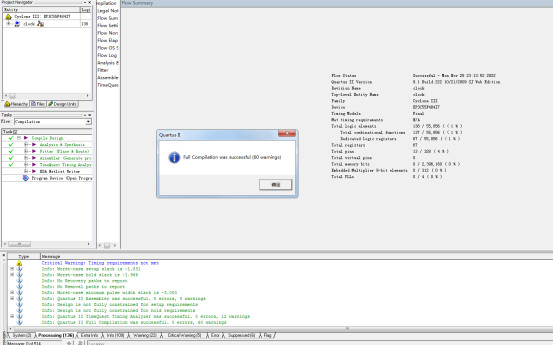

3. 程序编译

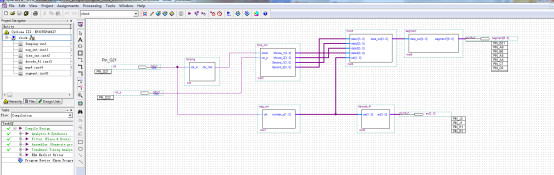

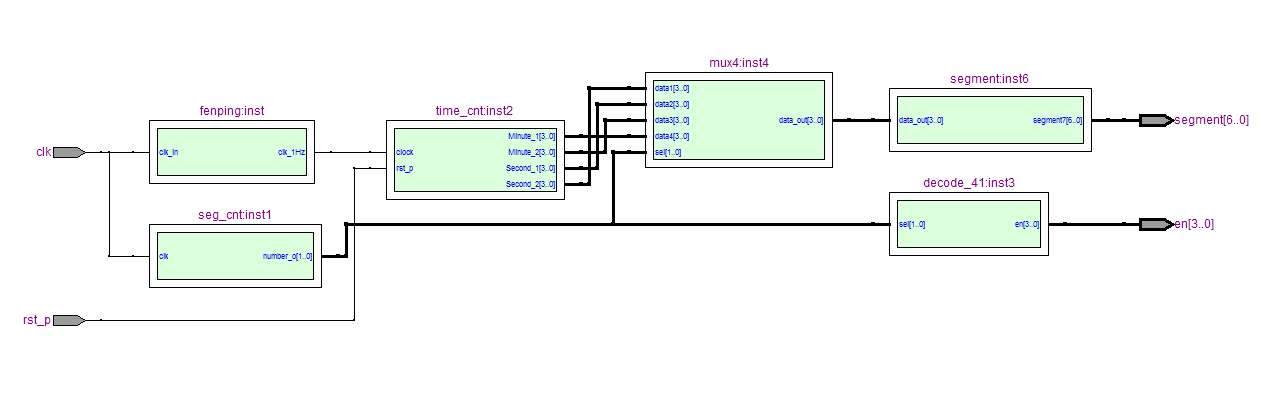

4. RTL图

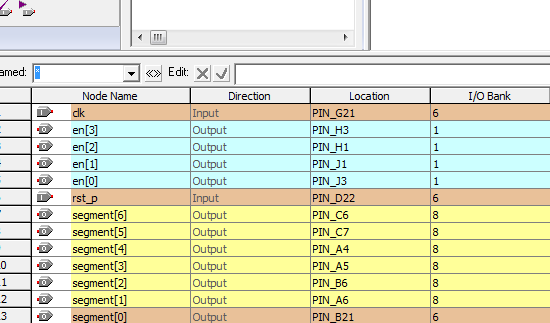

5. 管脚分配

6. 仿真图

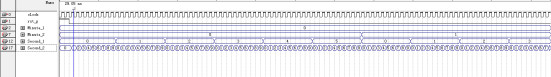

整体仿真图

分频模块

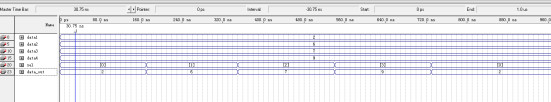

数码管计数器模块

2-4译码器模块

4选1模块

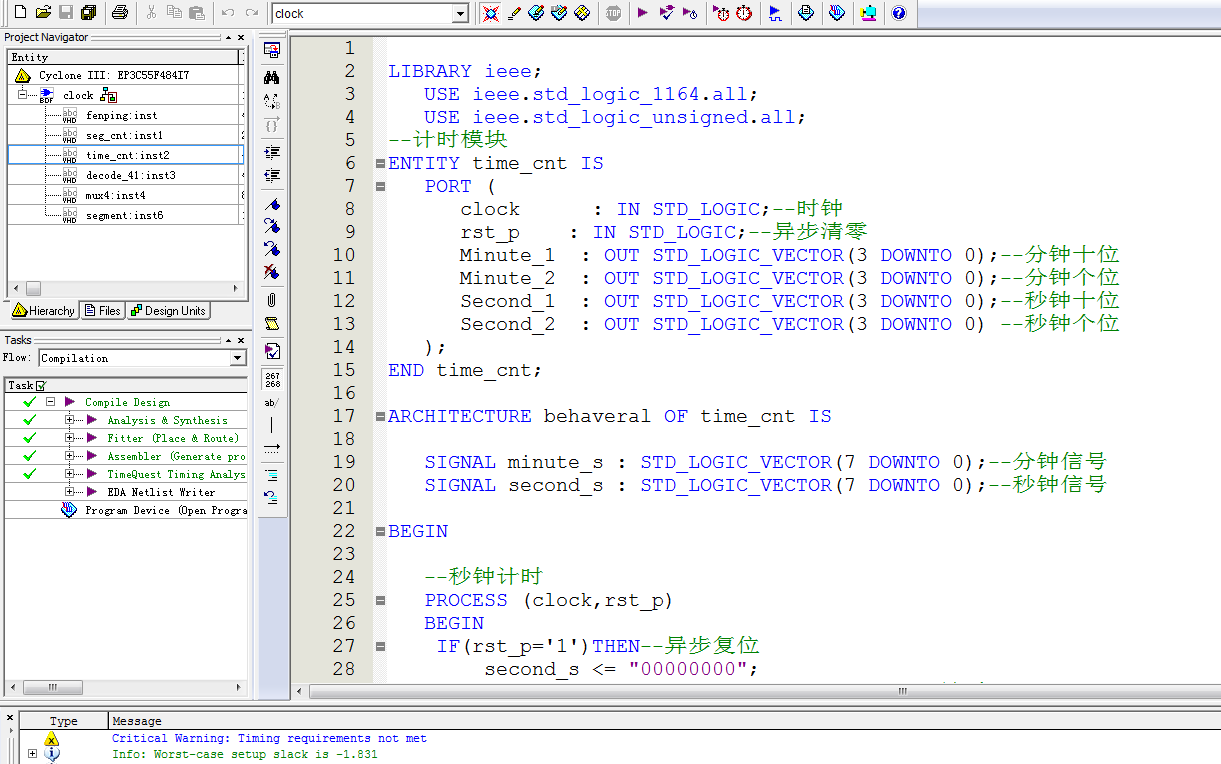

分秒计数器模块(计时模块)

数码管译码模块

部分代码展示:

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; --译码器 ENTITY decode_41 IS PORT( sel : IN STD_LOGIC_VECTOR(1 DOWNTO 0) ;--输入2位 en : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--输出4位 ) ; END ENTITY decode_41 ; ARCHITECTURE behav OF decode_41 IS BEGIN PROCESS (sel) BEGIN CASE sel(1 DOWNTO 0) IS WHEN "00"=> en<="1000";--0 WHEN "01"=> en<="0100";--1 WHEN "10"=> en<="0010";--2 WHEN "11"=> en<="0001";--3 WHEN OTHERS => NULL ; END CASE ; END PROCESS ; END ARCHITECTURE behav ;

源代码

点击下方的公众号卡片获取

6298

6298

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?