背景介绍:我们在进行高压设计时,对爬电距离和电气间距都会有严格的要求,但是传统的间距约束只能检查电气间距,无法判断爬电距离。为了提高高压设计的可靠性,Allegro X PCB设计工具的Constraint Manager中增加了高压设计检查规则,实现了对高压物体爬电距离的检查。

下面我们就开始分享具体的操作步骤:

- 高压约束设置

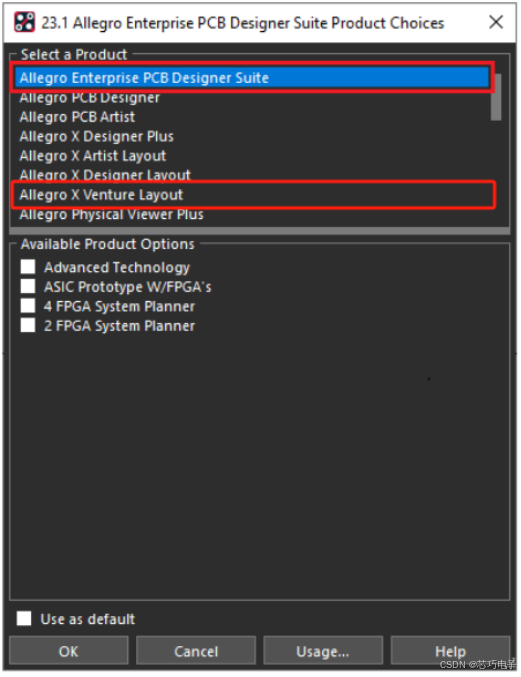

步骤一:使用Allegro PCB Editor打开PCB文件时,Product选择“Allegro Enterprise PCB Designer Suite“或“Allegro X Venture Layout”,点击“OK”,如图1所示。

图1 选择Product

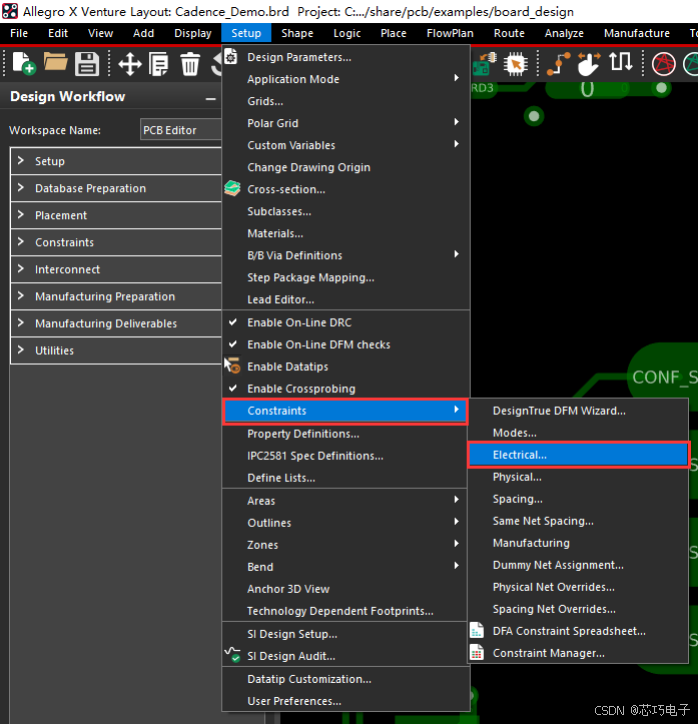

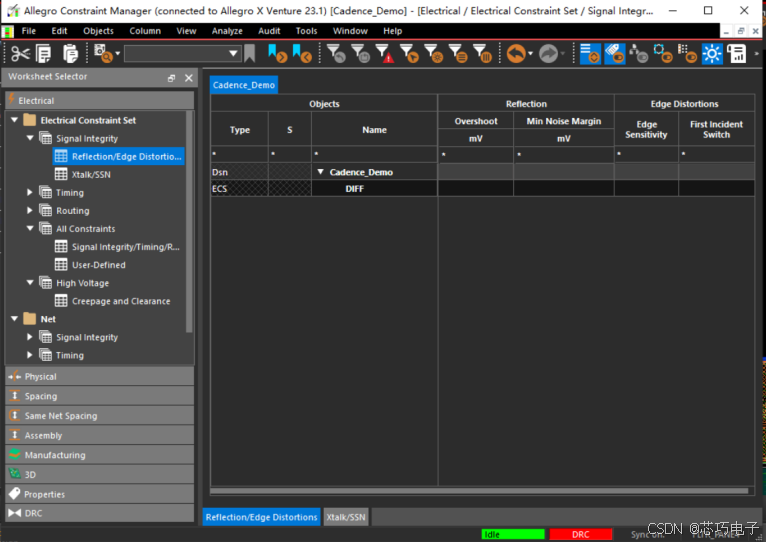

步骤二:在菜单栏中依次点击【Setup】→【Constraints】→【Electrical…】,打开Constraint Manager界面,如图2和3所示。

图2 选择“Electrical…”菜单

图3打开Constraint Manager界面

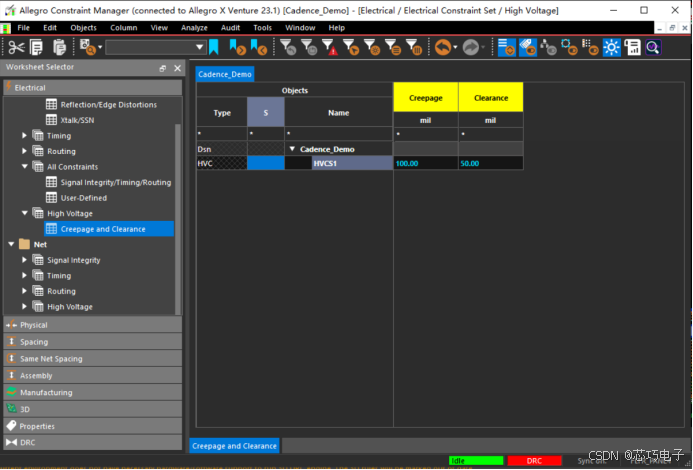

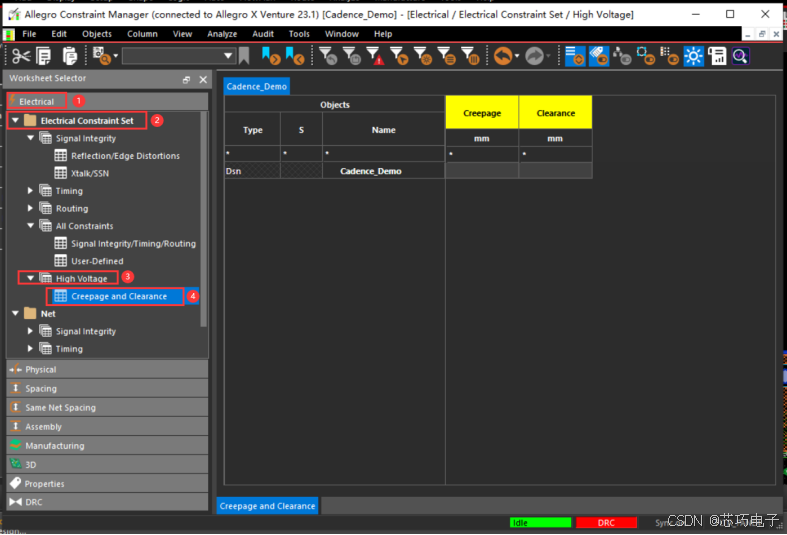

步骤三:在Electrical下依次选择“Electrical Constraint Set”-“High Voltage”-“Creepage and Clearance”,进入高压设计约束集配置界面,如图4所示。

图4 高压设计约束集配置界面

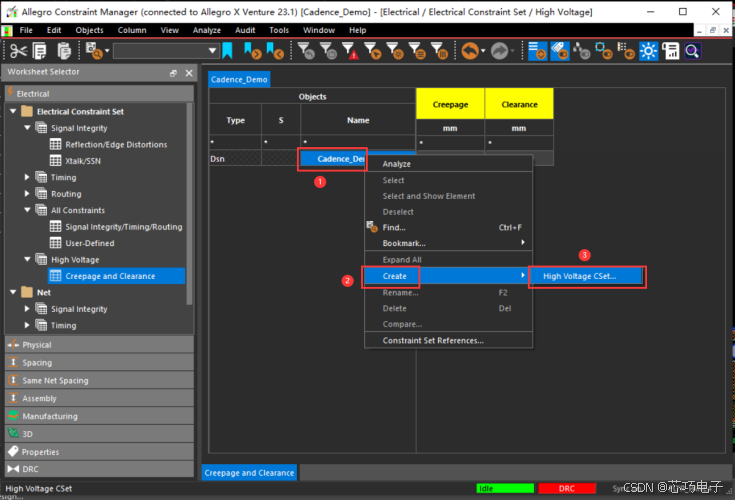

步骤四:在右侧界面选中设计,然后右键菜单选择“Create”-“High Voltage CSet”,如图5所示。

图5 创建High Voltage Cset

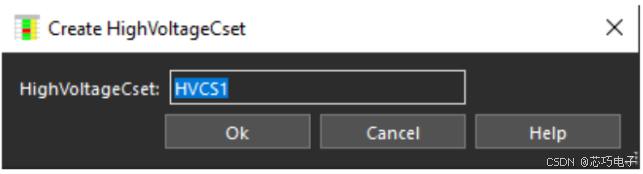

步骤五:在Create HighVoltageCset窗口输入约束名称,点击“OK”,如图6所示。

图6 命名高压约束

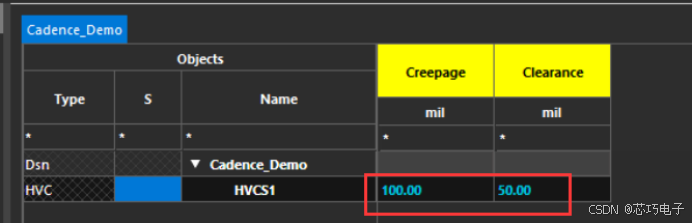

步骤六:在创建的约束规则中设置Creepage值和Clearance值,如图7所示。

图7 设置Creepage和Clearance值

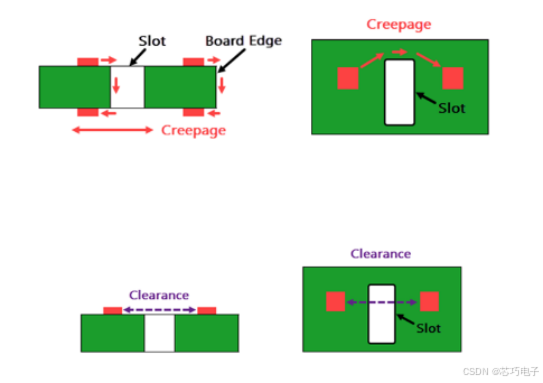

注意:其中,Clearance值是指高压物体间的空间距离,而Creepage值是指高压物体之间沿材料表面的最短距离,也叫爬电距离,如图8所示。

图8 Creepage和Clearance

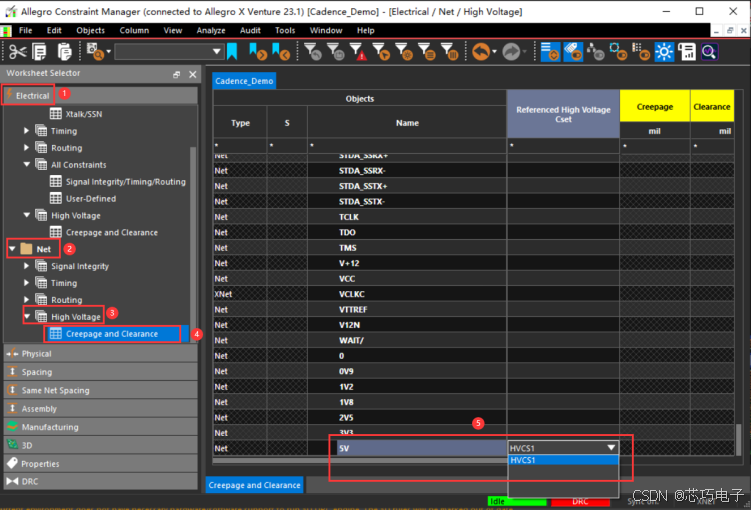

步骤七:在Electrical下依次选择”Net”-”High Voltage”-“Creepage and Clearance”,然后在右侧界面中为高压网络分配高压约束即可,如图9所示。

图9 分配高压约束

- 高压设计检查

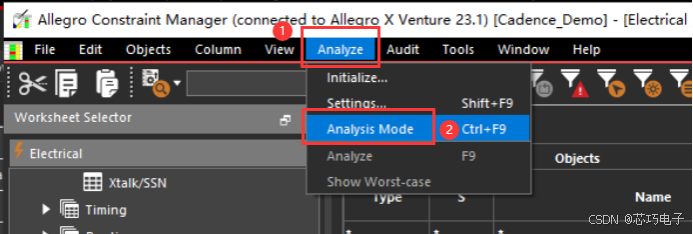

步骤一:在Constraint Manager菜单栏中依次选择【Analyze】→【Analysis Mode】或按下快捷键“Ctrl+F9”打开Analysis Modes窗口,如图10所示。

图10 打开Analysis Modes窗口

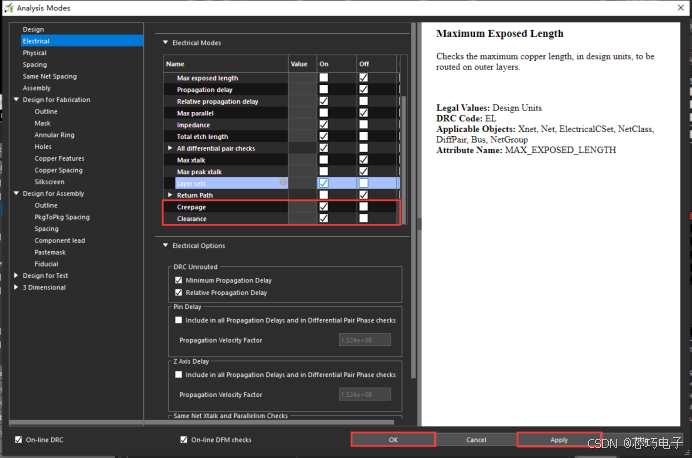

步骤二:在Analysis Modes窗口选择“Electrical”,然后勾选“Creepage”和“Clearance”后,依次点击“Apply”-“OK”,再关闭约束管理器即可,如图11所示。

图11 勾选“Creepage”和“Clearance”

步骤三:选中PCB上的CR DRC标志,运行“Show Element”命令,即可查看高压设计检查结果的报错信息,如图12所示。

图12 查看高压设计检查报错信息

步骤四:根据报错信息,可以通过添加或修改挖空区域、添加或修改Slot等方法来调整爬电距离,通过移动器件等方法来调整电气间距,调整完成后,高压设计检查报错就会消失,如图13所示。

图13 消除高压设计检查报错信息

- 小结

本节主要介绍了在Allegro X PCB设计工具中,如何使用高压设计检查功能,对印制板上高压物体的爬电间距和电气间距进行检查,避免导电元件之间不必要的放电,使设计符合高压设计标准和安全规范。

501

501

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?