Verilog 與 C

語言的運算子大同小異,

例如:C = A + B ; A = A + 1;

例如:C = A + B ; A = A + 1;

但是在加法中Verilog沒有遞增、遞減運算子

例如:for( i =0 ; i < 5 ; i++) ←此在C是正確

不過在Verilog沒有 i++ (亦無 i += 1)的運算,

需以 i = i + 1 表示。

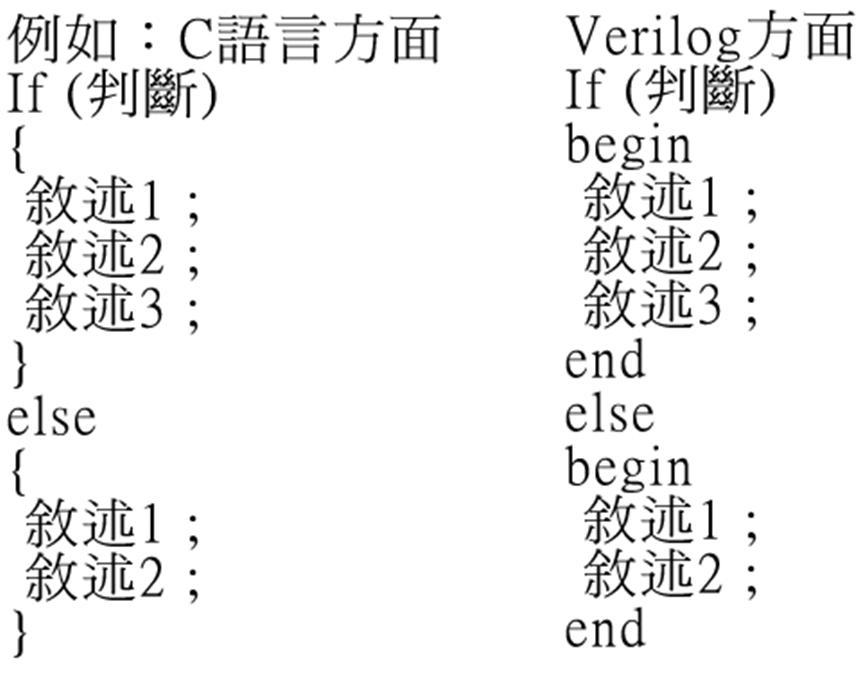

在判斷式:if,else,在用法上也是一樣的,

只是在敘述超過兩行以上所使用的範圍→{ },

在Verilog卻是以begin與end表示之。

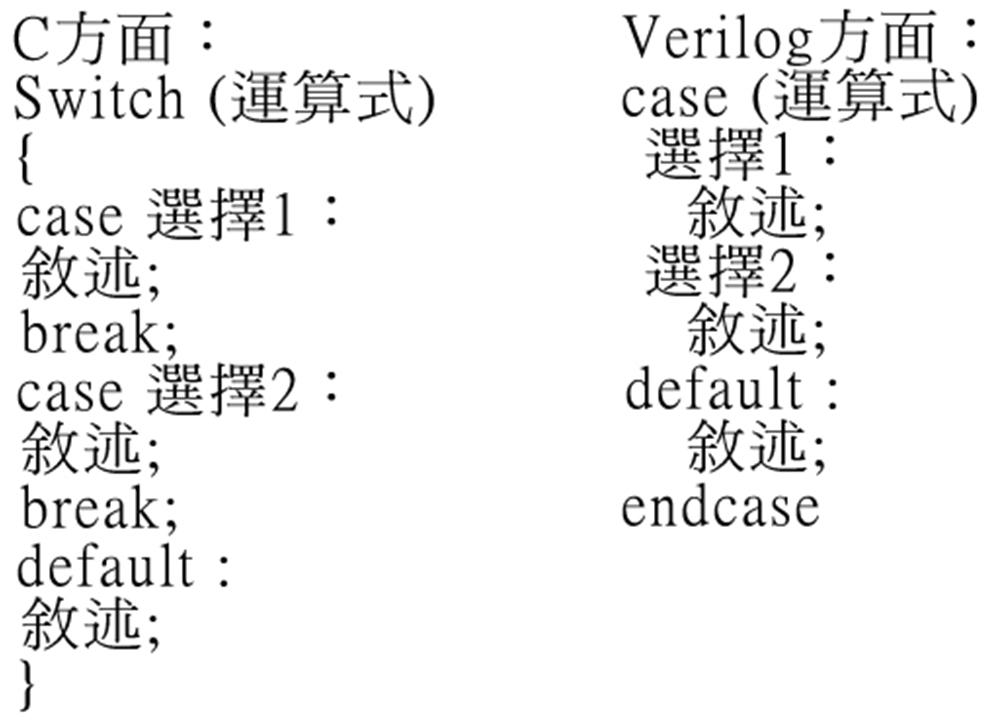

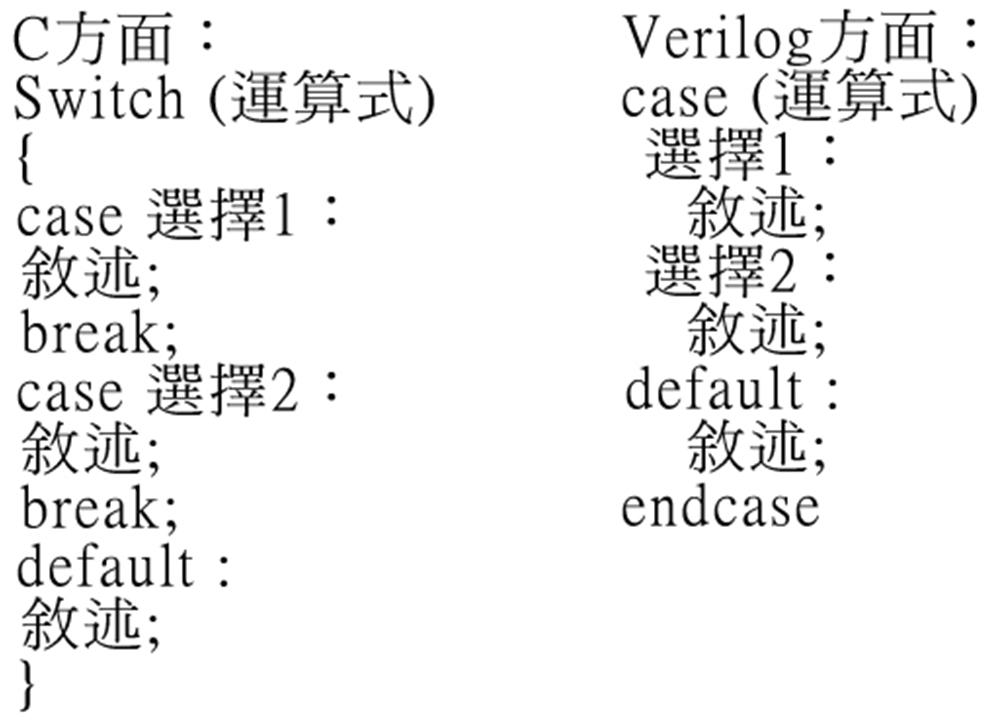

在多重選擇方面,Verilog與C

也不盡相同。

同樣的,超過一個敘述以上仍需加上begin end。

同樣的,超過一個敘述以上仍需加上begin end。

9628

9628

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?