【懂得都懂】学弟学妹们理性参考,不要照抄。

一、实验目的与实验仪器(5%)

1.1 实验目的

- 拓展专业知识,了解器件发展趋势;

- 深入掌握半导体器件仿真工具的使用方法与器件建模仿真流程;

- 了解结构参数对晶体管器件特性的影响。理论联系实际,在仿真中深刻领会 课堂所学相关内容并能举一反三,提出设计或优化的方法。

1.2 实验仪器

基于silvcao TCAD仿真平台探究SOI技术构建Bipolar Junction Transistor 的各项指标。

二、实验原理分析(10%)

2.1 双极性晶体管Bipolar Junction Transistor

BJT(Bipolar Junction Transistor,双极晶体管)是一种半导体器件,是现代电子电路中最基本、应用最广泛的三层异质结器件之一。BJT主要由两种不同类型的半导体材料(通常是N型和P型)构成,它有三个区域:发射区、基区和集电区。

(1)结构:

BJT由两个不同类型的半导体材料(N型和P型)组成的三层结构。有两种主要类型的BJT:NPN型和PNP型。

发射区、基区和集电区: 三个区域分别对应于不同的半导体材料,其中发射区主要负责电子注入,基区用于控制电子注入,而集电区用于收集电子。

(2) 工作原理:

NPN型和PNP型: NPN型BJT中,电子是主要载流子,而PNP型BJT中,空穴是主要载流子。在NPN型中,电流流动从发射区到集电区,而在PNP型中,电流流动方向相反。

放大功能: BJT可用作放大器,其工作原理基于电流控制电流的原理。微小的输入电流可以控制大电流的输出,使得BJT在电子设备中起到放大信号的作用。

(3)应用领域:

放大器: BJT广泛应用于放大器电路,如放大音频信号、射频信号等。

开关: BJT也可用作开关,通过控制基区电流来控制集电区的电流,实现开关电路的功能。

振荡器: 在振荡器电路中,BJT可以用于产生振荡信号。

数字电路: 虽然现代数字电路主要依赖于场效应晶体管(FET),但BJT仍然在某些数字电路中使用。

(4) 特性:

非线性特性: BJT的输入-输出特性是非线性的,这使得它在某些应用中比场效应晶体管更适用。

温度敏感: BJT对温度变化敏感,这需要在设计电路时考虑温度补偿和稳定性。

2.2 SOI横向器件

(1)SOI结构的优势?基本工艺流程?发展方向?

1.SOI结构优势:

<1 减小了寄生电容,提高了运行速度。与体硅材料相比,SOI 器件的运行速度提高了20-35%;

<2 具有更低的功耗。由于减少了寄生电容,降低了漏电,SOI 器件功耗可减小35-70%;

<3 消除了闩锁效应;

<4 抑制了衬底的脉冲电流干扰,减少了软错误的发生;

<5 与现有硅工艺兼容,可减少 13-20%的工序

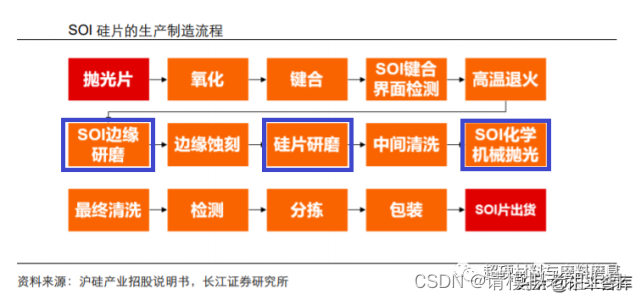

2.基本工艺流程:

图1 SOI基本工艺流程图图示

3.发展方向:

<1 FD-SOI(全耗尽型绝缘体上硅)

在汽车、物联网等领域具有很好的发展前景。

<2 RF-SOI(射频绝缘体上硅)

用于各种射频器件,是各类射频应用里主流的衬底,如射频开关、LNA、调谐器。智能耳机、手表、可穿戴设备等,而且不限于蜂窝通信,蓝牙、Wi-Fi以及超宽带UWB等无线技术背后都有其存在,而且RF-SOI还能在毫米波应用中。

(2)横向双极晶体管与平面型双极晶体管的区别?横向晶体管有何优势?

1. 横向双极晶体管与平面型双极晶体管的区别

平面晶体管是指电子在晶体管中的流动与晶体管的主电极之中平行于表面进行的器件。

优点:工艺技术成熟,生产成本低,适合大规模生产。并且在低温下使用时性能稳定,可靠性高。

缺点:

1.电阻大:因为电流流动方向与晶体管表面成45度角,电阻明显增加;

2.速度慢:纵向晶体管的漂移区域很长,电子流速度较慢;

3.发热量大:晶体管的漂移区域受到电子和芯片的热量较大,热损失较多;

4.电压降大:因为相对较大的电阻和长的漂移区域,电压降较大。

横向晶体管是指电子在晶体管中的流动与晶体管表面垂直方向进行的器件。

优点:速度快,发热量低,电阻小,电压降低。

缺点:由于其制造工艺技术相对较新,成本较高,生产周期较长,可靠性差,非常容易受到电磁干扰等问题。

2.横向晶体管的优势

平面型晶体管的制造成本较低,适合于大规模生产,但在性能方面会有所欠缺。而横向晶体管成本相对较高,但它的性能表现更加出色。

(3)是否只能在SOI结构上制作横向晶体管?原因是什么?

不一定。横向晶体管可以在不同类型的晶体管结构上制作,但SOI结构通常被认为是最适合制作横向晶体管的结构。这是因为SOI结构可以减少晶体管之间的互相干扰,从而提高晶体管的性能和可靠性。此外,SOI结构还可以提高晶体管的速度和功率效率,因为它可以减少电荷耦合和电阻效应。因此,尽管可以在其他结构上制作横向晶体管,但SOI结构仍然是最常用的。

除了SOI结构外,还可以在Bulk CMOS(大规模集成电路中常见的技术)、FinFET(三维晶体管结构)和多晶硅等结构上制作横向晶体管。每种结构都有其独特的优势和限制,因此在特定应用中可能会选择不同的结构来制作横向晶体管。

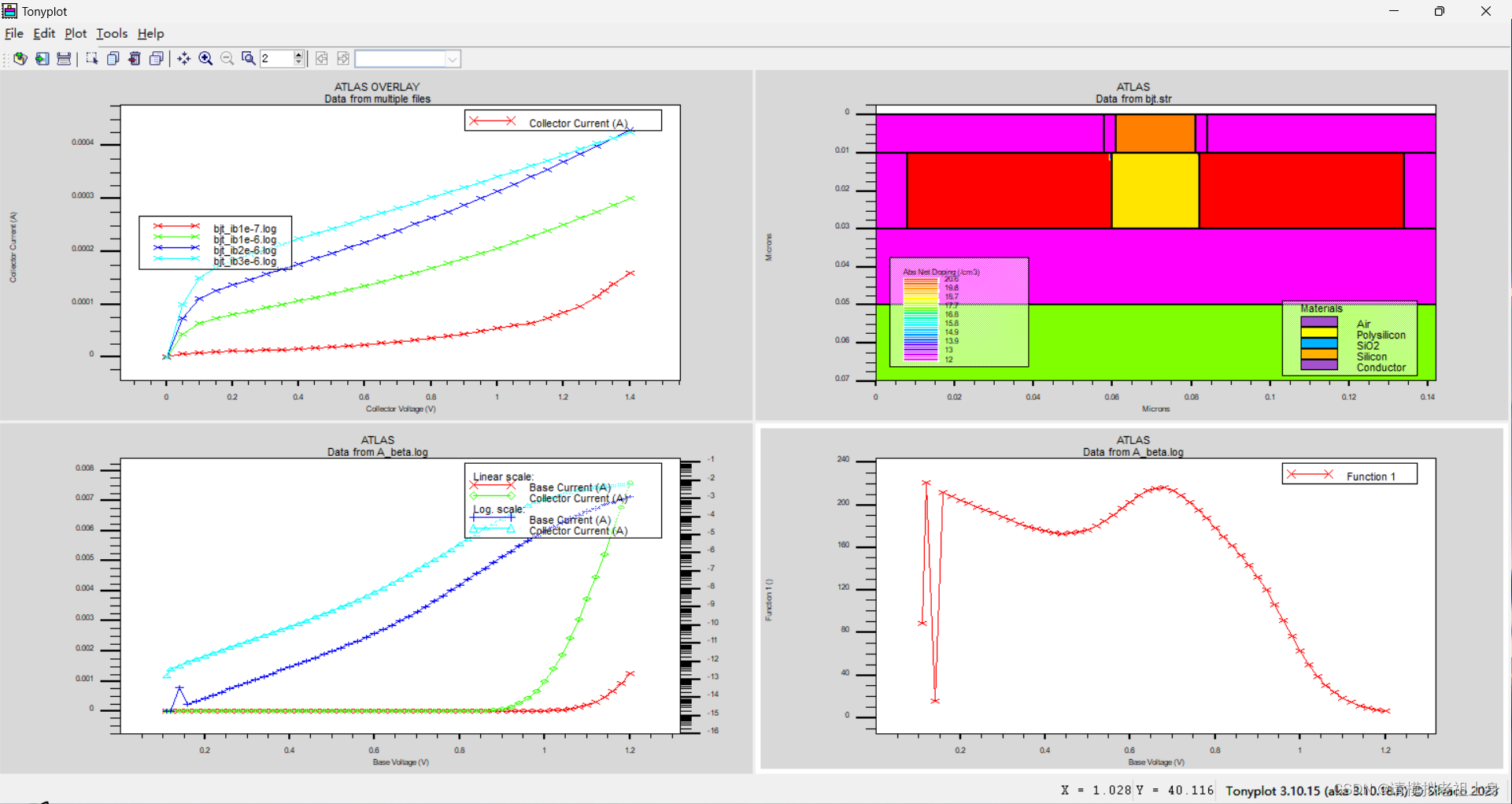

三、实验步骤(20%)

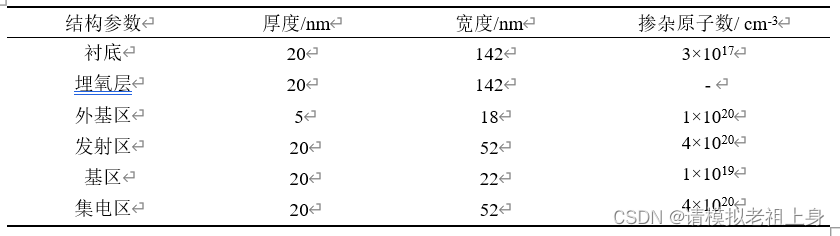

1. 明确实验参数与实验结构

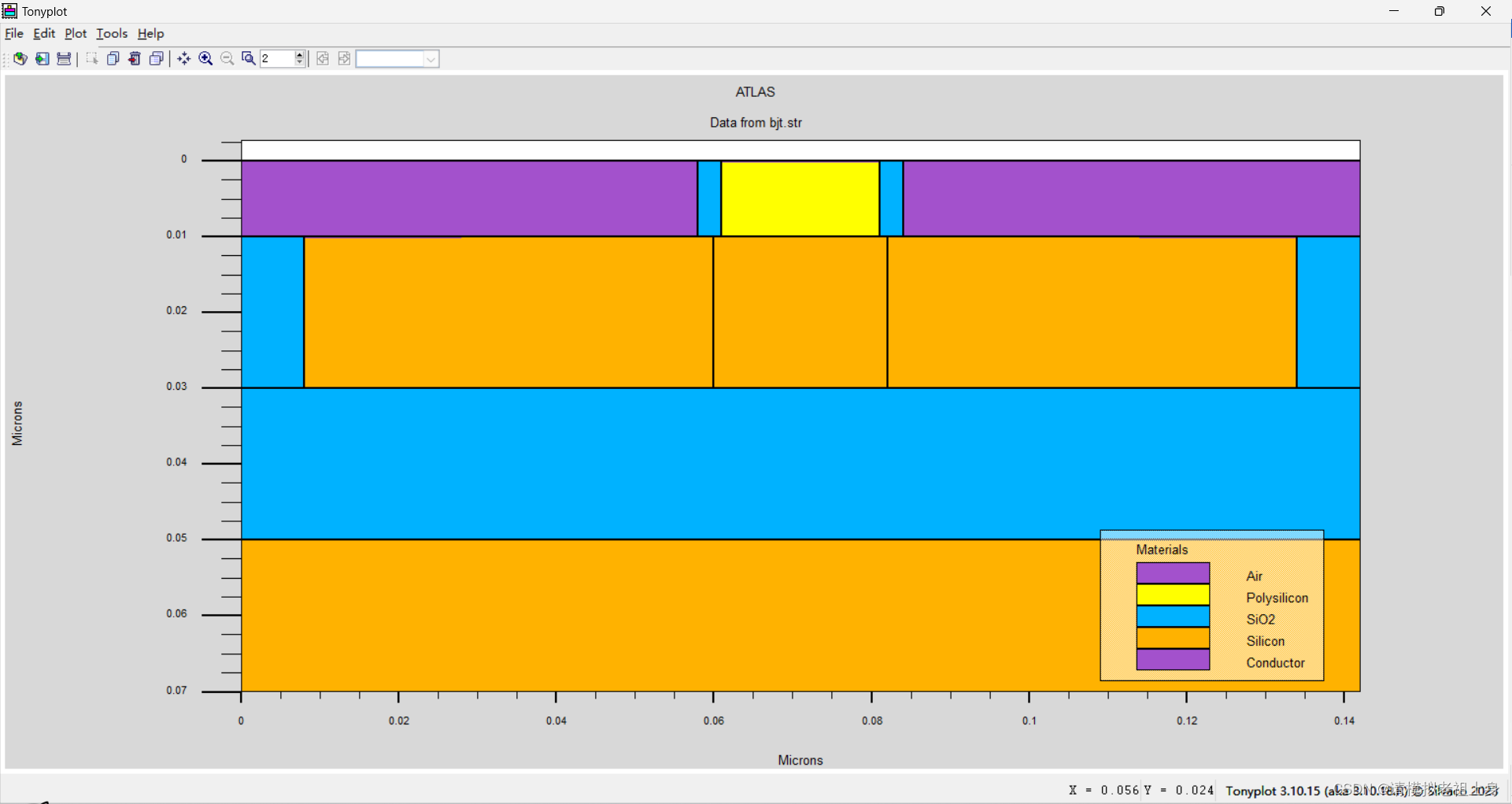

图2 SOI器件各区域参数

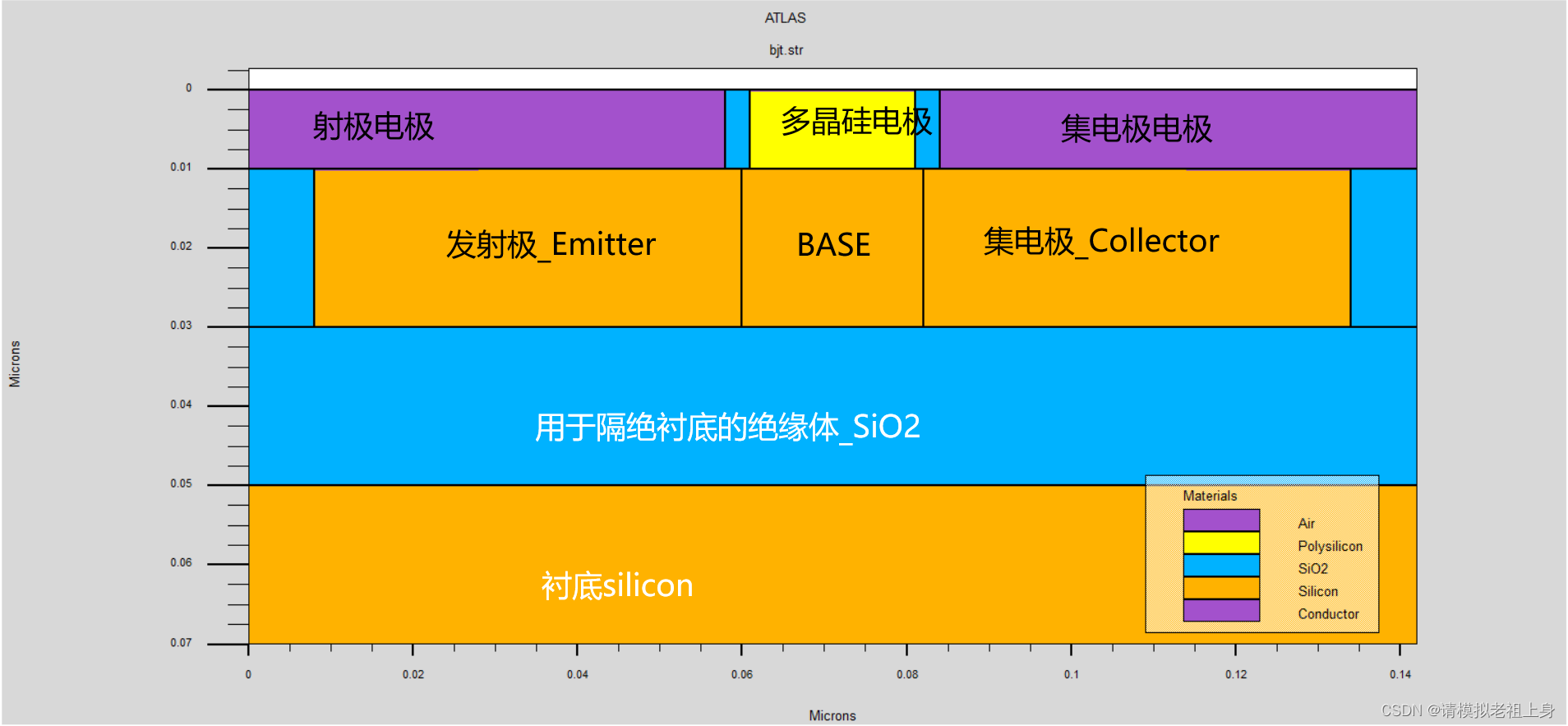

图3 SOI器件结构示意图

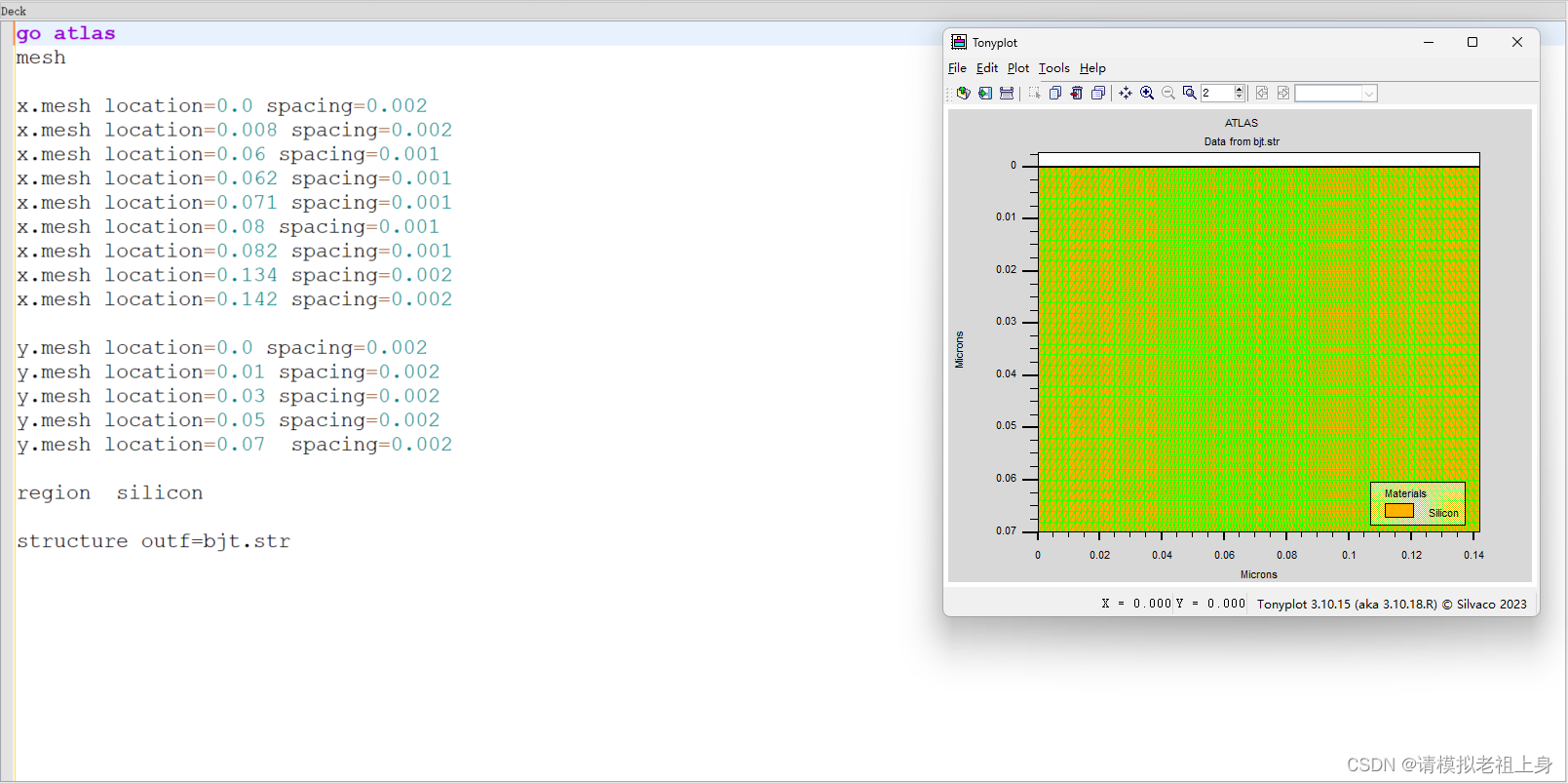

2. 建立网格(Initial Mesh)

Atlas由状态x.mesh、y.mesh及其对应的参数location和spacing来定义网格。状态mesh表明网格生成开始,参数space.mult定义网格线间距的倍乘因子,默认值是1,大于1会使网格变粗糙,仿真也相应加快。参数width可以定义器件在Z轴方向的长度。

网格必须考虑疏密程度,材料界面、很薄的材料层都需要定义的密集一些。衬底可以定义的稀疏一些。基本原则是在location附近参数变化显著。

图4 网格建立代码与密度图示

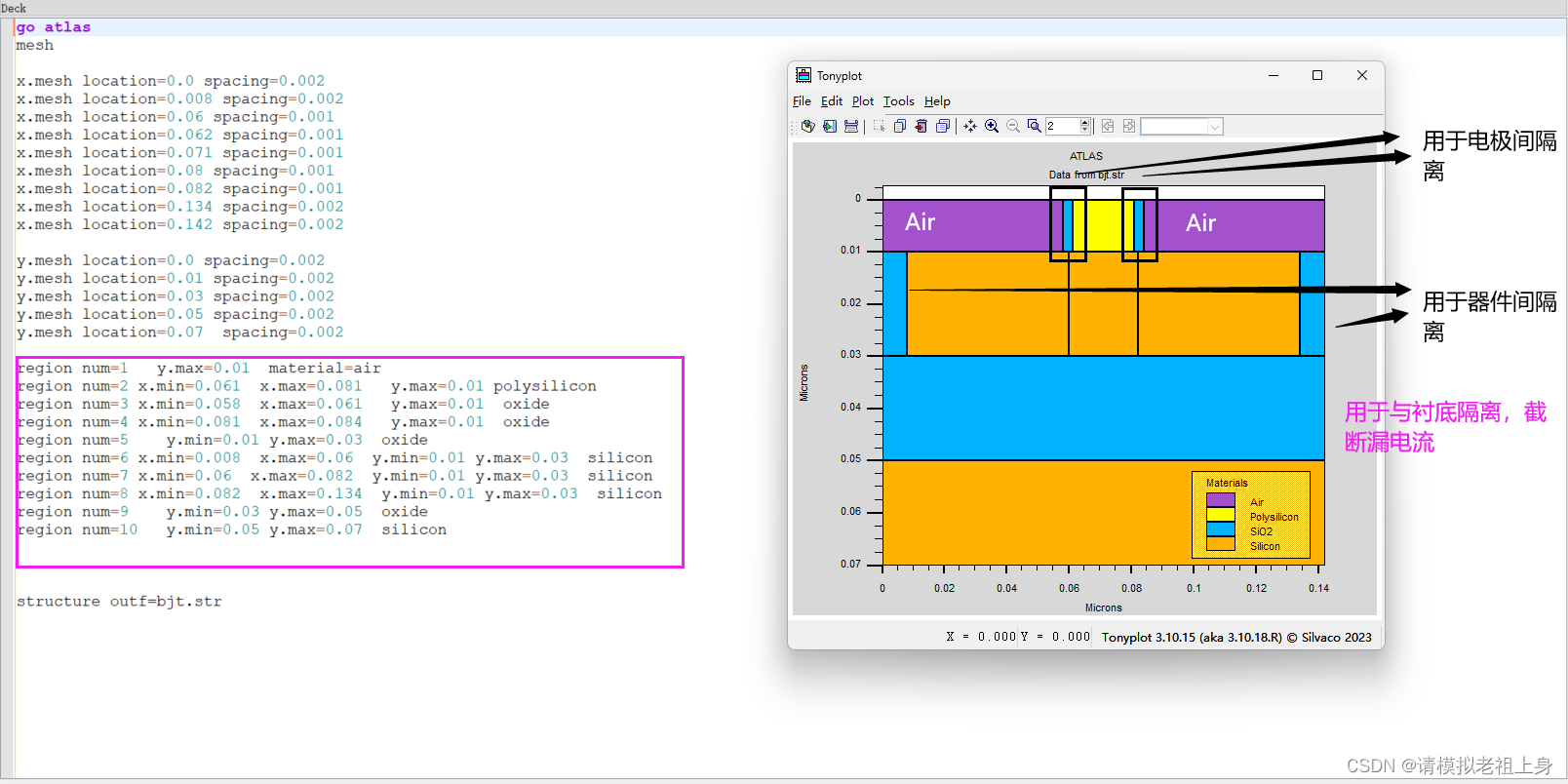

3. 区域材料定义(Region and Materials)

ATLAS的器件剖面可以按需要分成不同区域,然后定义区域的特性。定义区域需要指明位置(X和Y的范围)、材料以及序号,在后续掺杂时可以按区域定义。

Region语法:

REGION NUMBER=<N><MATERIAL>[<POSITION>]

应当使mesh范围全部都有region定义,实在没有材料可以将material设置为air。

ATLAS有两种方法可以定义区域中材料组分的渐变:

- 用compx.top和compx.bottom参数来定义区域顶部和底部的组分,中间区域组分是线性变化的。

- 由参数grad.<n>定义在某一区间内组分由某一值减少为0。

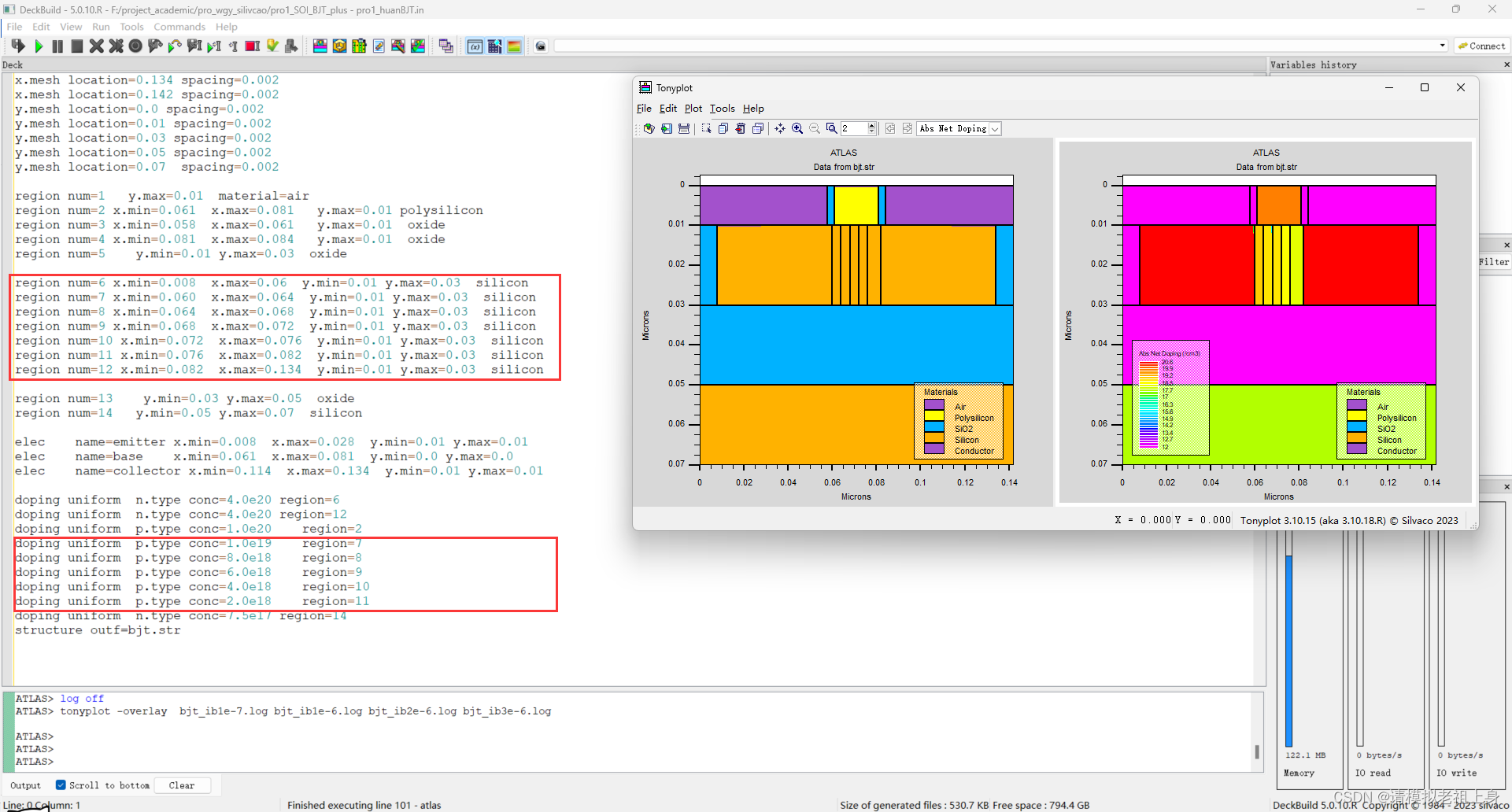

图5 区域材料定义代码与结构展示

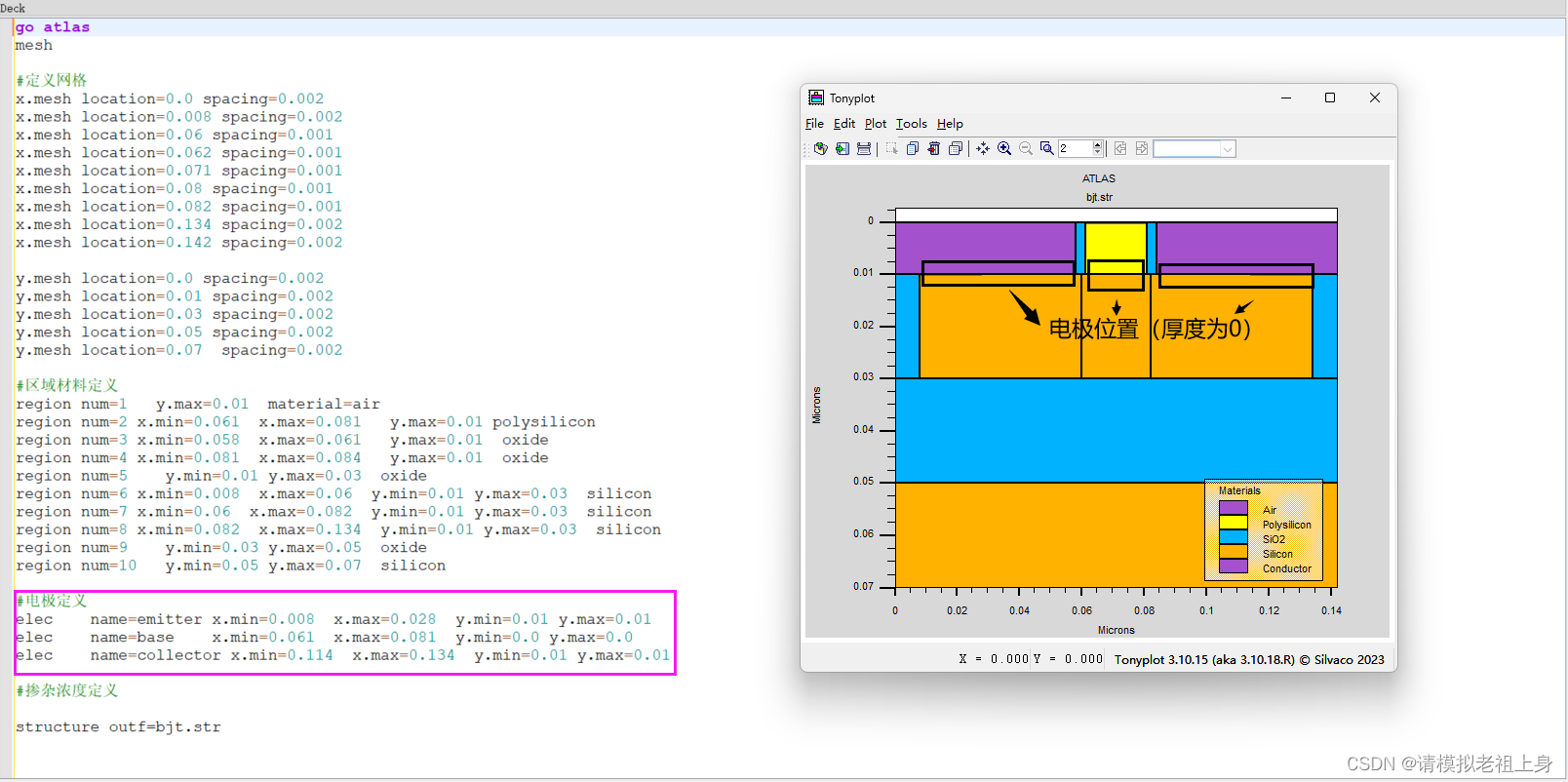

4. 电极定义(Electrode)

Electrode定义电极,位置可以是由x.min、x.max、y.min、y.max组成的矩形框,也可以是按照剖面的特定位置如top、bottom、left、right或substrate定义,还可以是指定一点和电极在X方向的长度来定义。电极接触类型默认为欧姆接触。

Electrode用法:

ELECTRODE NAME=<C>[SUBSTRATE]<POSITION><REGION>

图6 电极定义代码与结构展示

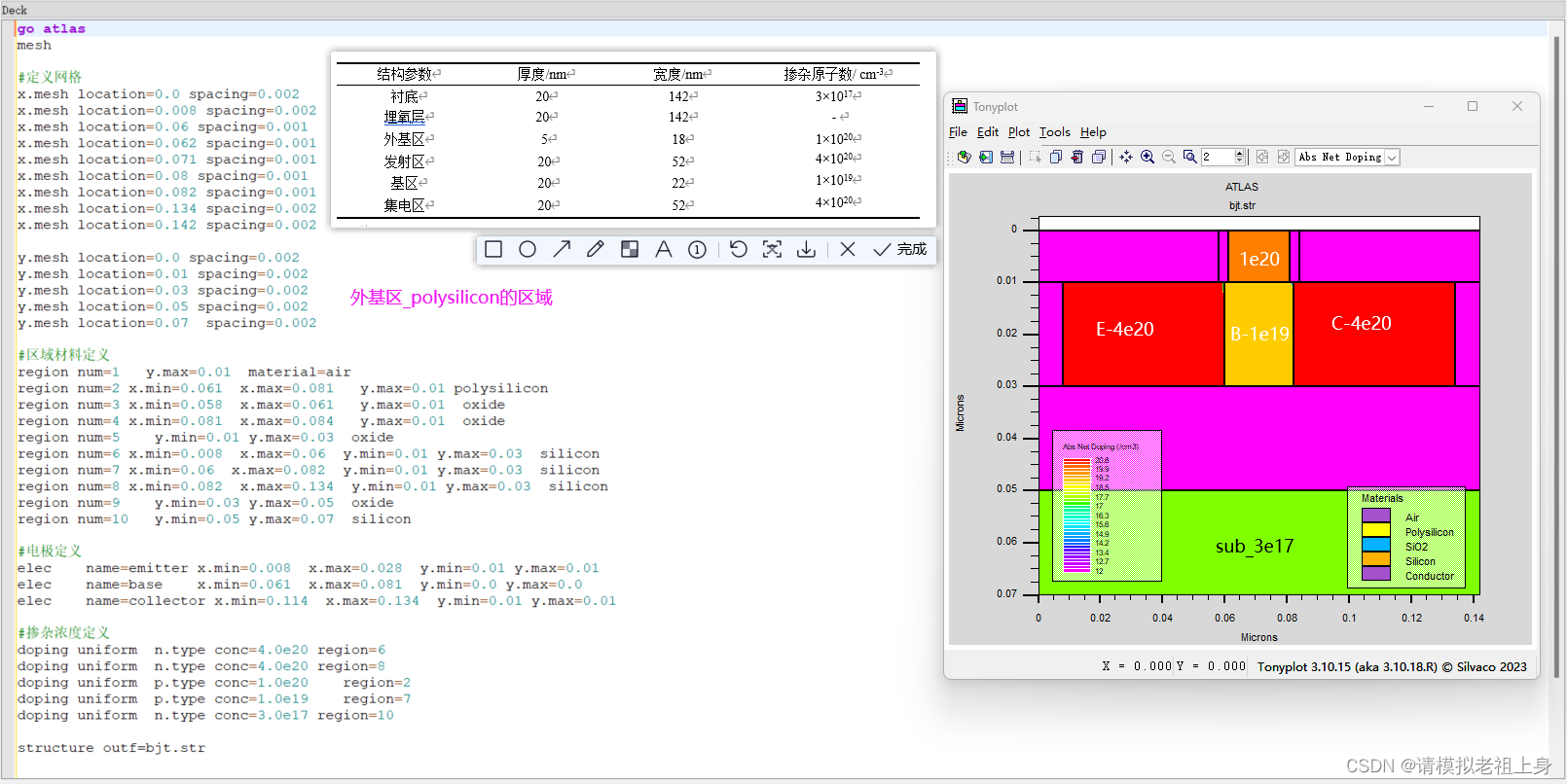

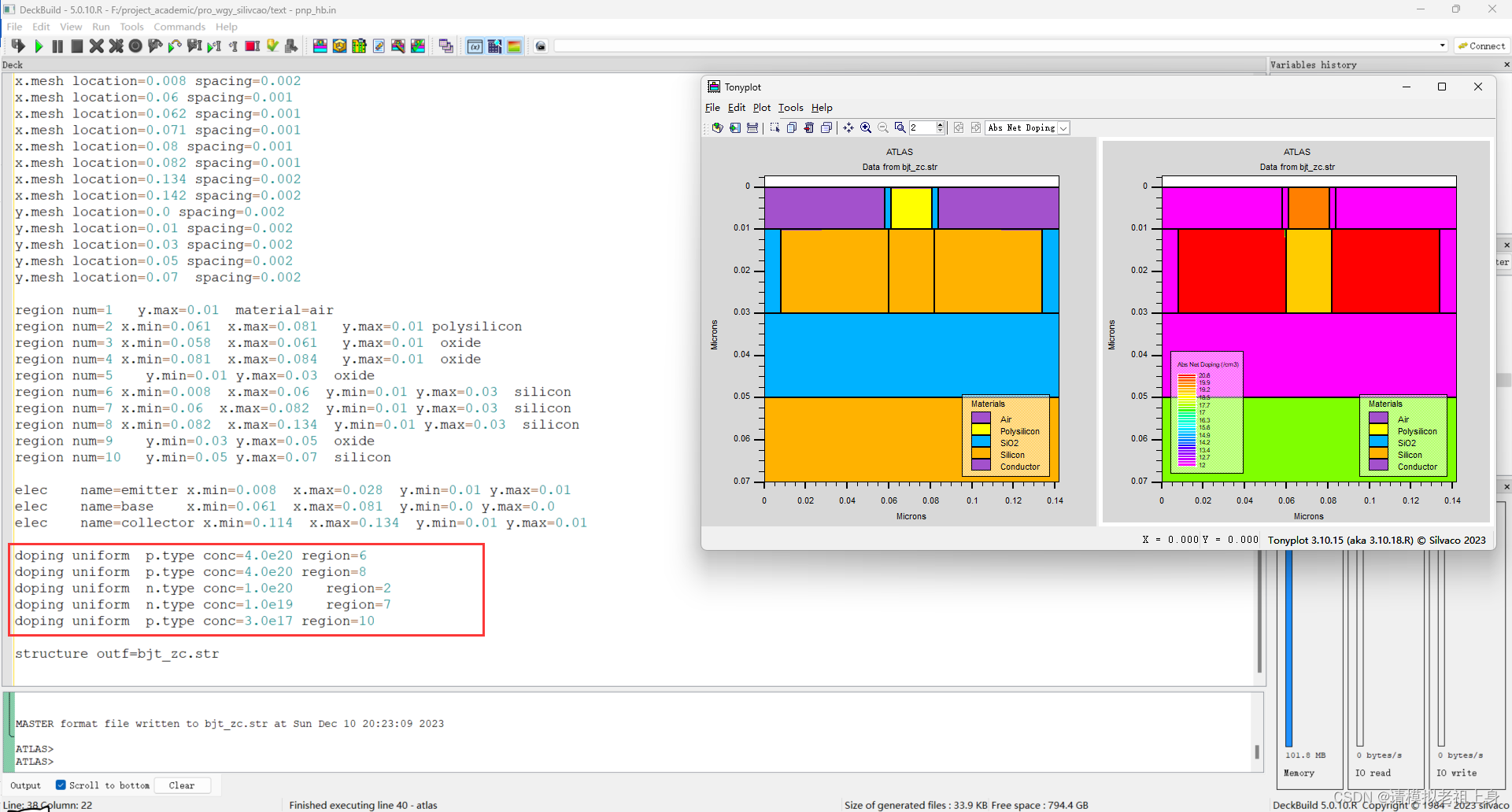

5. 掺杂浓度定义(Doping)

杂质分布由doping状态设置,doping语法格式如下:

DIOING<DISTRIBUTION_TYPE><DOPANT_TYPE><POSITION_PARAMETERS>

杂质分布可以是均匀(uniform)、高斯(Gaussian)和余误差函数(error function)分布。

均匀分布常用的参数有杂质类型(n.type或p.type)、浓度(concentration)和区域(region)。

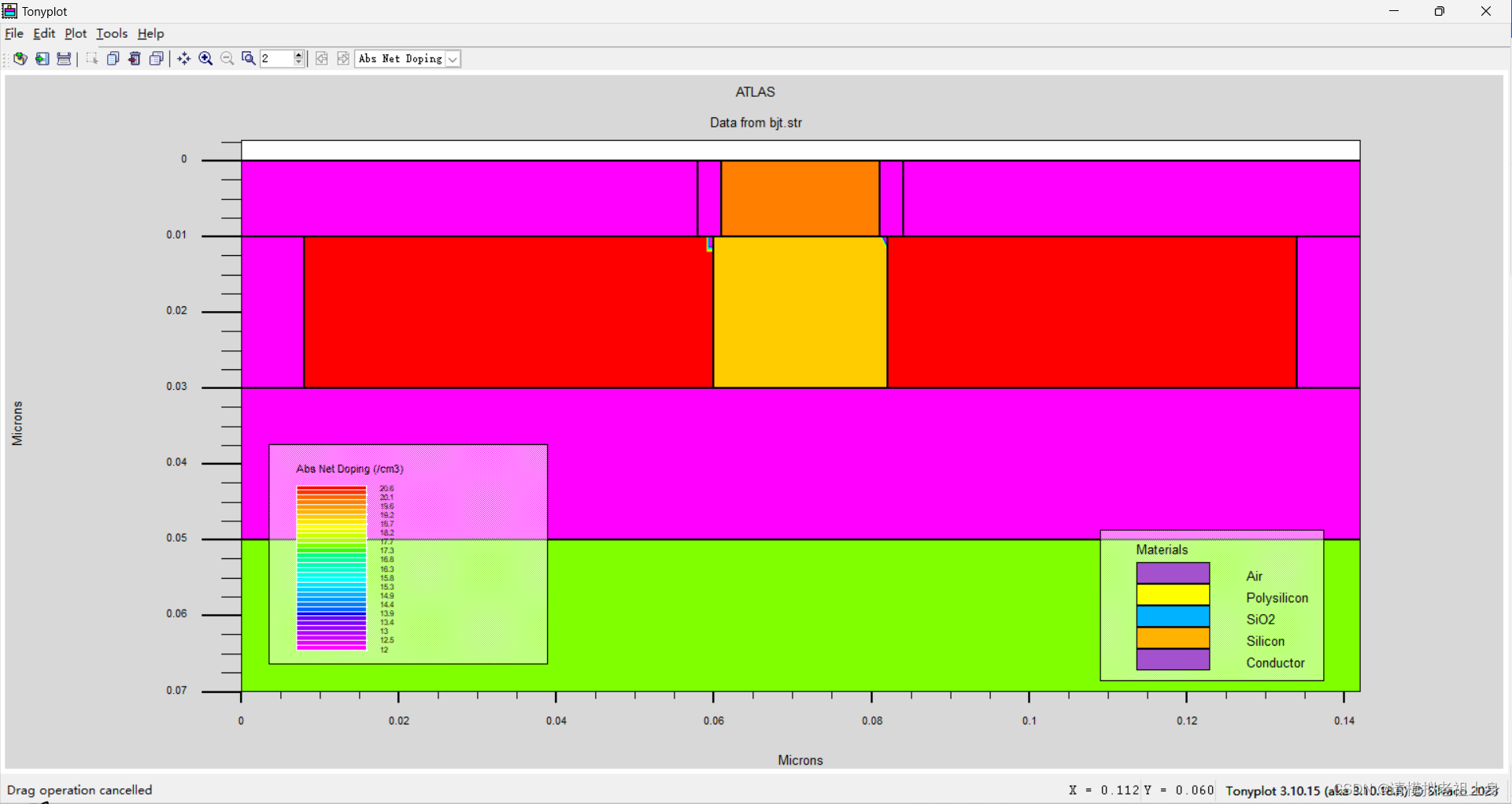

图7 掺杂浓度定义代码与结构展示

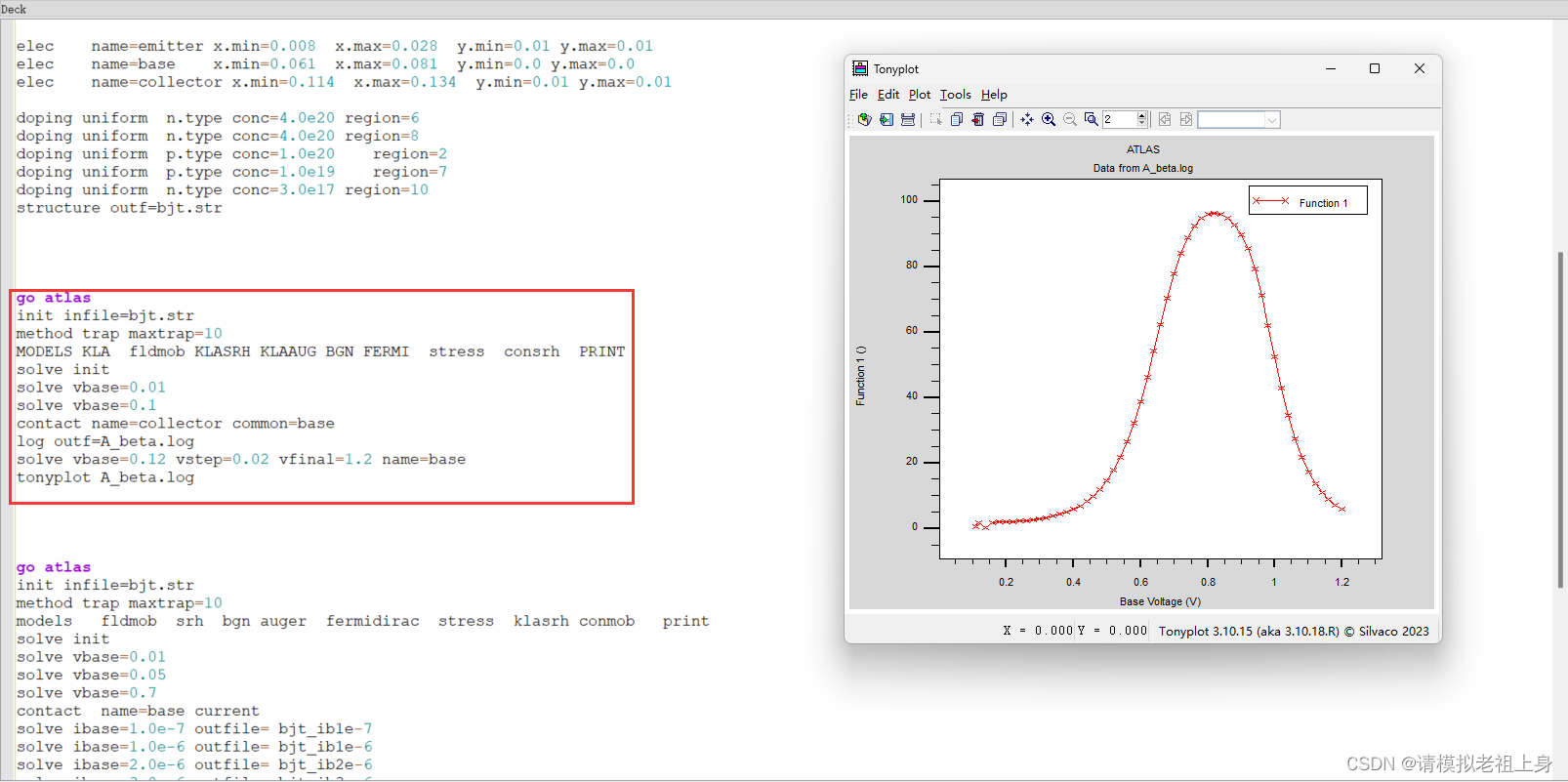

6. 输出共射级电流增益

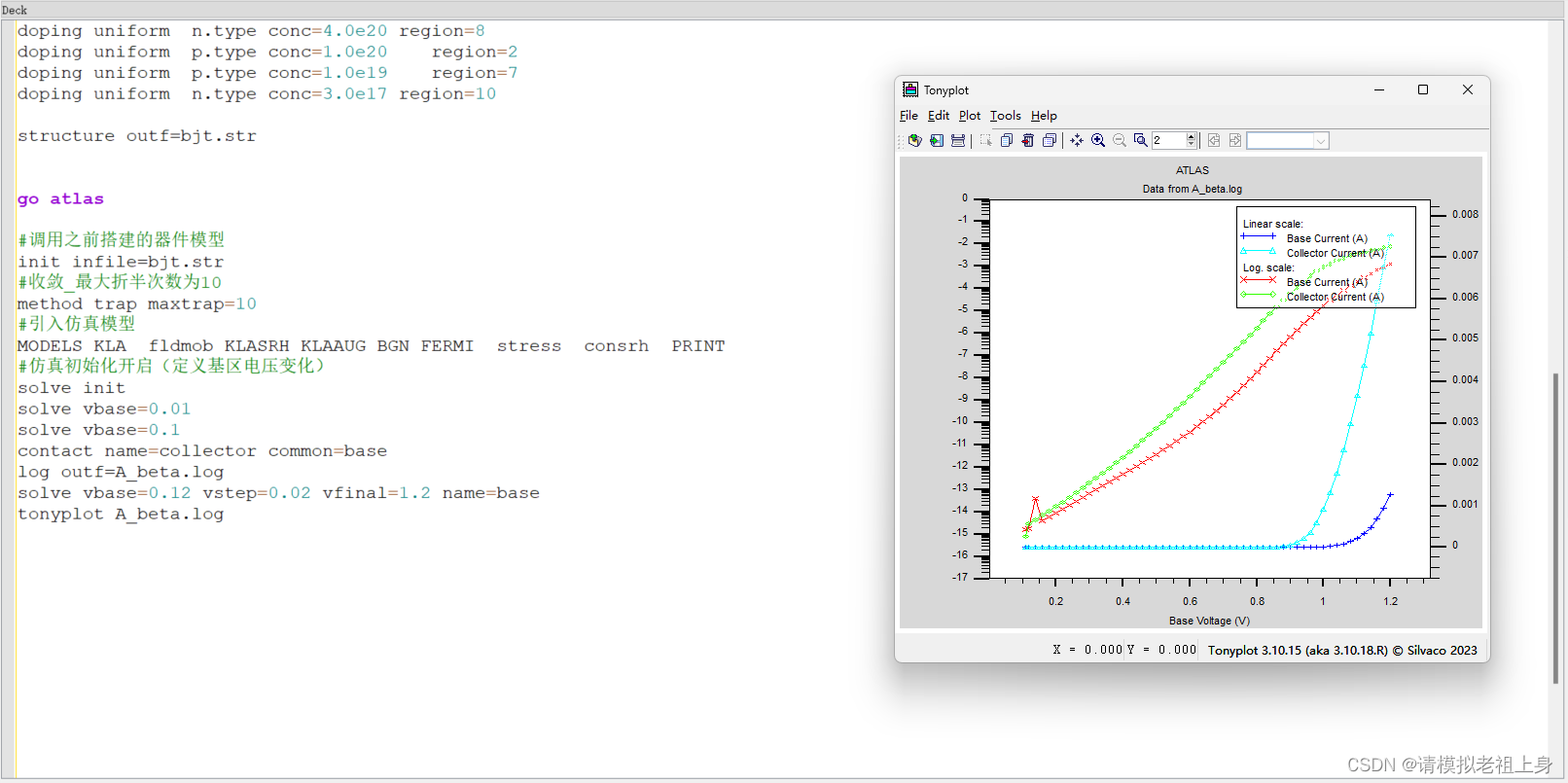

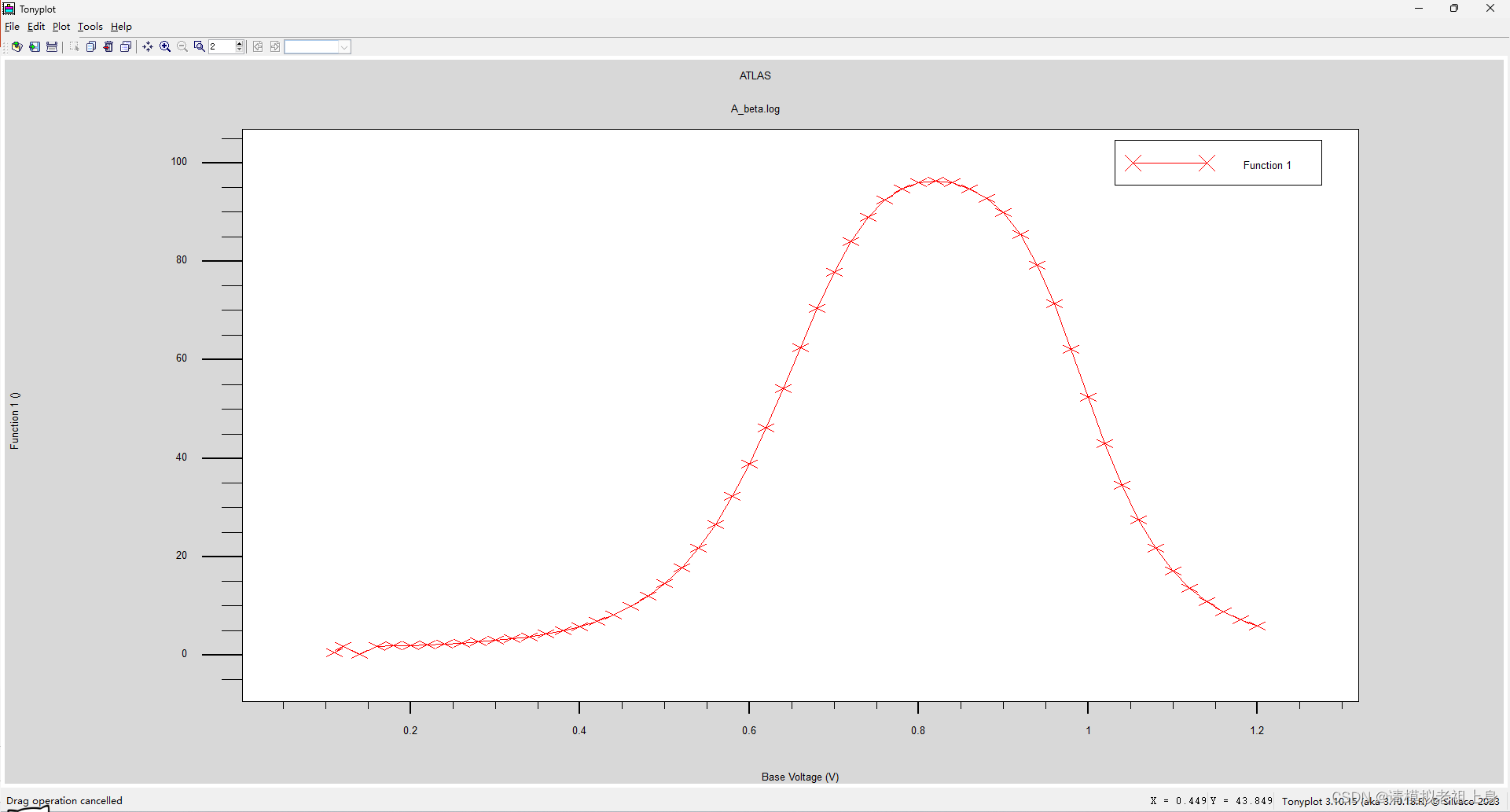

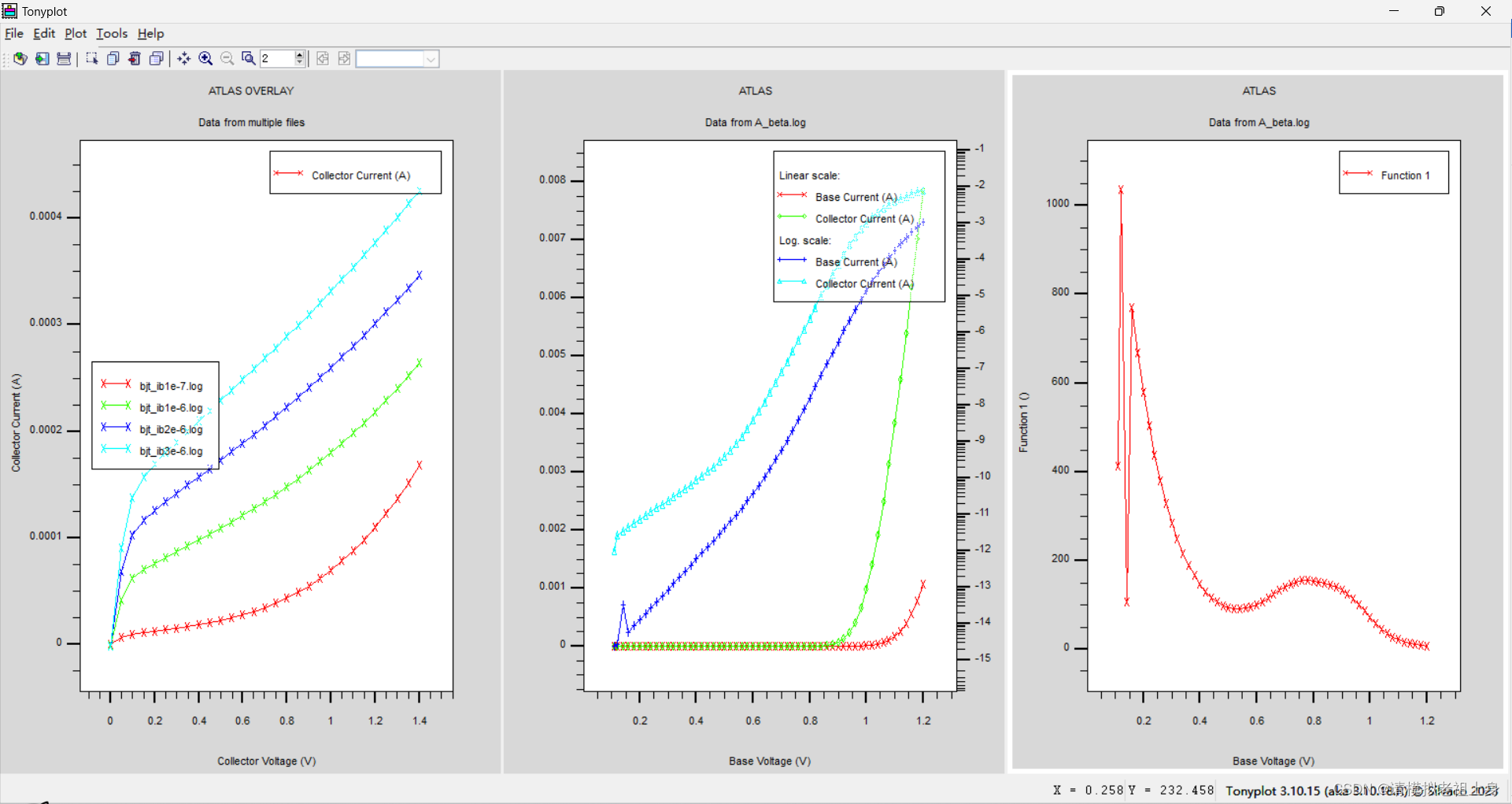

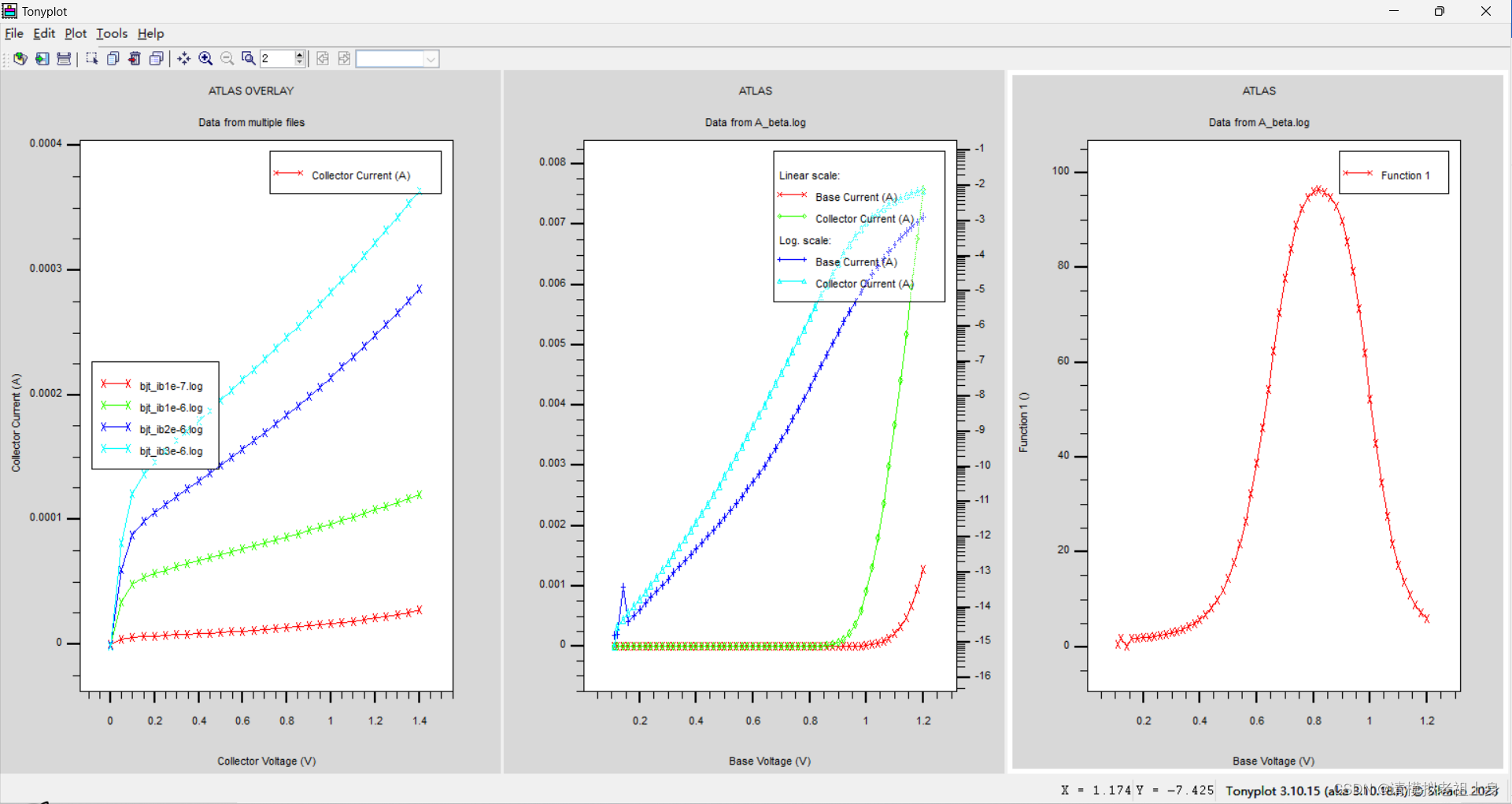

图8 共射极电流增益代码与图形展示

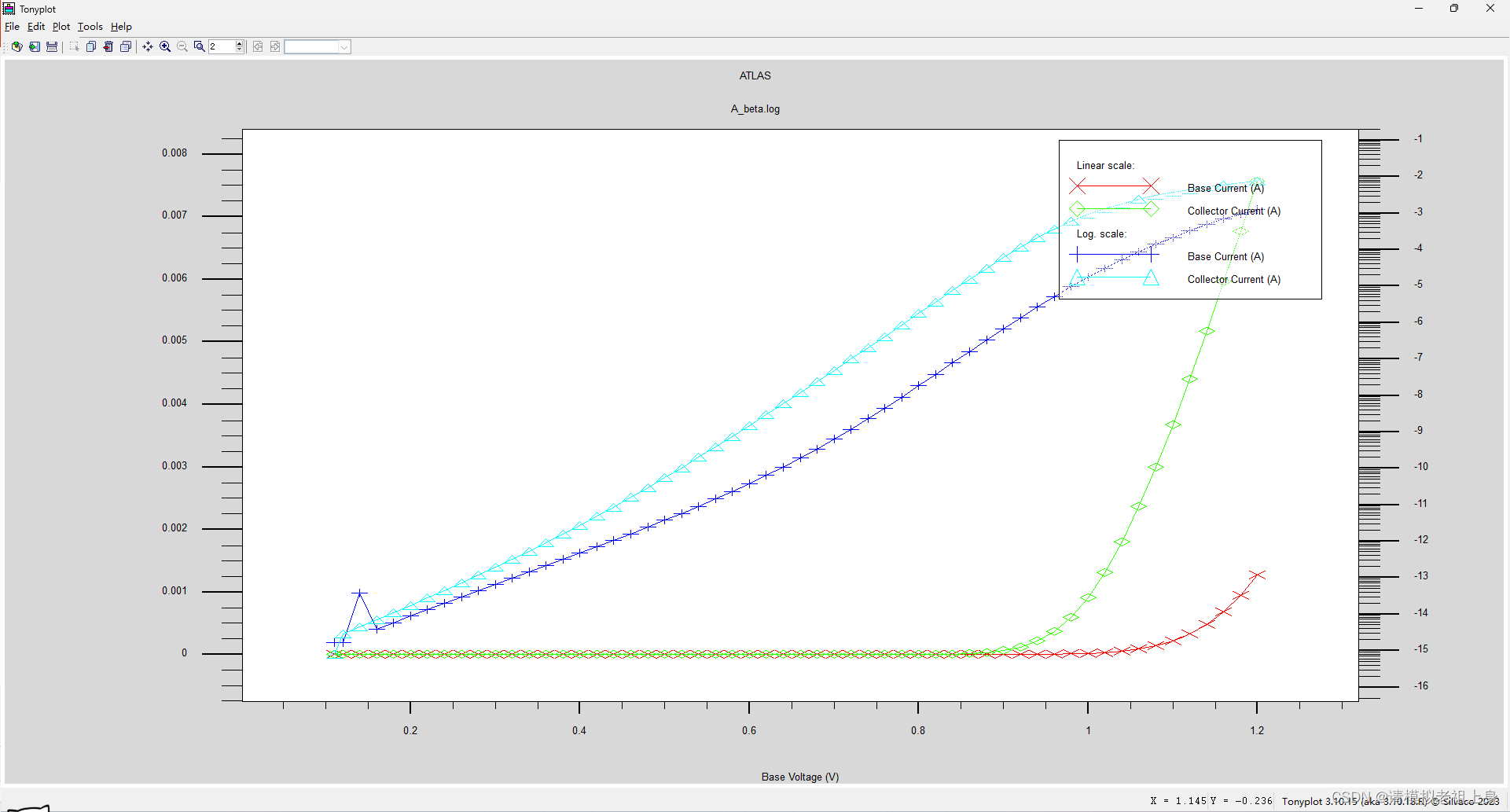

7. 输出Gummel曲线

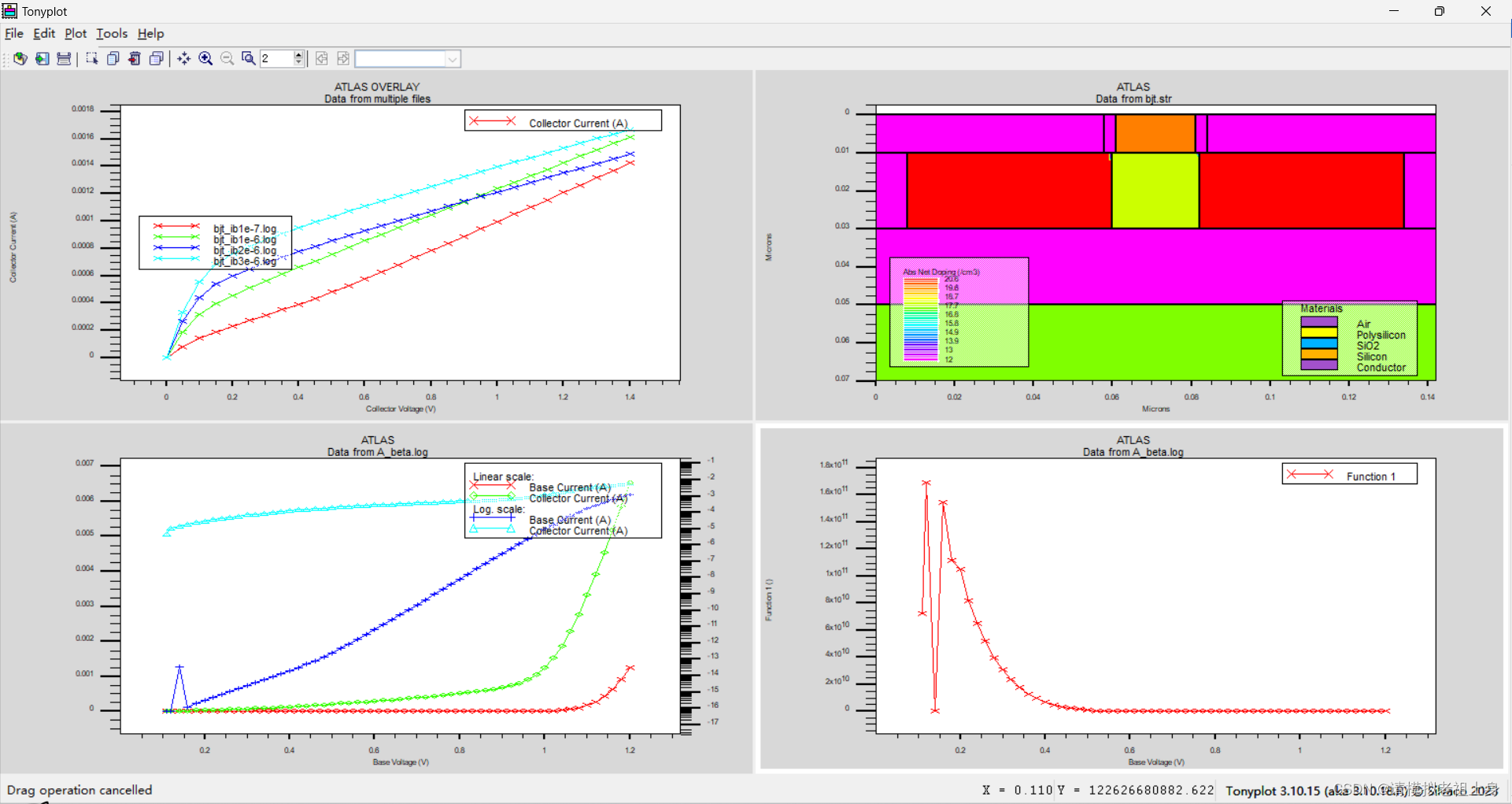

图9 Gummel曲线

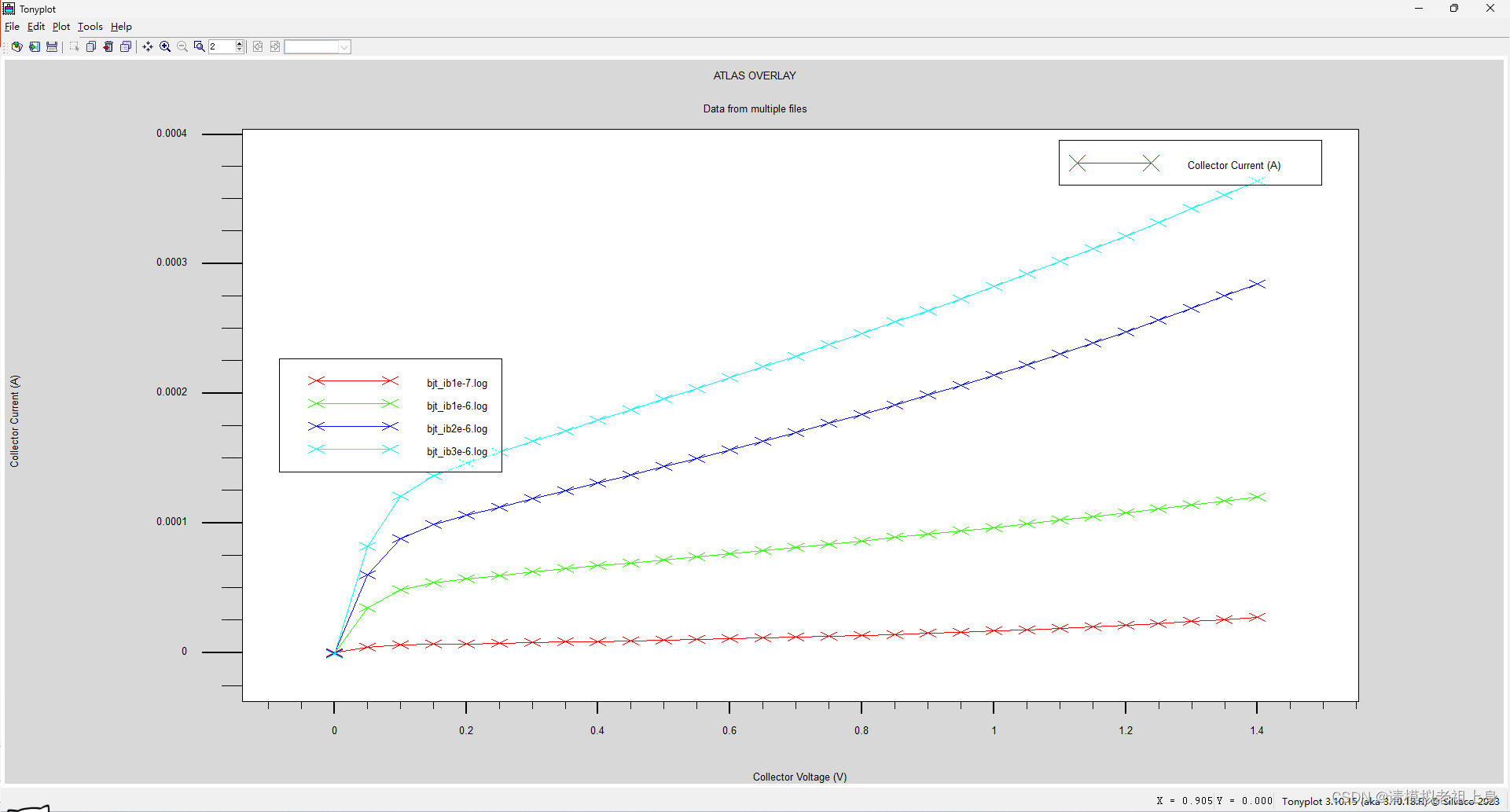

8. 输出I-V 特性曲线

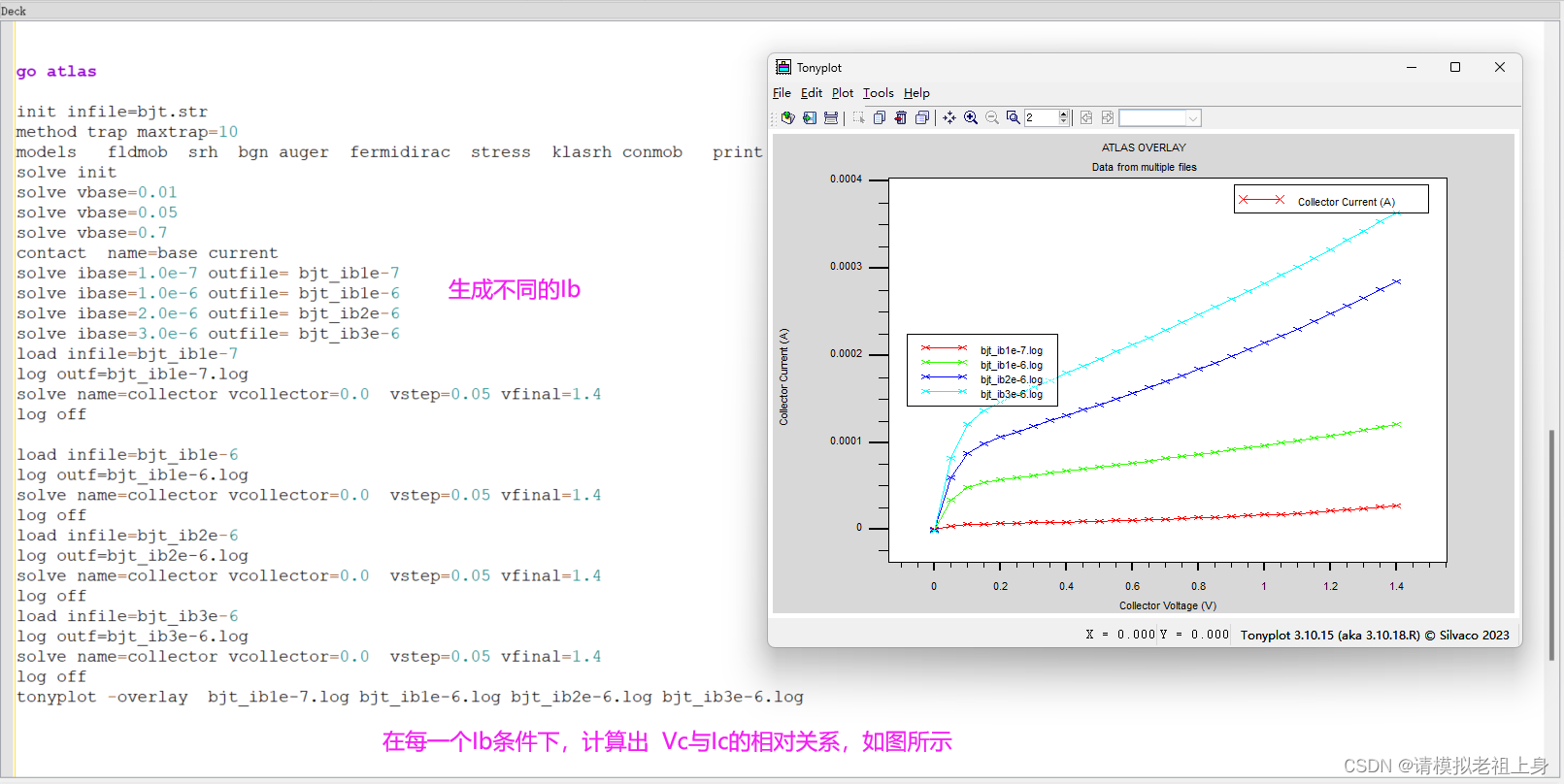

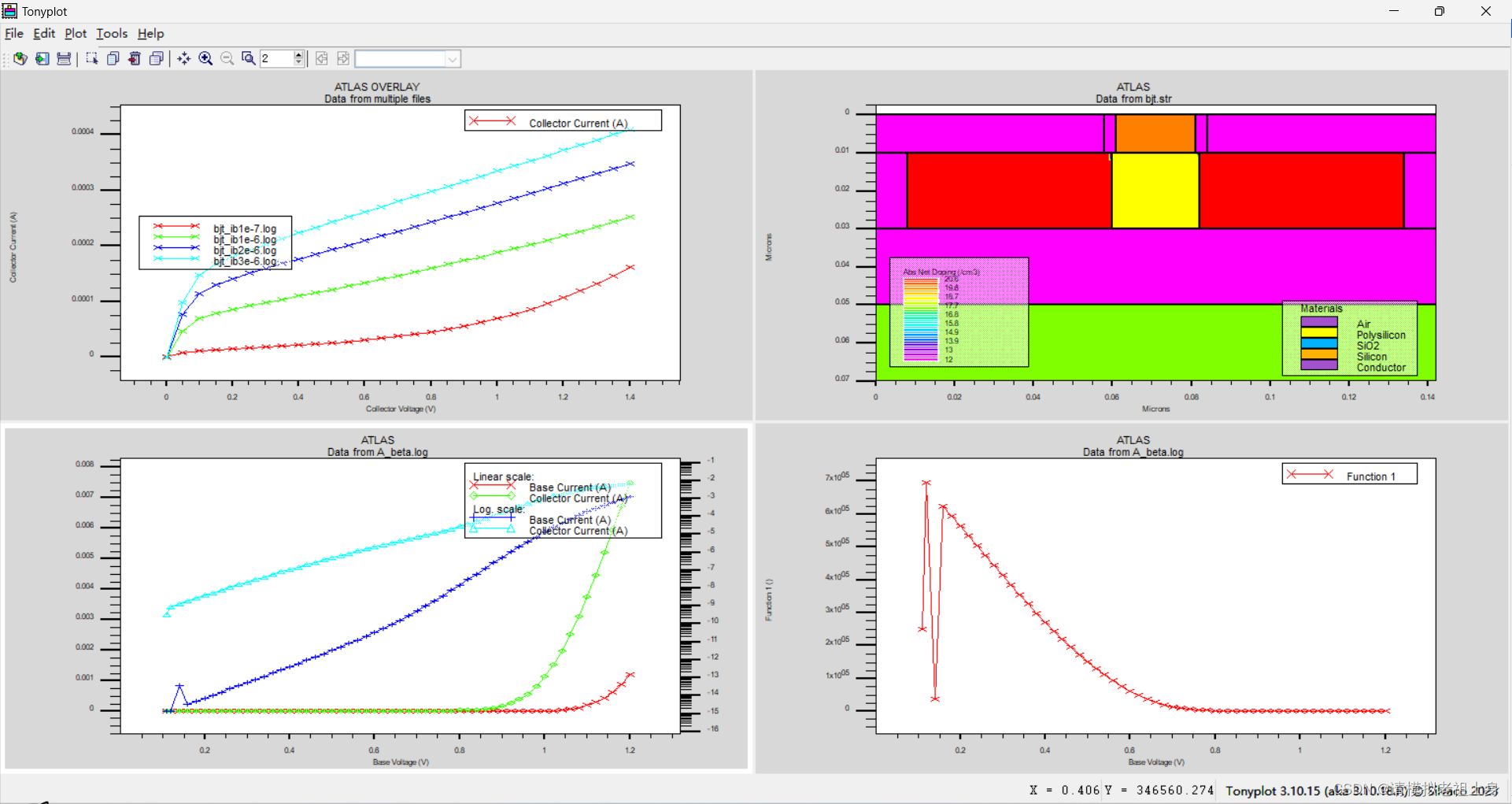

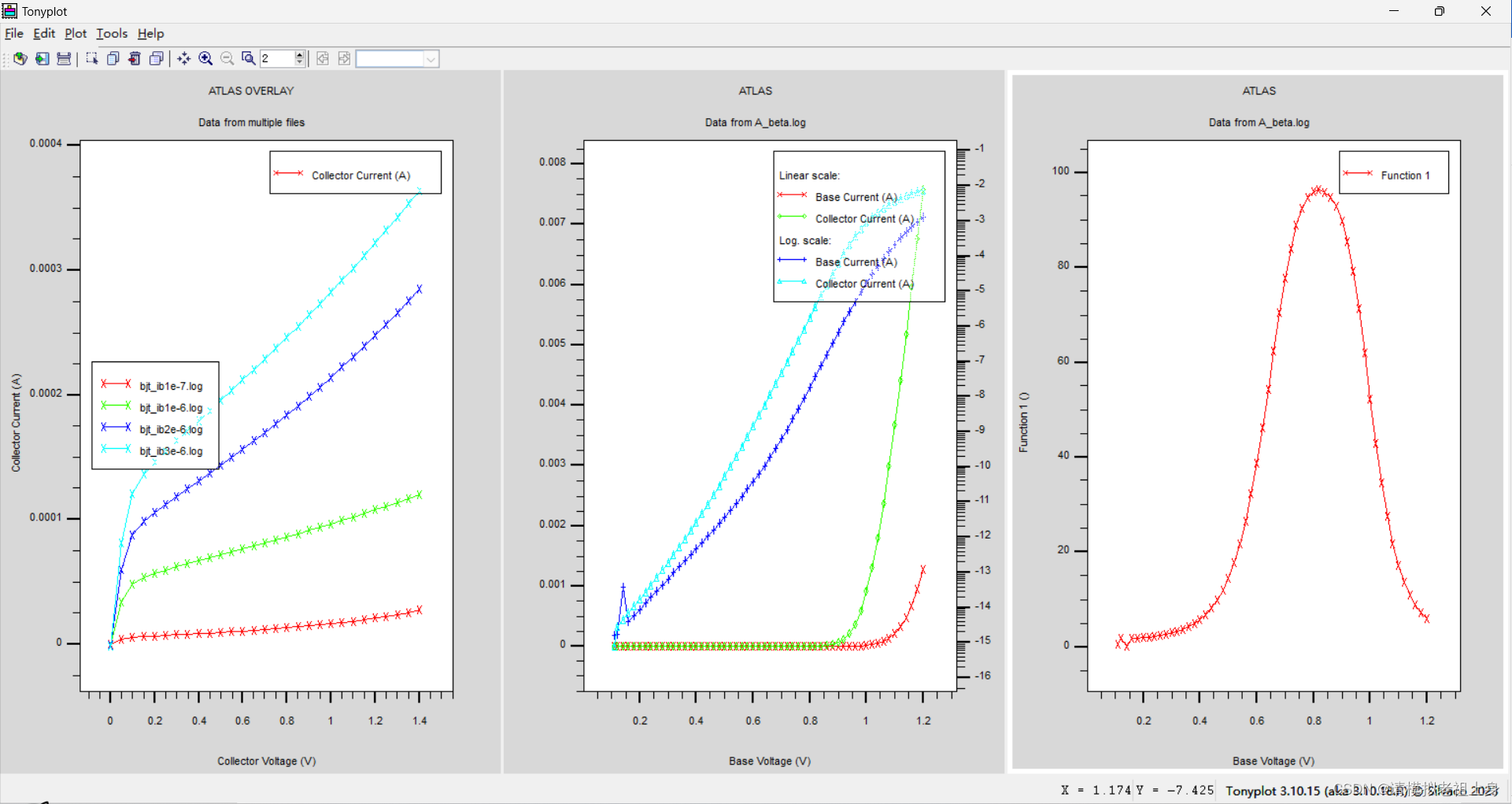

图10 I-V特性曲线

四、实验过程原始记录(数据、图表、相关计算等)(40%)

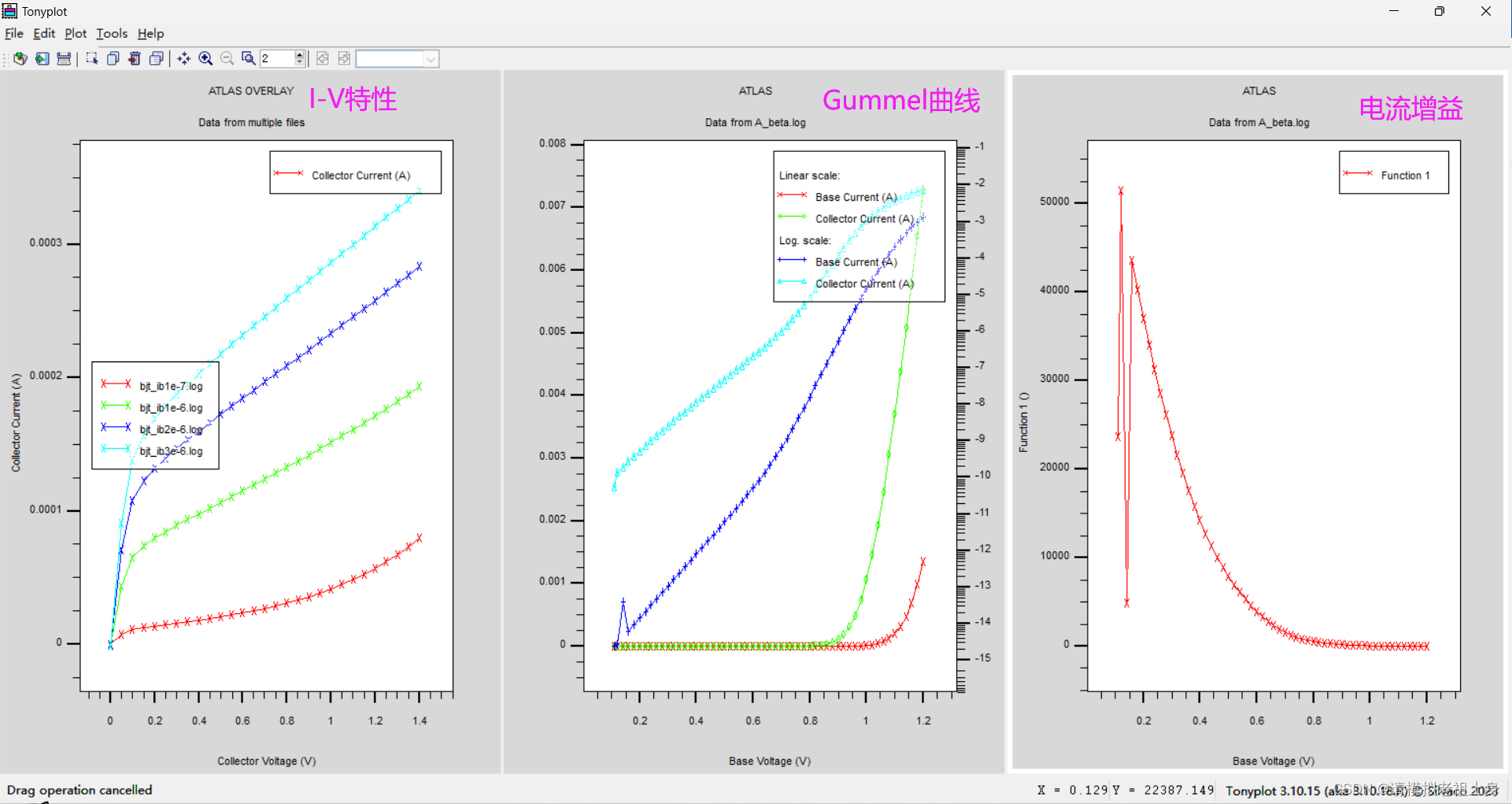

4.1 均匀基区,如上掺杂浓度下的实验数据

1.器件结构

2.共射级电流增益

3. Gummel 曲线

4. I-V特性曲线

5.分析与总结见思考题一

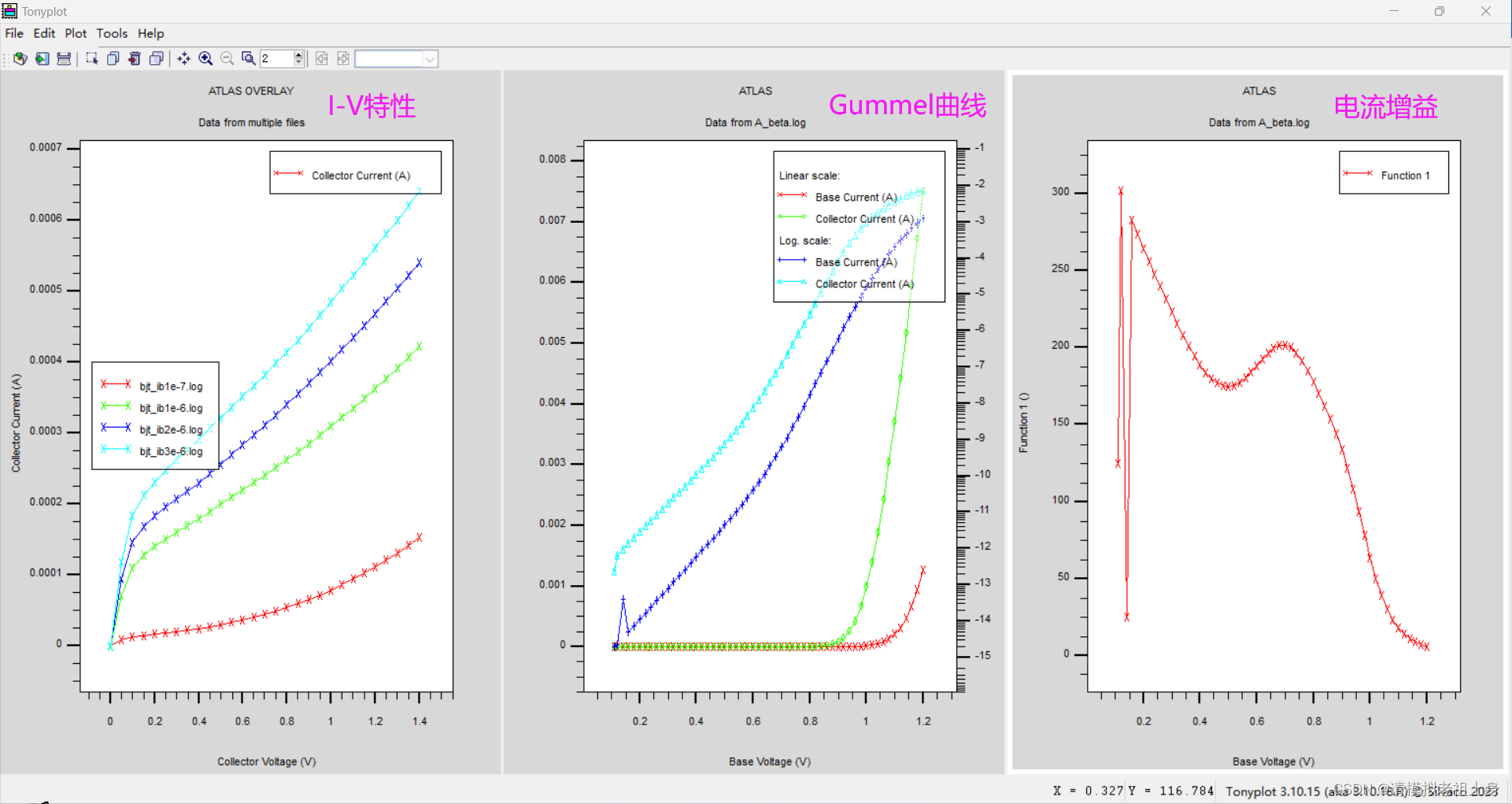

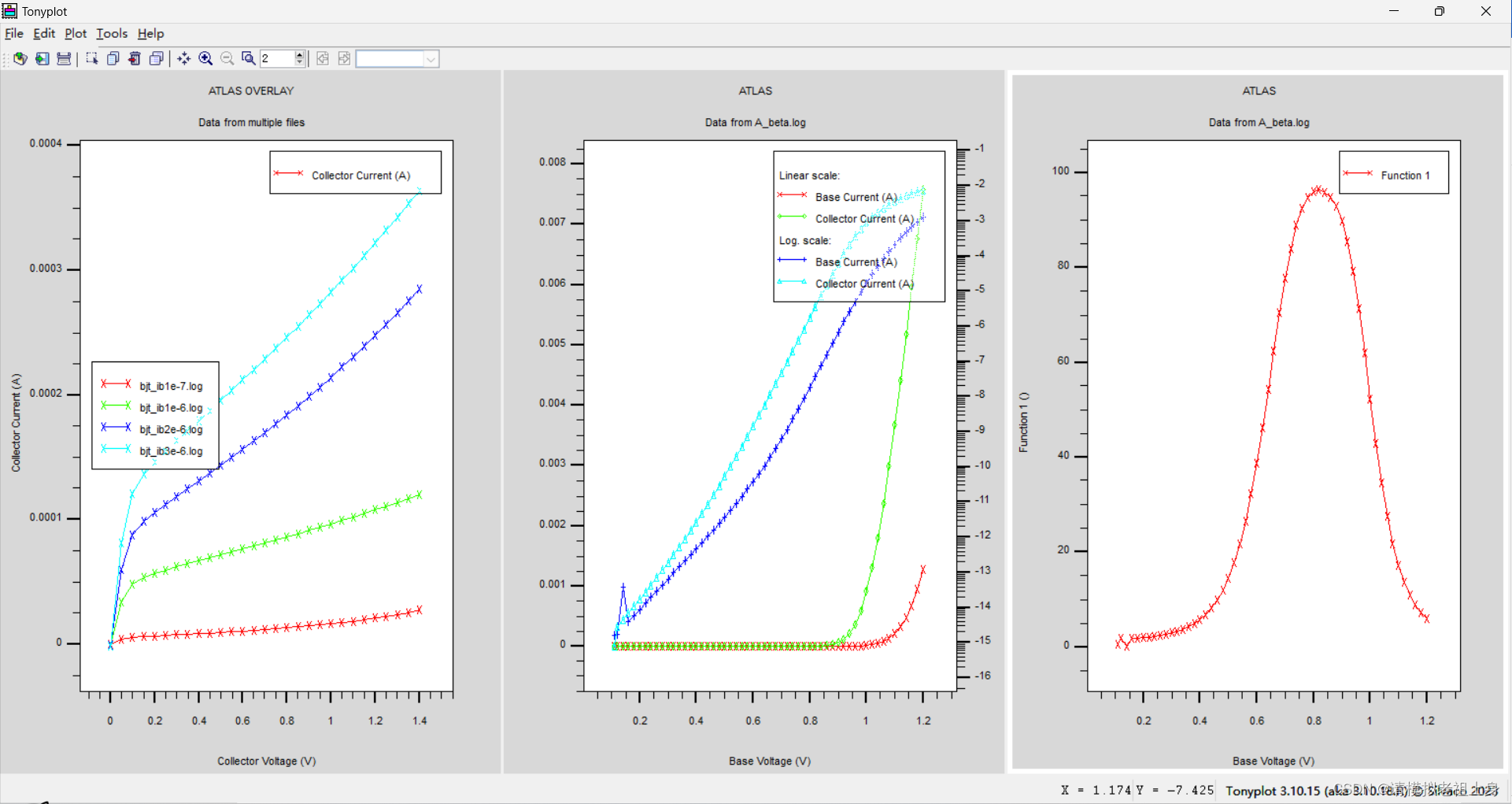

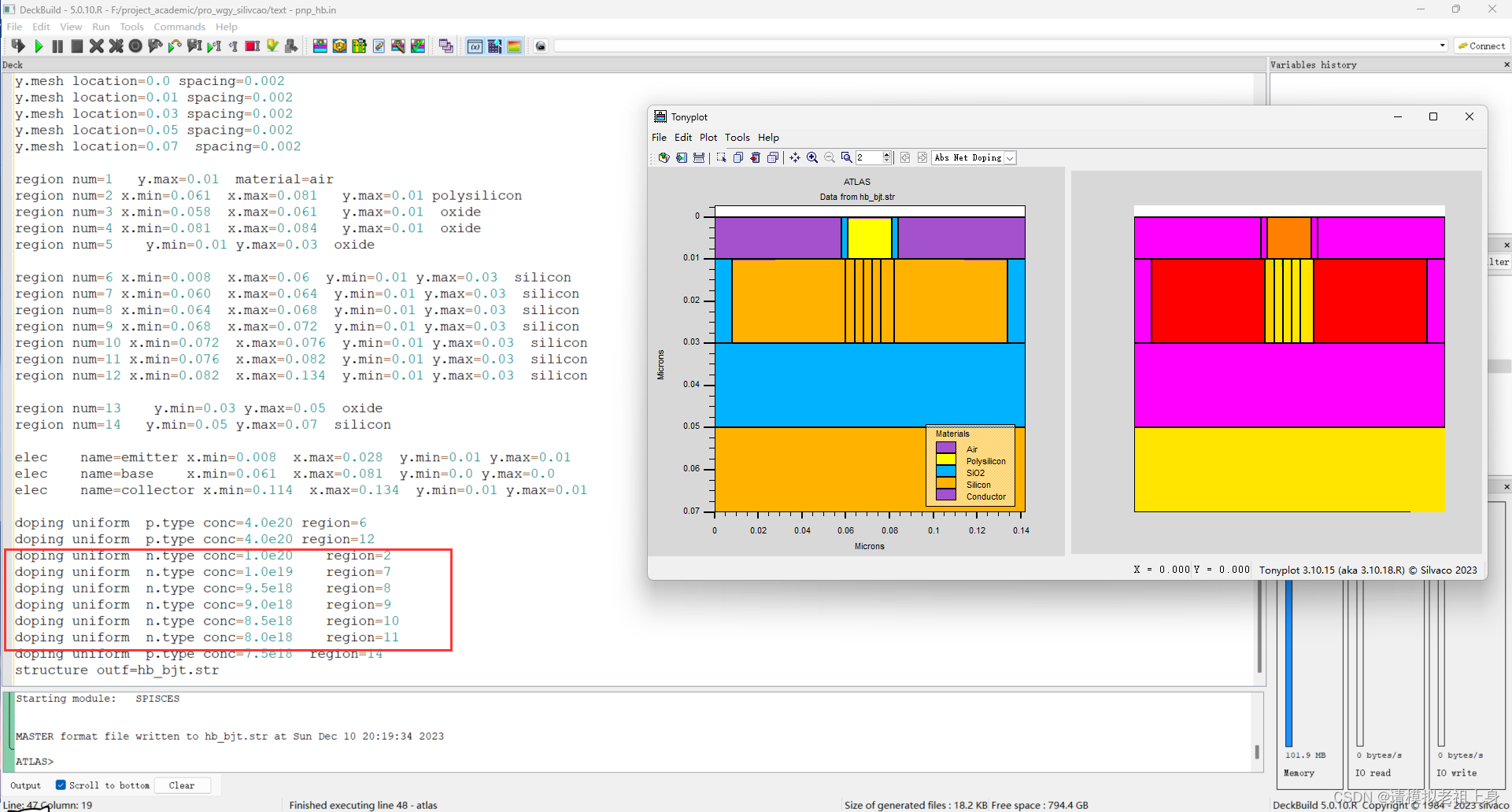

4.2 缓变基区,如上掺杂浓度下的实验数据

其他条件均不变,只是通过以下代码,构建如图所示模型

下面通过控制变量,只展示当内建电场浓度梯度变化时,其各曲线的差异。

1.当掺杂浓度差为2e18

2.当掺杂浓度差为1e18

3.当掺杂浓度差为5e17

4.分析与总结

(1) 一定范围内,基区自建电场浓度差越小,BJT的放大倍数越高。

(2)一定范围内,基区自建电场浓度差越小,BJT的厄利电压越大,与放大倍数呈相反关系。

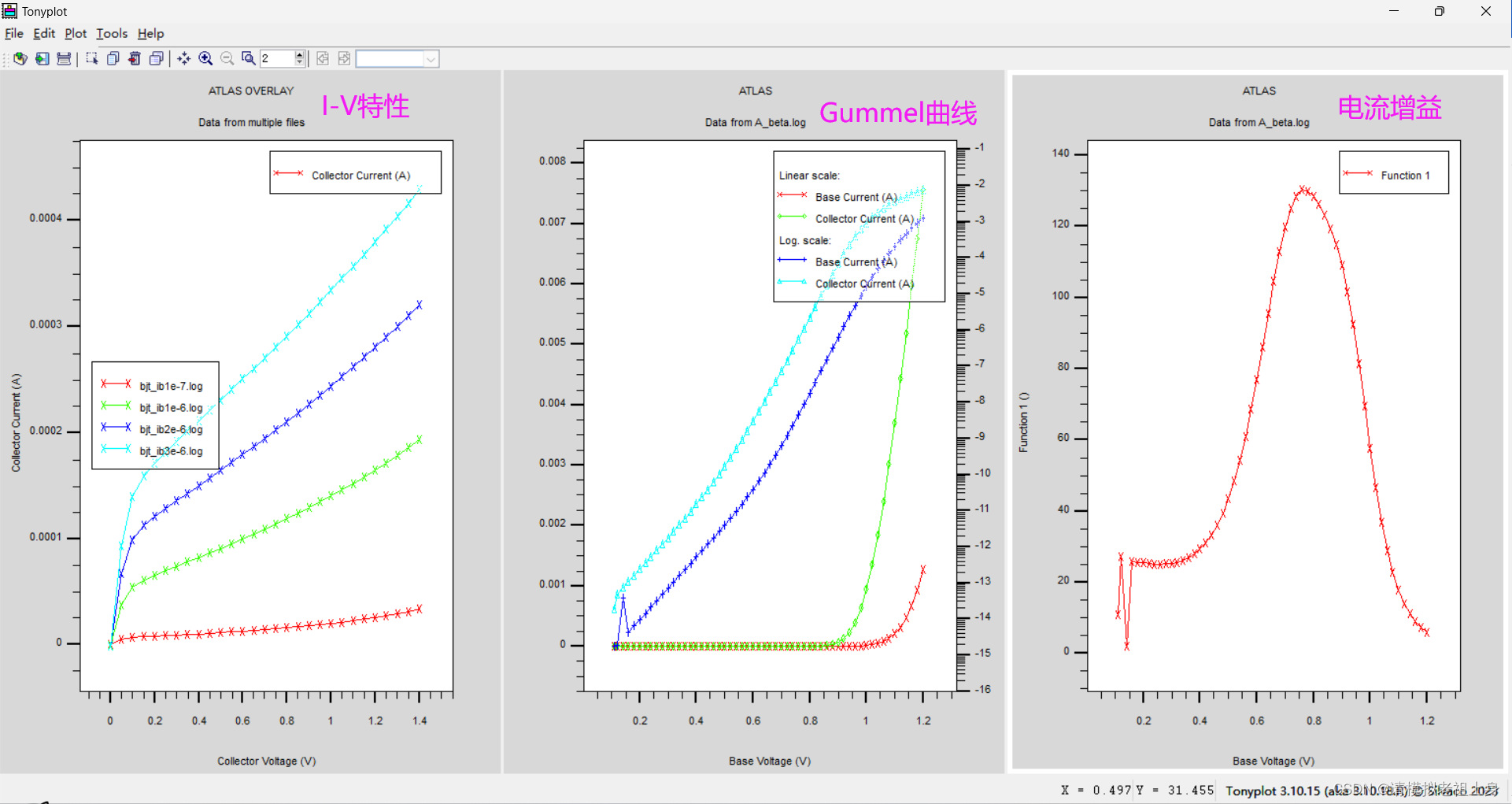

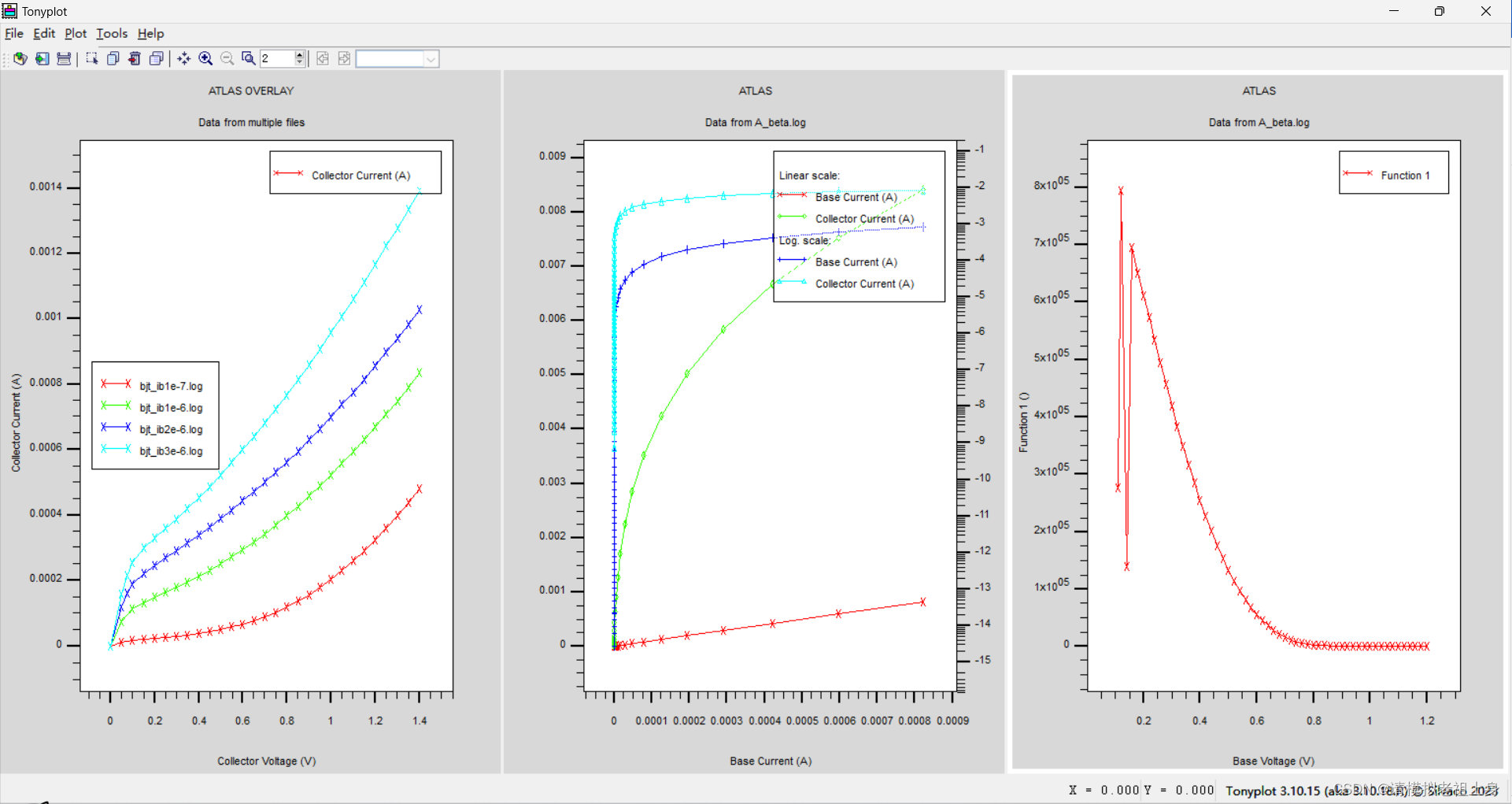

4.3 均匀薄基区,如上掺杂浓度下的实验数据

下面通过控制变量,只展示当基区厚度发生变化时,其各曲线的差异。

1.基区宽度为20nm

2.基区宽度为18nm

3.基区宽度为15nm

4.总结与分析:

(1)一定范围内,基区宽度越小,BJT的放大倍数越高。受制于工艺不好控制。

(2)一定范围内,基区宽度越大,BJT的厄利电压越大,与放大倍数呈相反关系。

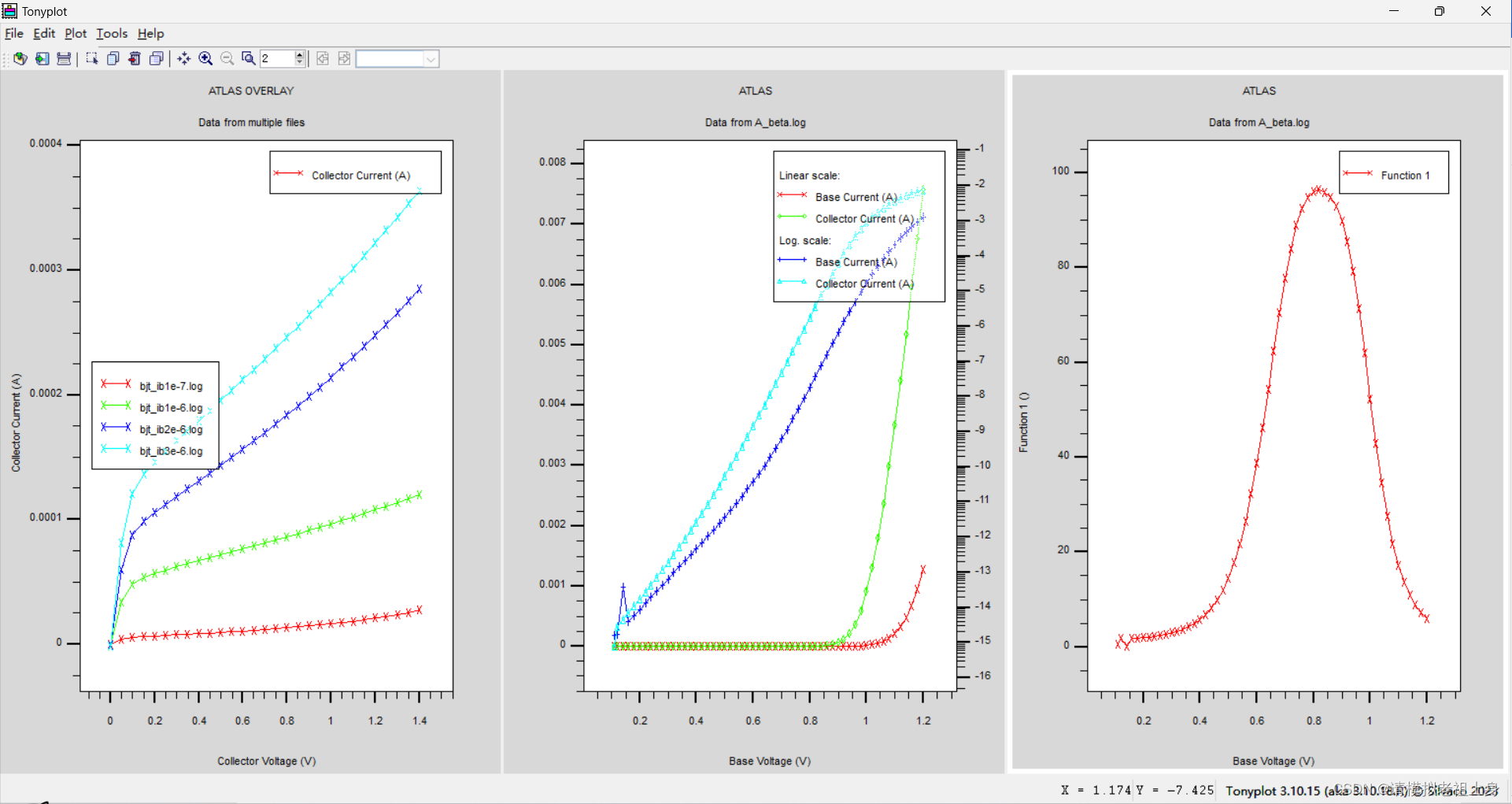

4.4 改变基区掺杂浓度,探究其对器件性能产生的影响

1. 基区掺杂浓度为1e19

2. 基区掺杂浓度为 8e18

3. 基区掺杂浓度为5e18

4. 基区掺杂浓度为1e18

5. 分析与总结

(1)一定范围内,基区的掺杂浓度越小,BJT的放大倍数越高。

(2) 一定范围内,基区的掺杂浓度越大,BJT的厄利电压越大,与放大倍数呈相反关系。

五、思考题分析(20%)

1. 按照仿真流程构建器件模型,正确得到各种曲线并加以解释分析;

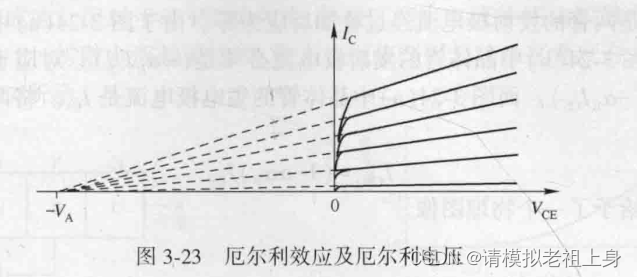

(1)第一张图,主要描述基区宽变调制效应(厄利效应)对输出特性产生的影响,也就是为什么Ic随着Vce会有略微增大。

原因:Vce增大àVbc=Vbe-Vce增大(集电结的反向偏压)à集电结势垒区变宽,中性基区变窄à基区少子浓度梯度增大à放大系数增大,Ic增大

Va(厄利电压): 各个曲线反向延长线所交于一点的电压绝对值,Va越大,曲线越趋于理想。减小厄利效应的方法:增大基区宽度Wb,增大基区掺杂浓(与增大放大倍数的方法正好相反)

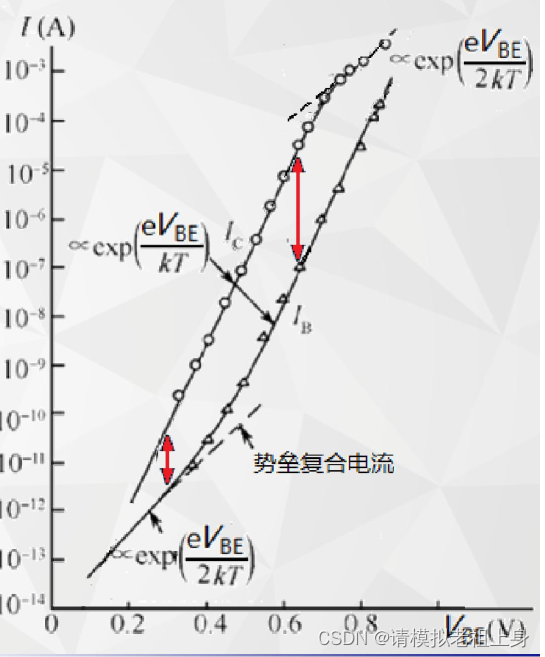

(3)第二张图,Gummel数主要用于研究注入效率

基区注入效率和基区输运系数又会对电流放大系数产生影响。在半对数坐标系中,当电压很小时,势垒复合电流占据主导,斜率大约为q/2kT,接着是两条曲线的垂直距离反映电流放大倍数,斜率均为q/kT,最后受制于大注入效应的影响,斜率为q/2kT。如理论学习的模型图所示,

基区注入效率和基区输运系数又会对电流放大系数产生影响。在半对数坐标系中,当电压很小时,势垒复合电流占据主导,斜率大约为q/2kT,接着是两条曲线的垂直距离反映电流放大倍数,斜率均为q/kT,最后受制于大注入效应的影响,斜率为q/2kT。如理论学习的模型图所示,

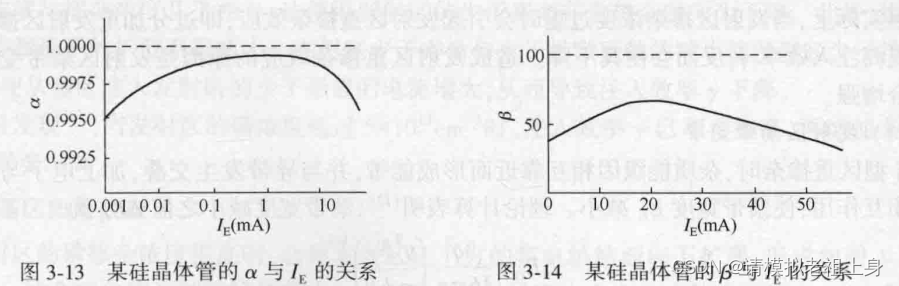

(3) 第三张图,主要描述放大倍数与Vbe之间的关系,有图可见,当Ie由0开始增加时(Ie受Ib的控制),放大倍数先是增加,在正常的电流范围内(管子完全打开,受二级效应影响较小),可认为放大倍数为一常数,当Ie很大时,放大倍数减小,是因为收到了二级效应的影响。(大注入效应,基区扩展效应)。

2. 从曲线中计算或读取放大系数、厄尔利电压;

由图可见,当基极电压在一定范围内不变时,放大倍数大约为100。

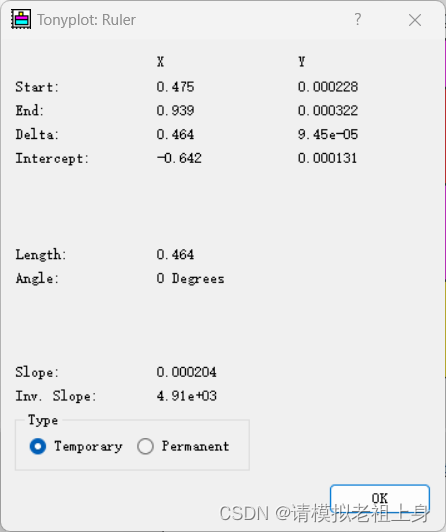

点击tonyplot 中的tool选项,选择rule,对I-V特性曲线的斜率进行测量得到如下数据:

厄利电压数值大小为0.642V。

3.思考:如何改进器件结构或参数,使得放大系数得以提高?使厄尔利电压减小?给出你的仿真验证过程。

(1) 提升放大倍数的手段

从微电子器件的角度出发,提升BJT三极管放大倍数的手段可以包括以下几点:

1. 减小基极宽度:减小基极宽度可以增加电流增益,从而提高放大倍数。

2. 优化掺杂浓度:通过控制基区、发射区和集电区的掺杂浓度,可以改善电流增益和频率响应,从而提高放大倍数。

3. 优化结构设计:设计更合理的结构,如采用双极型结构、双异质结构等,可以提高电流增益和频率响应,从而提高放大倍数。

4. 降低电荷存储时间:通过减小基区的电荷存储时间,可以提高频率响应和放大倍数。

5. 优化工艺参数:通过优化工艺参数,如减小接触电阻、减小漏电流等,可以提高三极管的性能,从而提高放大倍数。

本次实验仅从基区宽度,优化结构(采用缓变基区),基区掺杂浓度三个角度出发,研究其与放大倍数的关系,我们采用控制变量法。当研究基区宽度时,控制其它参数不变,看20nm.18nm,15nm下,基于SOI技术的BJT管子的放大倍数(图形,数据与分析见4.3)。结论:一定范围内,基区宽度越小,BJT的放大倍数越高。当研究缓变基区时,控制其它参数不变,看不同浓度梯度差(2e18,1e18,5e17)下,基于SOI技术的BJT管子的放大倍数(图形与数据见4.2)。结论:一定范围内,缓变基区相邻区域浓度差越大,BJT的放大倍数越高。

(2) 降低厄利电压的手段

增大基区宽度Wb

当改变基区宽度时,控制其它参数不变,看20nm.18nm,15nm下,基于SOI技术的BJT管子的厄利电压(图形,数据与分析见4.3)。结论:一定范围内,基区宽度越小,BJT的厄利电压越小。与放大倍数呈相反关系。

增大基区掺杂浓度

当改变基区掺杂浓度时,控制其它参数不变,看不同基区浓度(1e19,8e18,5e18,1e18)下,基于SOI技术的BJT管子的放大倍数(图形,数据与分析见4.4)。结论:一定范围内,基区的掺杂浓度越大,BJT的厄利电压越大,与放大倍数呈相反关系。

4. 能否试着构建PNP型的晶体管结构?

1. 均匀基区

2.缓变基区

六、实验心得(5%)

本次微电子器件基础实验主要是在silvcao平台上,使用SOI技术去搭建一个NPN晶体管,探究其直流特性比如电流放大系数,I-V特性曲线,通过输出Gummel曲线去研究注入效率对电流放大系数所产生的影响……,在课上王冠宇老师的提问中,去探究可以通过什么方式去提升管子的放大倍数?如引入缓变基区结构,合理增加其相邻区域的浓度梯度,王老师在课堂上由实验入手深入浅出的讲述了相关原理,让我感受到了做微电子器件的魅力。

在搭建BJT晶体管的过程中,我深刻体会到了SOI技术的优势。SOI技术可以减少晶体管之间的互相干扰,提高晶体管的性能和可靠性。此外,SOI结构还可以提高晶体管的速度和功率效率,减少电荷耦合和电阻效应。因此,使用SOI技术搭建BJT晶体管可以更准确地研究器件的性能,并且有助于优化器件设计。

在仿真过程中,我发现电流放大倍数、基区输运系数和注入效率等对器件性能的影响非常显著。通过调整这些参数,我可以观察到晶体管的电流放大倍数和效率的变化。这让我对器件参数的选择和优化有了更清晰的认识,也使我更加熟悉了BJT晶体管的工作原理。同时, 在调整参数时,我发现一些参数的变化对器件性能的影响并不直观,需要进行大量的仿真和分析才能得出结论。同时,由于SOI技术在实际制造中的复杂性,我也遇到了一些模型和仿真工具的局限性,需要不断地查阅资料和与同学交流才能解决问题。

总的来说,通过半导体器件仿真的实践,我对SOI技术、BJT晶体管的工作原理和性能有了更深入的理解,也掌握了一些实用的仿真技巧。同时,也让我意识到半导体器件仿真是一个复杂而又有趣的领域,需要不断地学习和实践才能取得更好的成果。在未来的研究和工作中,我将继续深入探究半导体器件的性能和优化,努力提高仿真技术的水平,为后面再微电子行业工作打下坚实基础。

本文详细介绍了在silvcaoTCAD平台上进行的半导体器件实验,重点探讨了SOI技术在构建BJT器件中的应用,涉及实验目的、原理分析、实验步骤、性能参数变化对放大系数和厄利电压的影响,以及如何通过结构优化提升性能。

本文详细介绍了在silvcaoTCAD平台上进行的半导体器件实验,重点探讨了SOI技术在构建BJT器件中的应用,涉及实验目的、原理分析、实验步骤、性能参数变化对放大系数和厄利电压的影响,以及如何通过结构优化提升性能。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?