一、实验目的与实验仪器(5%)

实验仪器:

7nm 微纳电子器件教学套件硬件DE101

实验目的:

1. 学习微纳电子教育套件的使用

2. 利用微纳电子教育套件掌握PN结的电学特性

3. 利用微纳电子教育套件掌握NMOS的电学特性

4. 利用微纳电子教育套件掌握LDMOS的电学特性

5. 利用微纳电子教育套件掌握FinFET的电学特性

二、实验原理分析(10%)

1. PN junction的电学特性与能带图

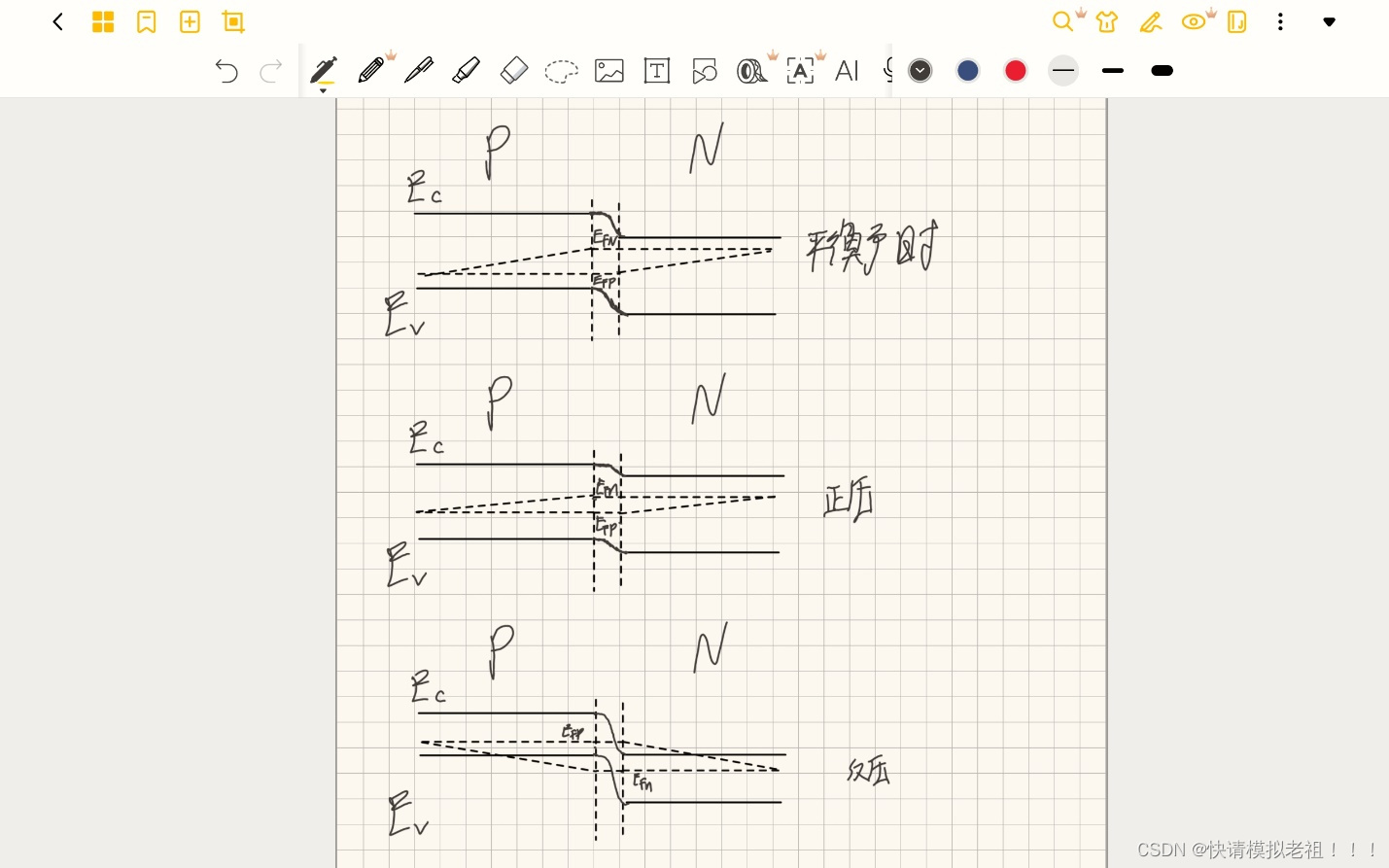

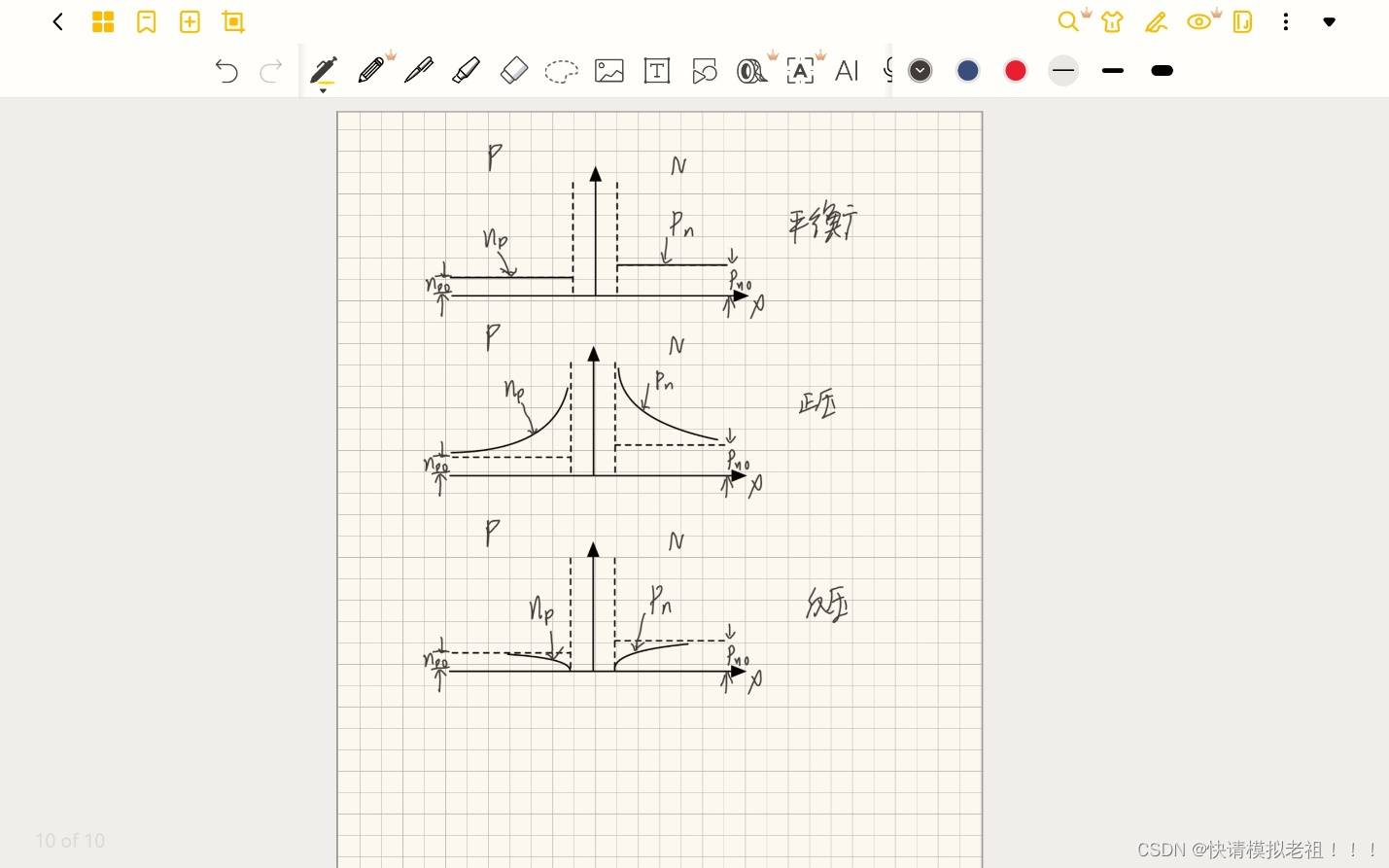

(1) 能带图

a. PN结平衡时、外加正向电压、外加反向电压情况下的能带图。

b. PN结平衡时、外加正向电压、外加反向电压情况下的少子分布图。

(2) 电学特性

a. 在平衡状态下,扩散电流和漂移电流处于动态平衡。扩散电流是由载流子的扩散引起的电流,而漂移电流是由外加电场引起的电流。

b. 在正向偏置时,电子从N区向P区扩散,而空穴从P区向N区扩散,这导致电流的形成。

c. 在反向偏置时,电子和空穴受到外加电场的影响,向远离结区域移动,这导致几乎没有电流通过PN结。当反向电压增加到一定程度时,会发生雪崩击穿。雪崩击穿是指在高电场作用下,少数载流子获得足够能量,撞击晶格,产生更多的载流子,导致电流急剧增加的现象。

(3) 电容特性

扩散电容是由PN结两侧的扩散区域形成的电容。在PN结中,由于扩散过程,载流子会在P区和N区之间形成一个耗尽层,这个耗尽层就是扩散电容的形成部分。扩散电容的大小取决于扩散区域的载流子浓度和PN结的面积。

势垒电容是由PN结的势垒区域形成的电容。当PN结处于正向偏置或反向偏置时,势垒区域的电场会使得PN结两侧形成一个电容效应,这就是势垒电容。势垒电容的大小取决于PN结的结构和外加电压的大小。

扩散电容是由扩散区域形成的耗尽层产生的电容效应,而势垒电容是由势垒区域形成的电场产生的电容效应。另外,扩散电容主要影响器件的高频特性,而势垒电容主要影响器件的低频特性

2. NMOS的电学特性

(1)MOSFET的工作原理是什么?

MOSFET的工作原理是通过在栅极施加电压来控制通道中的电流。当栅极施加正电压时,在氧化物和半导体之间形成一个电场,这将影响半导体中的电荷分布。这种电场可以吸引或排斥电荷,从而控制通道中的电流流动。当栅极电压变化时,通道中的电流也会相应变化。

(2)什么是MOSFET的阈电压?影响因素有哪些?

MOSFET的阈值电压(也称为门极阈值电压)是指在MOSFET中开始导通电流的栅极电压。当栅极电压超过阈值电压时,MOSFET开始导通电流。

影响因素:

材料特性: MOSFET的闻值电压受到半导体材料的影响,不同的半导体材料会有不同的闻值电压。

惨杂:半导体材料的掺杂水平会影响闯值电压的大小。掺杂更多的材料通常会导致较低的闻值电压

氧化层厚度: MOSFET中的氧化层厚度也会影响闻值电压。较薄的氧化层会导致较低的闻值电压。

结构设计: MOSFET的结构设计也会影响闻值电压。例如,通道长度和宽度的设计会影响闻值电压的大小。

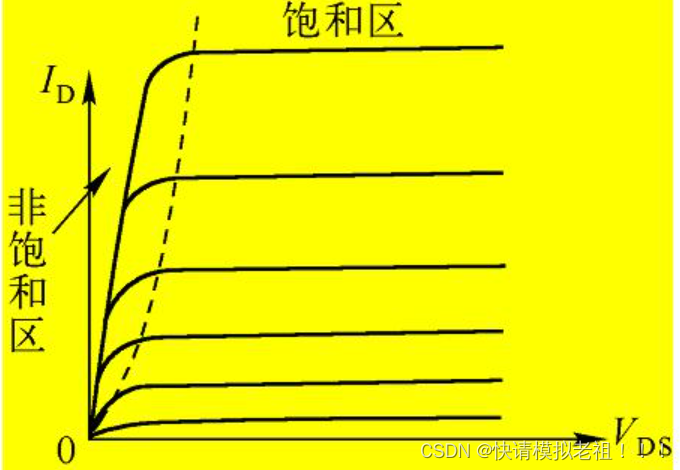

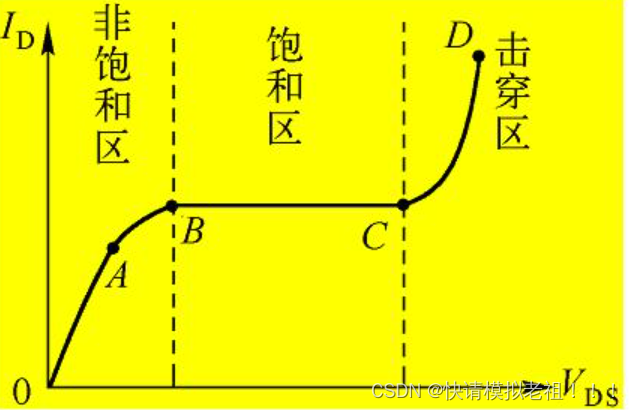

(3)MOSFET的输出特性曲线是怎样的,如何分区?

0~A为线性区,A~B为过渡区,B~C为饱和区,C~D为击穿区。

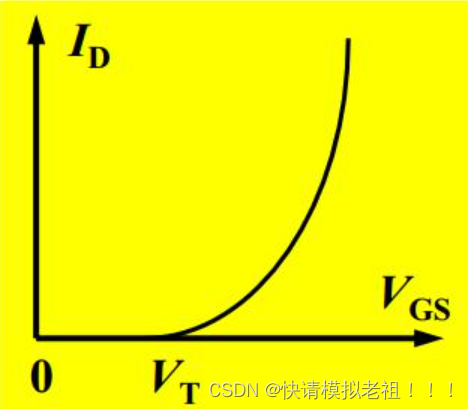

(4)MOSFET的转移特性曲线是怎样的,如何分区?

VGS < VGS(th)时,MOS管处于夹断区(截止区)。

VGS>VGS(th) ,且VDS < VGS - VGS(th),MOS管进入可变电阻区。

VGS≥VGS(th),且VDS>VGS-VGS(th),MOS管进入恒流区。

随着VDS增大,PN结承受太大的反向电压而被击穿。

(5)MOSFET的衬底电流Isub与VGS之间的变化关系曲线是怎么样的?

当漏源电压VDS不变时,亚阈漏极电流IDsub与栅源电压VGS呈指数关系,类似于PN结的正向伏安特性。

3. LDMOS的电学特性

LDMOS(横向双扩散金属氧化物半导体)是一种功率MOSFET器件,它具有低导通电阻、高击穿电压和高开关速度等优点,广泛应用于射频功率放大器、开关电源和电机驱动等领域。

LDMOS的工作原理与普通MOSFET类似,都是通过栅极电压控制沟道中的电子或空穴浓度来实现导通和截止。然而,LDMOS与普通MOSFET的不同之处在于,它的源极和漏极都是扩散形成的,而不是离子注入形成的。这种结构使LDMOS具有更高的击穿电压和更低的导通电阻。

LDMOS的电学特性主要包括导通电阻、击穿电压、开关速度和热阻。导通电阻是指器件在导通状态下的电阻,它主要由沟道电阻和源极电阻组成。击穿电压是指器件能够承受的最大电压,它主要由器件的掺杂浓度和沟道的长度决定。开关速度是指器件从导通状态切换到截止状态所需的时间,它主要由器件的栅极电容和漏极电容决定。热阻是指器件从芯片表面到散热器之间的热阻,它主要由器件的封装材料和结构决定。

4. FinFET的电学特性

FinFET(鳍式场效应晶体管)是一种新型的场效应晶体管,它具有更小的尺寸、更快的速度和更低的功耗,被认为是下一代集成电路的核心器件。

FinFET的工作原理与传统的平面MOSFET类似,都是通过栅极电压控制沟道中的电子或空穴浓度来实现导通和截止。然而,FinFET与平面MOSFET的不同之处在于,它的沟道不是平面的,而是在衬底上形成了一系列垂直的鳍状结构。这种结构使FinFET具有更高的栅极控制能力和更小的短沟道效应,从而可以实现更小的尺寸和更快的速度。

FinFET的电学特性主要包括导通电阻、击穿电压、开关速度和亚阈值摆幅。导通电阻是指器件在导通状态下的电阻,它主要由沟道电阻和源极/漏极电阻组成。击穿电压是指器件能够承受的最大电压,它主要由器件的掺杂浓度和沟道的长度决定。开关速度是指器件从导通状态切换到截止状态所需的时间,它主要由器件的栅极电容和漏极电容决定。亚阈值摆幅是指器件从截止状态切换到导通状态所需的栅极电压变化量,它主要由器件的沟道掺杂浓度和栅极氧化物厚度决定。

FinFET与平面MOSFET相比,具有以下优点:

1. 更小的尺寸:FinFET的沟道是垂直的,而不是平面的,这使得它可以实现更小的尺寸。

2. 更快的速度:FinFET具有更高的栅极控制能力和更小的短沟道效应,这使得它可以实现更快的速度。

3. 更低的功耗:FinFET具有更低的亚阈值摆幅,这使得它可以实现更低的功耗。

FinFET目前已经成为主流的集成电路器件,并被广泛应用于智能手机、平板电脑和笔记本电脑等电子产品中。随着FinFET技术的不断发展,它有望在未来实现更高的性能和更低的功耗,从而推动集成电路行业的发展。

1497

1497

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?