一、generate语法举例

generate

genvar i;

for(i=0;i<=9;i=i+1) begin

assign D[i] = A[i];

end

endgenerate

上述语句实现将assign D[0]=A[0];assign D[1]=A[1];assign D[2]=A[2];·····assign D[9]=A[9];

二、generate的灵活使用

当赋值语句较多,且具备一定的规律时,可以灵活使用取整 /、取余 %等语句实现。

举例如下:

module map(

input [63:0] A [3:0],//A0、A1、A2、A3的[3:0]为无用数值,不考虑

output [11:0] D [19:0] //ADC0通道A采样点0-19

);

//下述代码拆分如下:

//assign D[0] = A[3][63:52];

//assign D[1] = A[2][63:52];

//assign D[2] = A[1][63:52];

//assign D[3] = A[0][63:52];

//assign D[4] = A[3][51:40];

//assign D[5] = A[2][51:40];

//assign D[6] = A[1][51:40];

//assign D[7] = A[0][51:40];

//..........

//assign D[18] = A[1][15:4];

//assign D[19] = A[0][15:4];

//上述代码可以简化写为:

generate

genvar j;

for(j=0;j<=19;j=j+1) begin

//从帧格式中划分出每个点(12bits),其中"/"为向下取整操作,%为取余

assign D[j] = A[3-j%4][(63-12*(j/4)) : (52-12*(j/4))];

end

endgenerate

endmodule正常情况下赋值语句越多,使用generate越能使程序清晰明了。

三、generate例化多个模块

设计一个加法器IP,8个输入A和8个输入B,输出8个C,利用generate模块减少代码量,使代码更加清晰明了。示例如下:

module TOP(

input CLK,//输入时钟

input [15:0] A [7:0],//输入8个16bits数据

input [15:0] B [7:0],//输入8个16bits数据

output [15:0] S [7:0]//输出8个16bits数据

);

//模块例化

genvar index;

generate

for(index=0; index<8; index=index+1) //例化8个模块

begin: exam//块名称

adder adder_inst (

.A(A[index]), // input wire [15 : 0] A

.B(B[index]), // input wire [15 : 0] B

.CLK(CLK), // input wire CLK

.S(S[index]) // output wire [15 : 0] S

);

end

endgenerate

endmodule

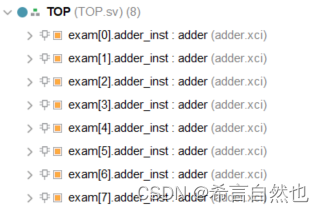

TOP模块在工程中例化形式如下,可以看到成功例化了8个加法器IP核。

其RTL图如下,可以看到结果符合预期,同时例化了8个输入A与8个输入B相加,分别输出给8个C。

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?