参考:pg159

VIO:可以模拟输入/输出功能,实时监视和修改FPGA中的信号,用于调试和验证,与ILA相比,VIO无需占用RAM资源。

VIO IP的输出对于FPGA内部逻辑是输入信号,可以在调试界面设置输入值;输入对内部逻辑是输出信号,用来检测信号变化。

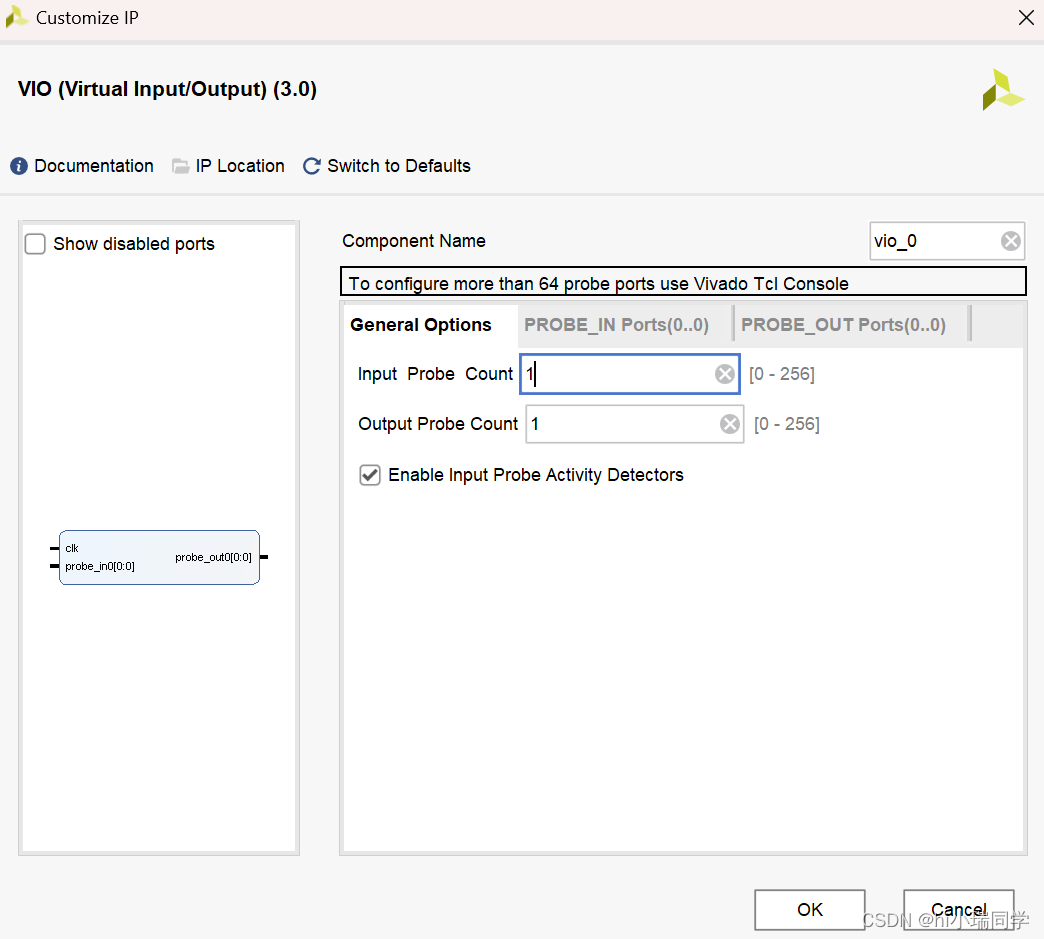

配置:

Input Probe Count:VIO输入探头个数,即输入到VIO、需要查看实时数据值的信号个数;

Output Probe Count:VIO输出探头个数,即输出给其他模块的信号个数;

Enable Input Probe Activity Detectors:输入探头变化检测。若勾选,则在后续调试过程中,某个输入信号发生变化时,则会出现数据变化的提示;若不勾选,则无输入数据变化提示(注意:这里输入是指输入到VIO模块中的数据)。

注:探针连接的信号不可以是该模块的输入信号,也不可以是其子模块的输入信号。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?