一、Quartus-II和 Modelsim 安装

- 简介

Quartus II 是Altera公司推出的综合性CPLD/FPGA开发软件,软件支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware 支持Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

- 安装

二、D触发器简介

- D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

- SD和RD接至基本RS触发器的输入端,它们分别是预置和清零端,低电平有效。当SD=1且RD=0时(SD的非为0,RD的非为1,即在两个控制端口分别从外部输入的电平值,原因是低电平有效),不论输入端D为何种状态,都会使Q=0,Q非=1,即触发器置0;当SD=0且RD=1(SD的非为1,RD的非为0)时,Q=1,Q非=0,触发器置1,SD和RD通常又称为直接置1和置0端。我们设它们均已加入了高电平,不影响电路的工作。

三、Quartus-II构造原理图并时序仿真

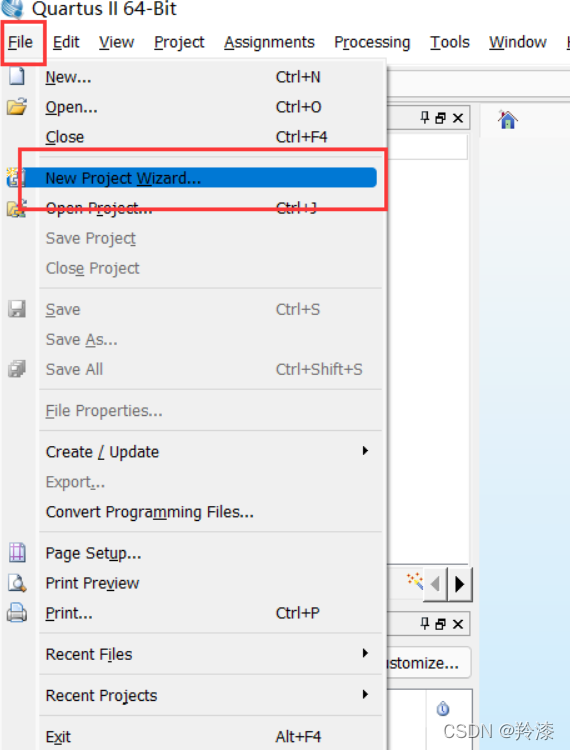

- 点击new project wizard创建新工程

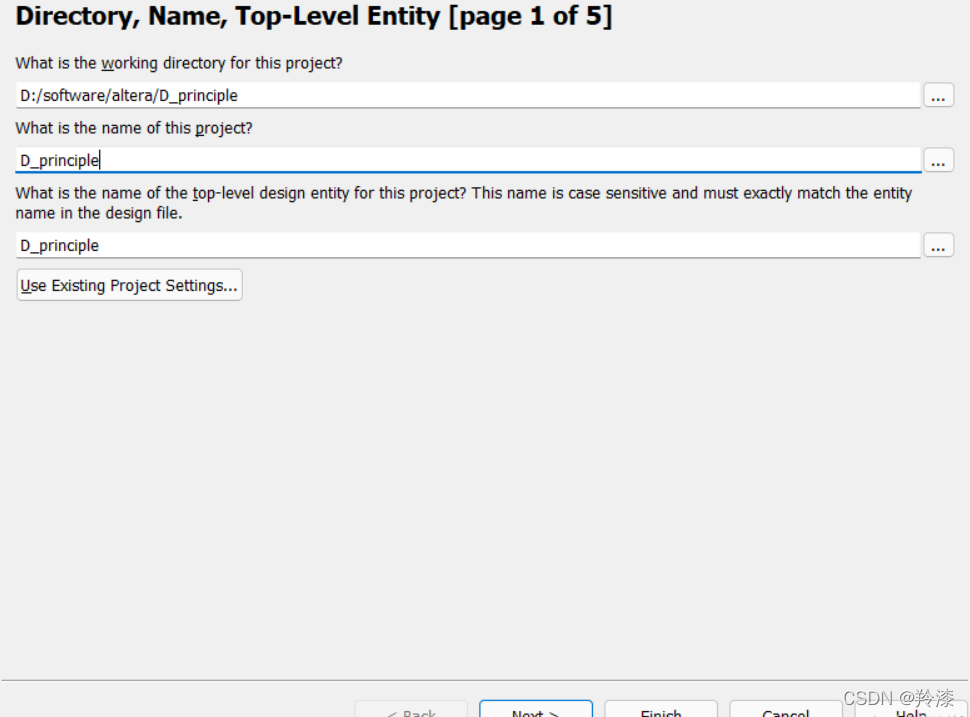

- 设置保存路径,以及项目名和顶层设计名

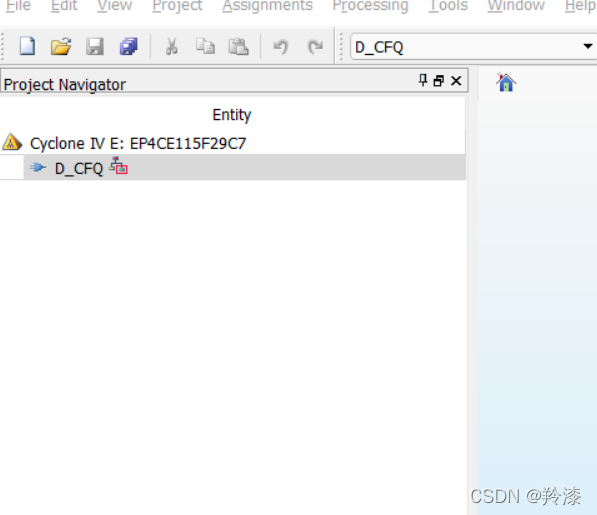

- 一路next,项目就创建完成了

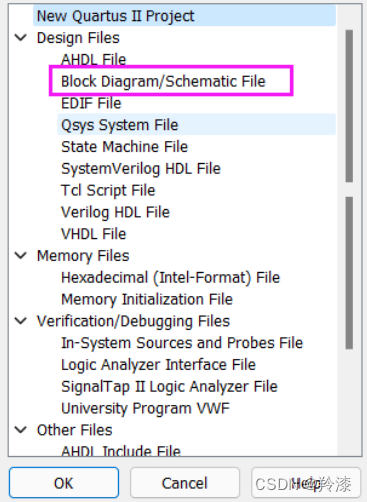

- 点击file -> new,选择Block Diagram/Schematic File

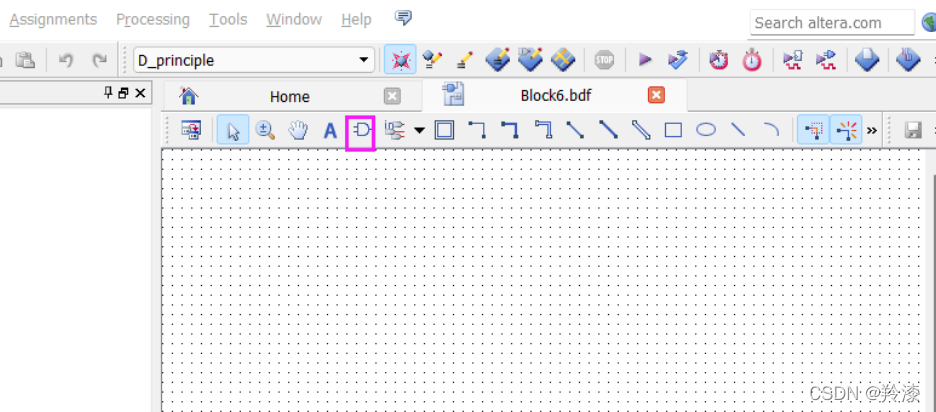

- 再点击下图的小符号

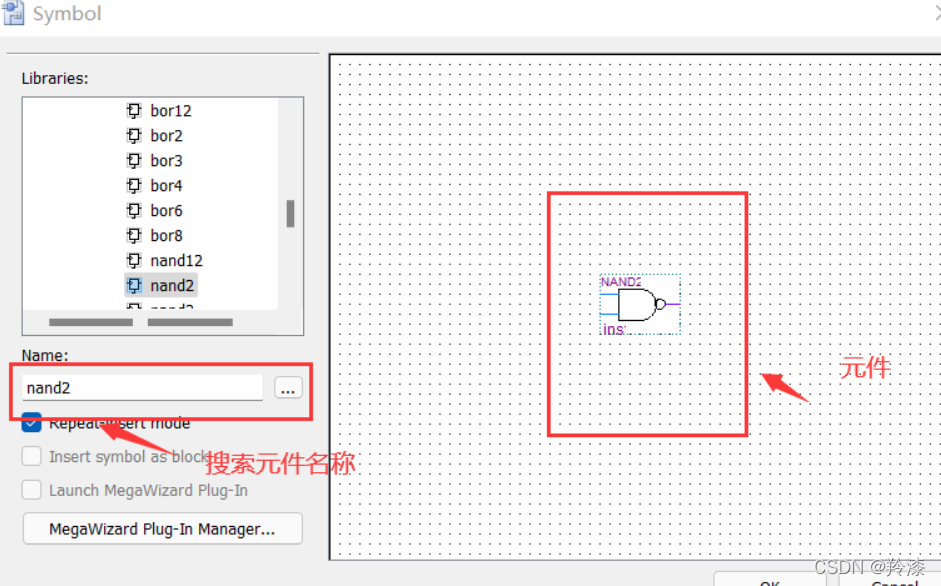

- 选择元器件

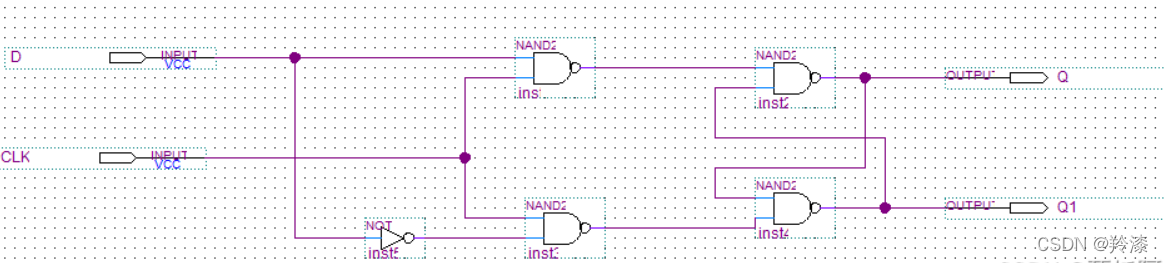

- 完成下图的元件连接

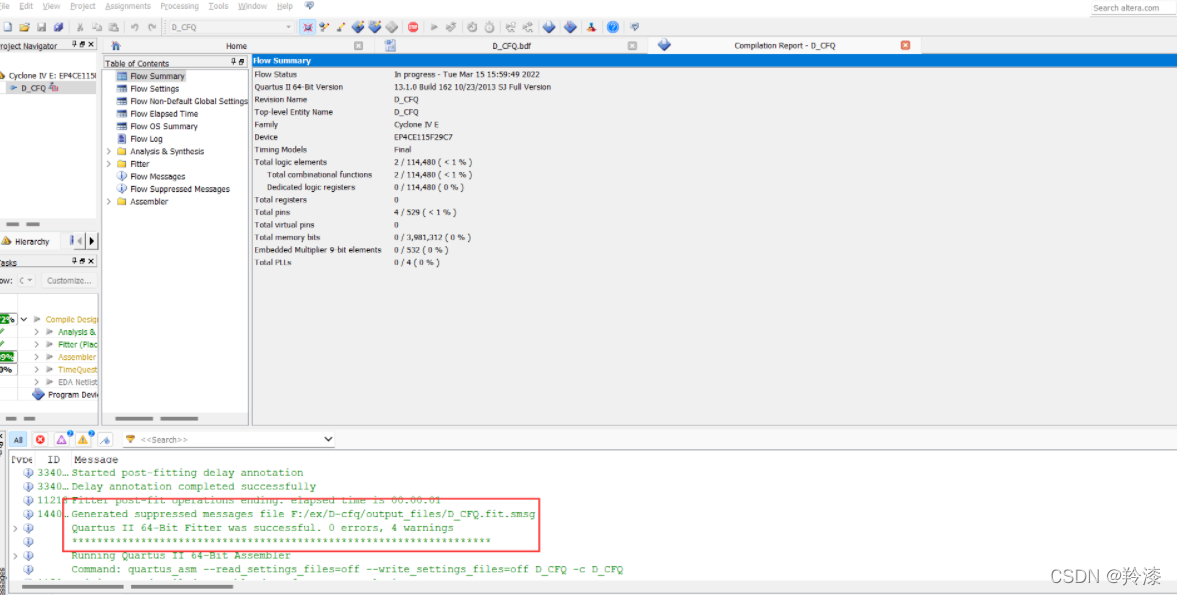

- 然后点击上面的紫色小箭头进行编译,有些警告没什么,只要没有红色的错误就能过

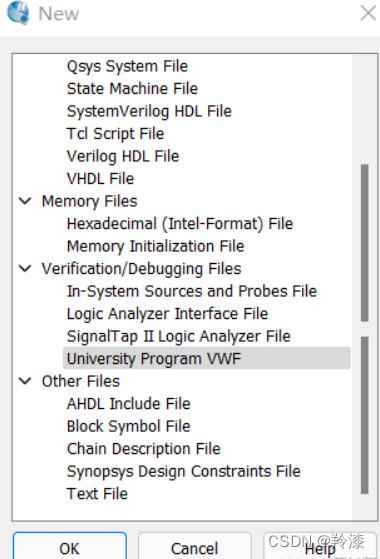

- 选择file–>new,选择VWF文件

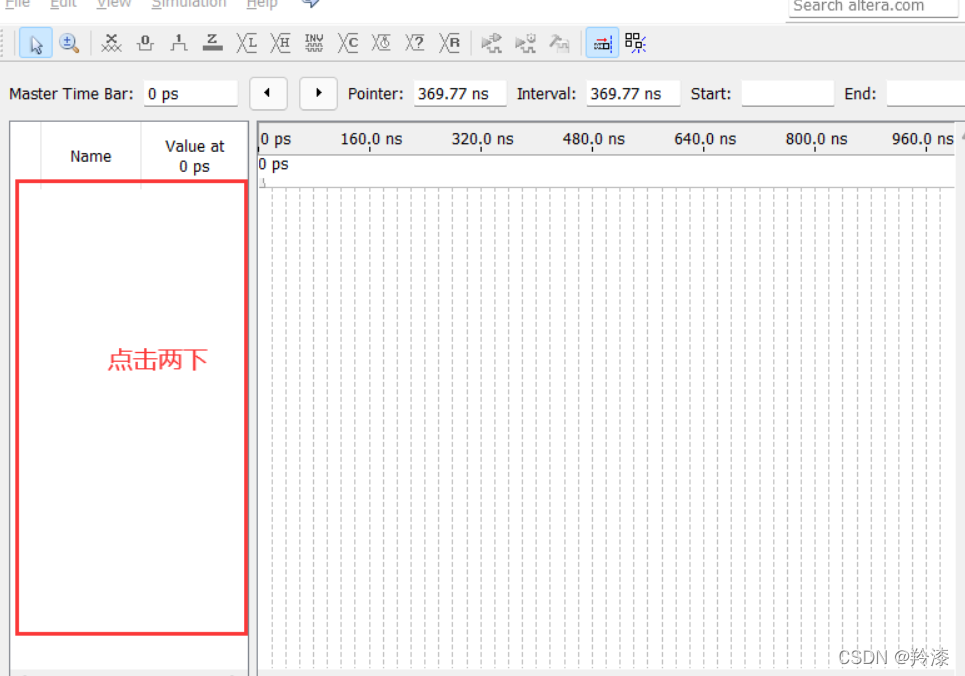

- 点击旁边的空白处,会出现插入界面,再点击node finder

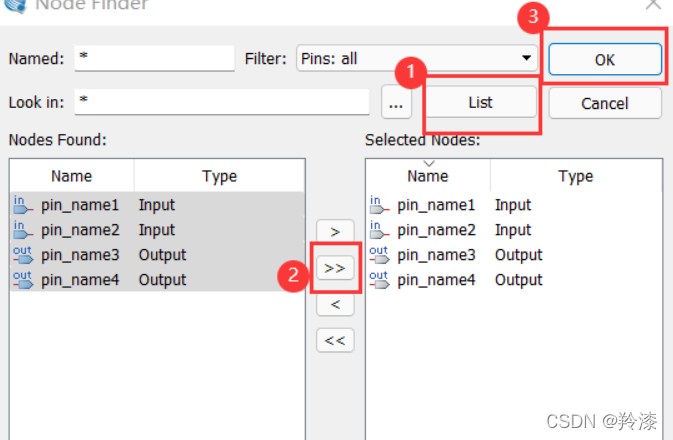

- 进去之后选择pin all,点击list,再点击>>就会将发现的引脚全部选上,最后选择OK

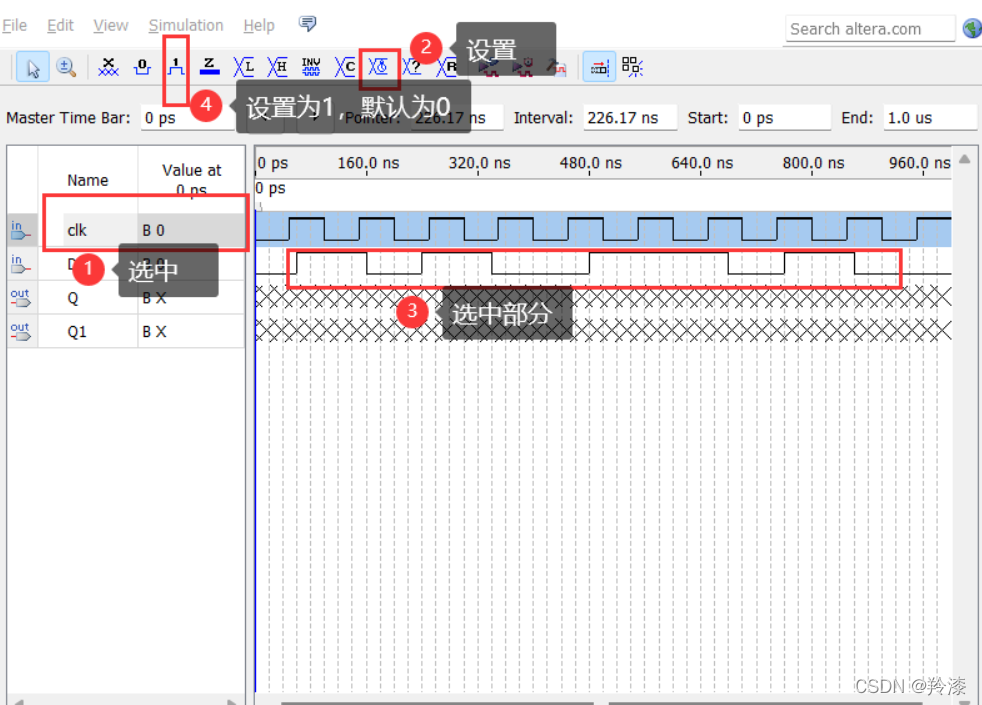

- 设置波形

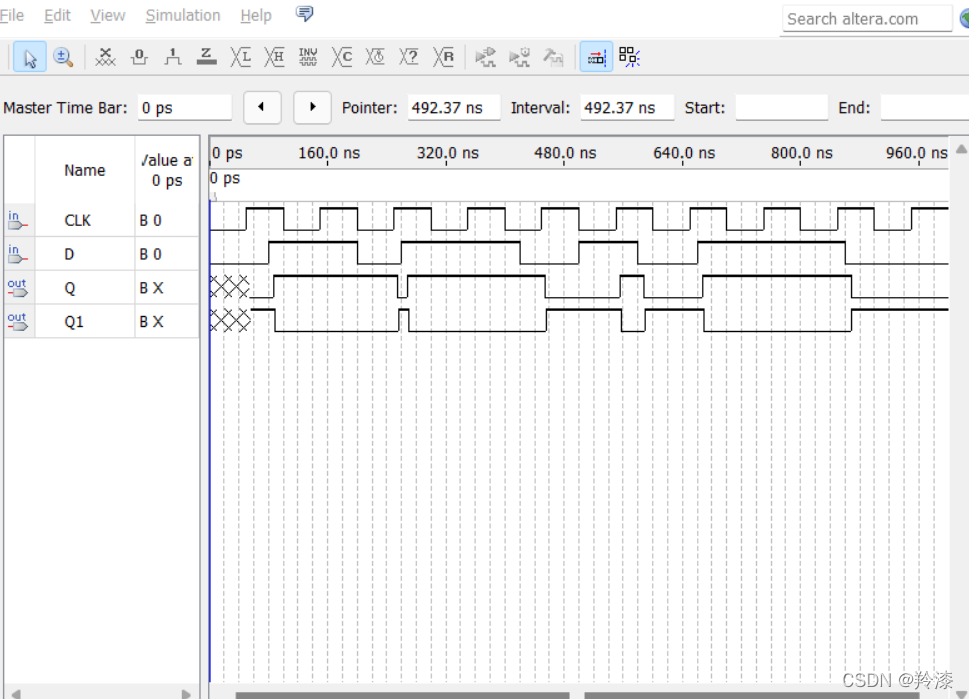

- 仿真结果,观察结果,波形变化具有时延

四、调用D触发器仿真

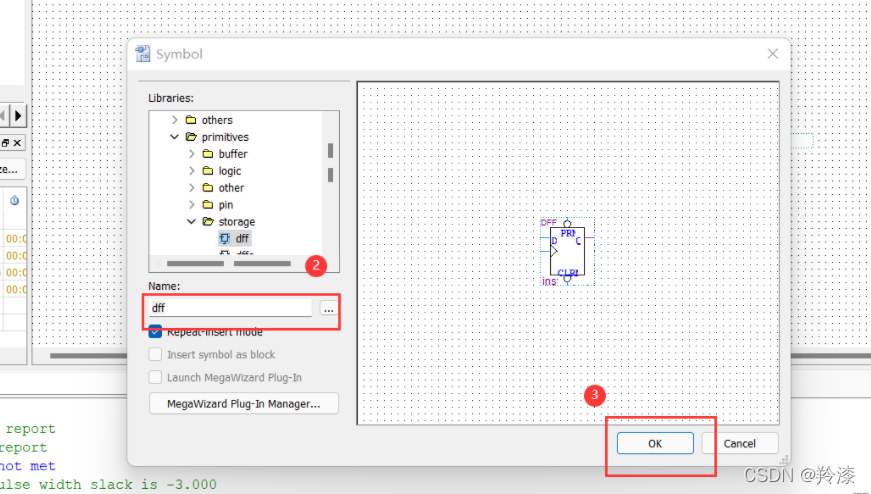

- 这里创建工程的步骤都是一样的,也一样需要先创建一个内部原理图,直接点击那个小插头,搜索dff,调用D触发器

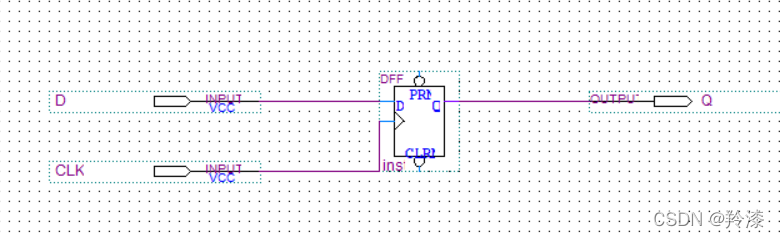

- 连线元件后如下图,连线完成后保存

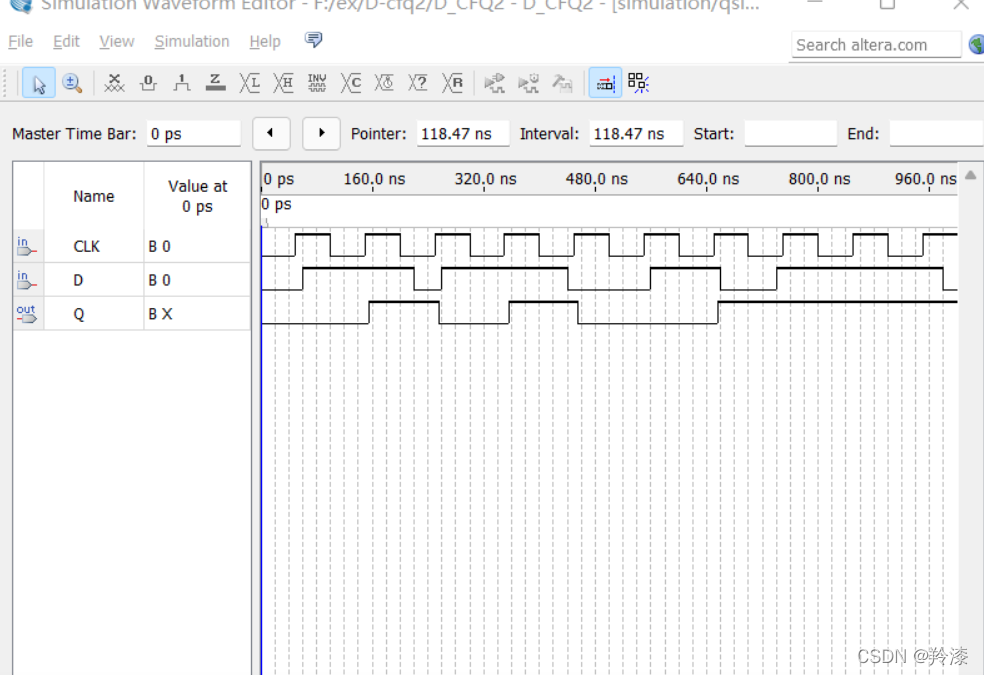

- 仿真结果

五、总结

两种方法都可以仿真成功,对比可知基本没有什么区别,都具有时延,看原理图会对其结构和原理更加直观。

923

923

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?