AW 和AR channel的 signal field 基本是相同的。

| Signal | Description |

| AxID[x:0] | Each transaction channel has its own transaction ID 每个transaction的唯一标识,AW /AR / B / R channel 都有 ID signal 对于一个read request,产生read data的模块,其产生的R ID 需要跟 收到的AR ID一致。Write request类似。 |

| AxADDR[x:0] | A burst must not cross a 4KB address boundary. |

| AxLEN[7:0] | The AXI protocol is burst-based. 也就是说 一个transaction的长度可以远大于 数据位宽,传输 全部的数据 需要多拍完成。比如 transaction length = 128byte,数据位宽为32byte,则 需要传4拍,则AxLEN = 3. (因为一个transaction至少需要1拍,AXI协议中 AxLEN = 0代表 实际 Burst Length = 1) AXI3 支持的 AxLEN 有4bit ,也就是transaction的 Burst length 取值范围为[1- 16]。AXI4 支持 8bit,transaction的 Burst length 取值范围为[1- 256] For wrapping bursts, the burst length must be 2, 4, 8, or 16. A burst must not cross a 4KB address boundary. |

| AxSIZE[2:0] | The maximum number of bytes to transfer in each data transfer, or beat, in a burst 一般情况下,都等于 接口的数据位宽,1拍可以传输的 数据的 最大量 位宽 = 2 ^ AxSIZE byte。因为 AxSIZE有3bit,故 最大支持的 位宽为 2^7 = 128byte |

| AxBURST[1:0] | Burst type, indicates how address changes between each transfer 可配置为FIXED、INCR、WRAP,详细的 解释如下 |

| AxLOCK[0:0] | AXI3 AxLOCK有两bit,AXI4 只保留了1bit。AXI4 删除了 对lock request的支持。 AXI3 :00 normal request, 01 exclusive request ; 10 locked request AXI4 : 0 normal request 1 exclusive request。 The AxLOCK signals select exclusive access, and the RRESP and BRESP signals indicate the success or failure of the exclusive access read or write respectively. |

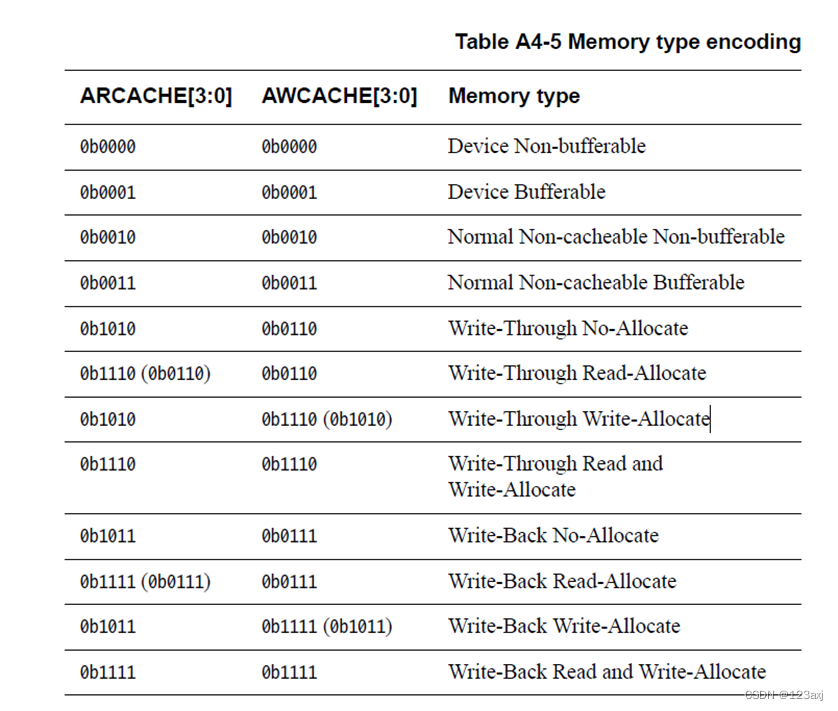

| AxCACHE[3:0] | Memory type (write through / write back / allocate / cacheable / bufferable) encoding, 对于每一个transaction,其在cache、memory中的行为都可以通过AxCACHE来进行区别处理。 |

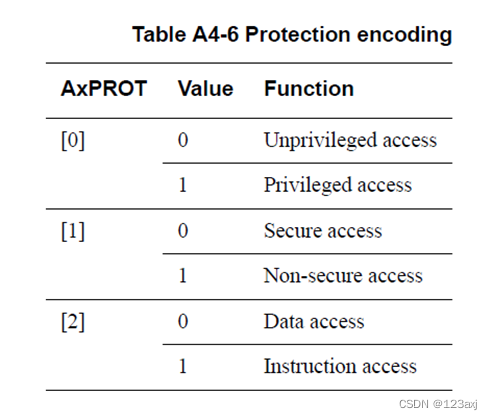

| AxPROT[2:0] | Protection attributes of transaction: privilege, security level, and access type (instruction or data). |

| AxQoS | AXI4 add。Quality of Service identifier for a transaction |

| AxREGION | AXI4 add。 |

| AxUSER | AXI4 add。User-defined extension,可以添加一些自定义的field |

W channel signal

| Signal | Description |

| WID[x:0] | Each transaction channel has its own transaction ID |

| WDATA[x:0] | Write data |

| WSTRB[x:0] | Write strobes, indicate which byte lanes hold valid data |

| WLAST[0:0] | Indicates whether this is the last data transfer in a write transaction |

| WUSER[x:0] | AXI4 add。User-defined extension for the write data channel. |

B channel signal

| Signal | Description |

| BID[x:0] | Each transaction channel has its own transaction ID |

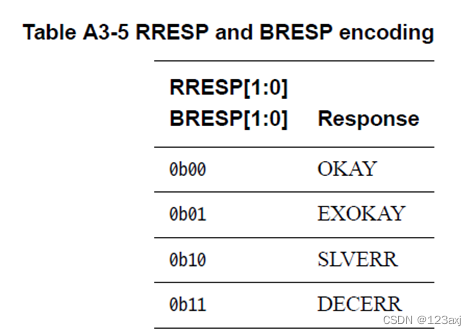

| BRESP[1:0] | Write response, indicates the status of a write transaction. Manager和Subordinate 等同于 分别为 master 和slave模块 OKAY: Normal access success. Indicates that a normal access has been successful. Can also indicate that an exclusive access has failed. EXOKAY : Exclusive access okay. Indicates that either the read or write portion of an exclusive access has been successful. SLVERR: Subordinate error. Used when the access has reached the Subordinate successfully, but the Subordinate wishes to return an error condition to the originating Manager. DECERR : Decode error. Generated, typically by an interconnect component, to indicate that there is no Subordinate at the transaction address |

| BUSER | AXI4 add。User-defined extension. |

R channel signal

| Signal | Description |

| RID[x:0] | Each transaction channel has its own transaction ID |

| RDATA[x:0] | Read data |

| RRESP[1:0] | read response, indicates the status of a write transaction. 类似 BRESP |

| RLAST[0:0] | 类似WLAST。Indicates whether this is the last data transfer in a read transaction |

| BUSER | AXI4 add。User-defined extension. |

本文详细介绍了AXI(Advanced eXtensible Interface)总线协议的AW(写地址)、AR(读地址)、W(写数据)、B(写响应)和R(读数据)通道的信号字段,包括它们的功能、作用和使用场景。例如,AxLEN用于指定传输的BurstLength,AxSIZE定义了每次数据传输的字节数,而AxBURST则指示地址如何在每次传输间变化。此外,还提到了AXI3与AXI4之间的差异,如AXI4增加了AxQoS和AxREGION信号,并简化了AxLOCK。

本文详细介绍了AXI(Advanced eXtensible Interface)总线协议的AW(写地址)、AR(读地址)、W(写数据)、B(写响应)和R(读数据)通道的信号字段,包括它们的功能、作用和使用场景。例如,AxLEN用于指定传输的BurstLength,AxSIZE定义了每次数据传输的字节数,而AxBURST则指示地址如何在每次传输间变化。此外,还提到了AXI3与AXI4之间的差异,如AXI4增加了AxQoS和AxREGION信号,并简化了AxLOCK。

1617

1617

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?