一、NAND基本原理

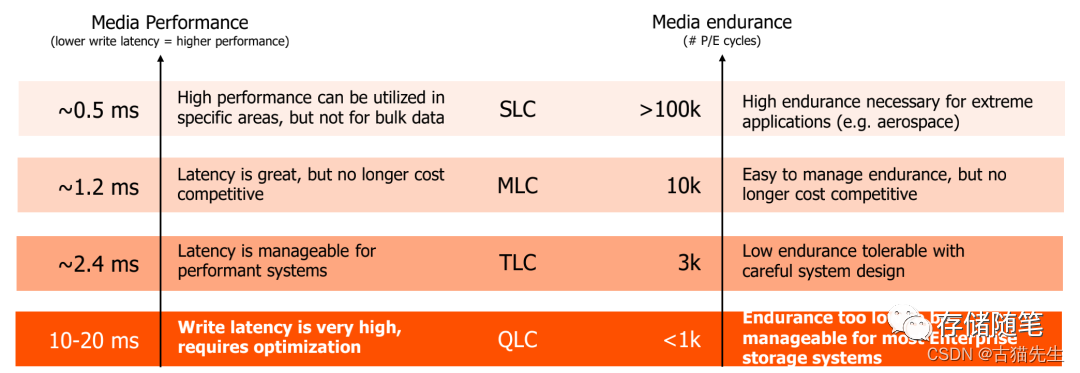

目前NAND已经从SLC发展到PLC,但是PLC离大规模上市还有一段距离,我们暂时先略过。市面上主要流通的就是4种NAND类型:SLC、MLC、TLC、QLC。随着每个寿命从高到低依次是SLC>MLC>TLC>QLC.

随着单个cell含有的bit数越多,NAND的可靠性也会有所降低。同时写延迟也在不断地增加。SLC写延迟在0.5ms级别,到QLC写延迟达到10-20ms,40倍的差距。这也导致QLC SSD性能出现很大的下降。

介绍完NAND cell的状态,再来show一下NAND的基本操作(以最简单的SLC为例)。

读(Read):

如上图所示,这是对单一cell进行read的基本操作。在控制栅极(CG, 也是WL)加上0V的电压,源极(Source)端加上0V以及漏极(Drain, 也是BL)加上1V,然后通过源极与漏极之间电流Icell的大小来判断cell的状态(0或者1)。

A点的状态代表存在Icell,所以Cell处于“开态”(ON),称为Erased;

B点的状态代表不存在Icell或者Icell很小且可忽略,所以Cell处于“关态”(OFF),称为Programmed。

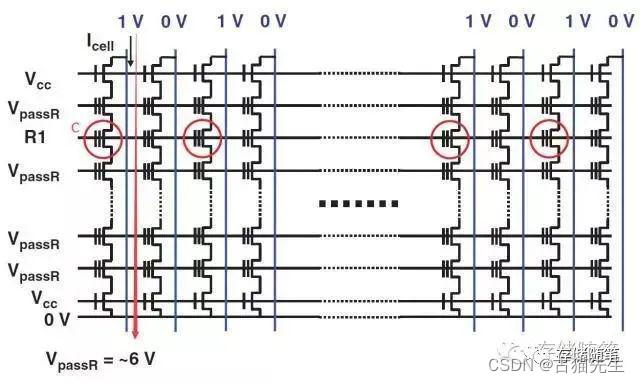

如果对NAND cell阵列操作,原理图如下:

如果Cell C处于Erased, 对应BL的Sense电路会感应到有电流;

在需要read的target Page的WL上面加一个R1(一个较小的电压),其他WL的加VpassR, BL方向加1V,

如果Cell C处于Programmed, 对应BL的Sense电路不会感应到有电流。

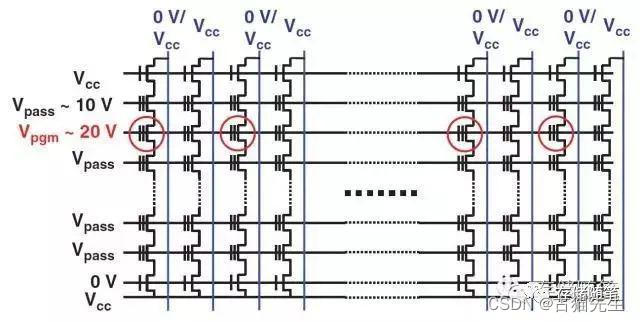

写(Program):

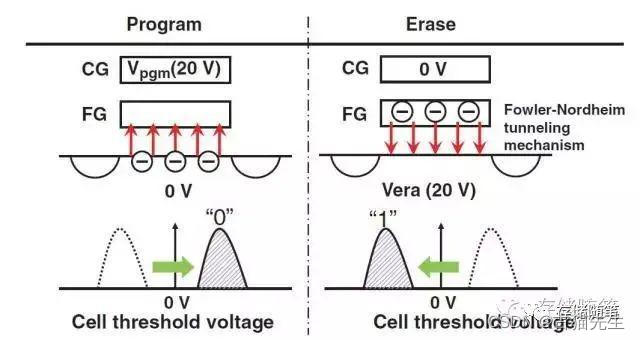

在控制栅CG加上一个高压20V,基底接0V, 由于电场的存在以及隧穿效应,电子会被俘获在浮栅FG,也就完成了单个Cell的Program操作。Program之后cell的状态为“0”。

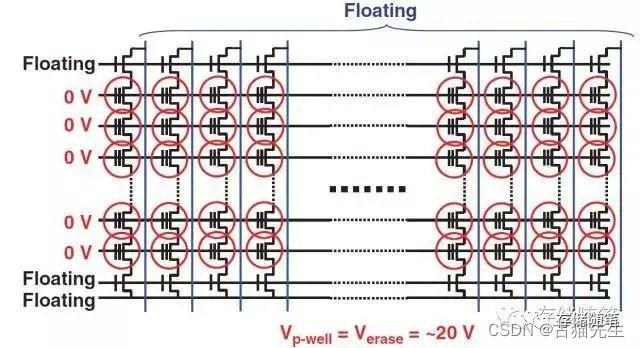

擦除(Erase):

在控制栅CG接0V,基底加上一个高压20V, 由于电场的存在以及隧穿效应,电子逃离浮栅FG,也就完成了单个Cell的Erase操作。Erase之后cell的状态为“1”。

需要注意的是,Read、Program都是以Page为最小基本操作单位,而Erase以Block为最小基本操作单位。

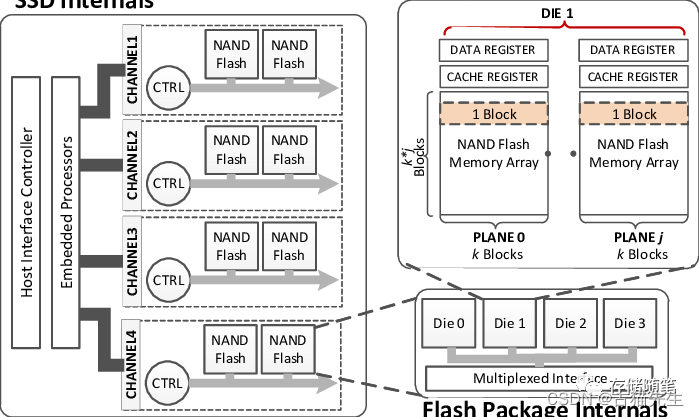

二、SSD基本原理

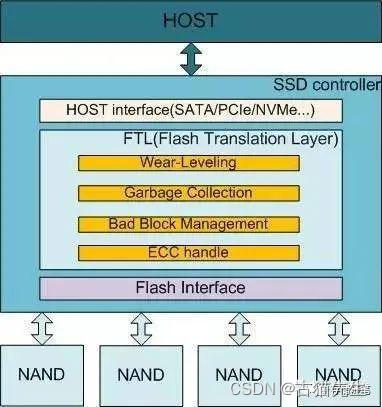

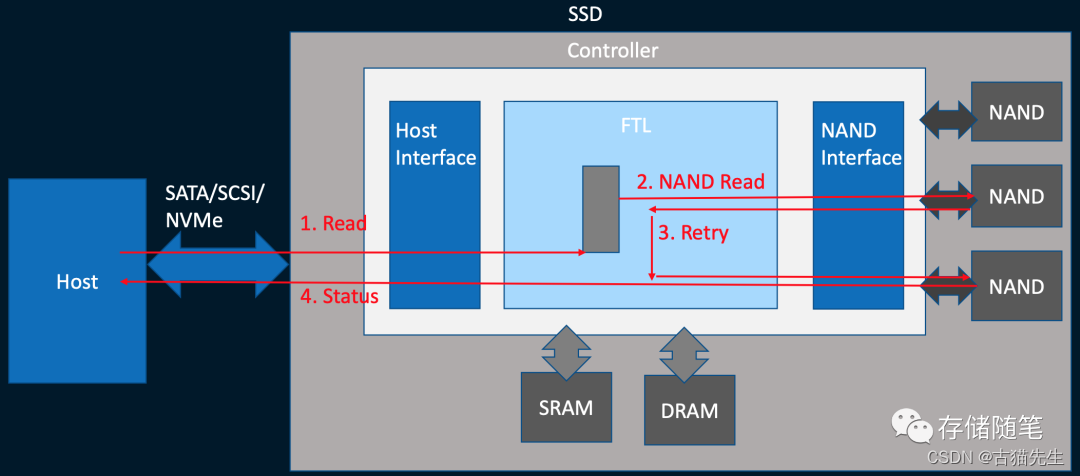

目前主流SSD主控架构如下图:

主要由三大部分组成:与Host对接的界面(Host interface), 闪存转换层FTL以及闪存对接界面(Flash interface)。

-

Host interface采用的协议(protocol)包括SATA,PCIe/NVMe SSD协议。

-

闪存转换层FTL是主控的核心部分,主要实现磨损平衡(Wear-leveling), 垃圾数据回收(Garbage Collection), 坏块管理(Bad Block Management)和数据纠错处理(ECC, Error Correction Code)。

Flash interface包括了SSD主控的flash controller,用来控制主控与NAND闪存之间的数据传输。

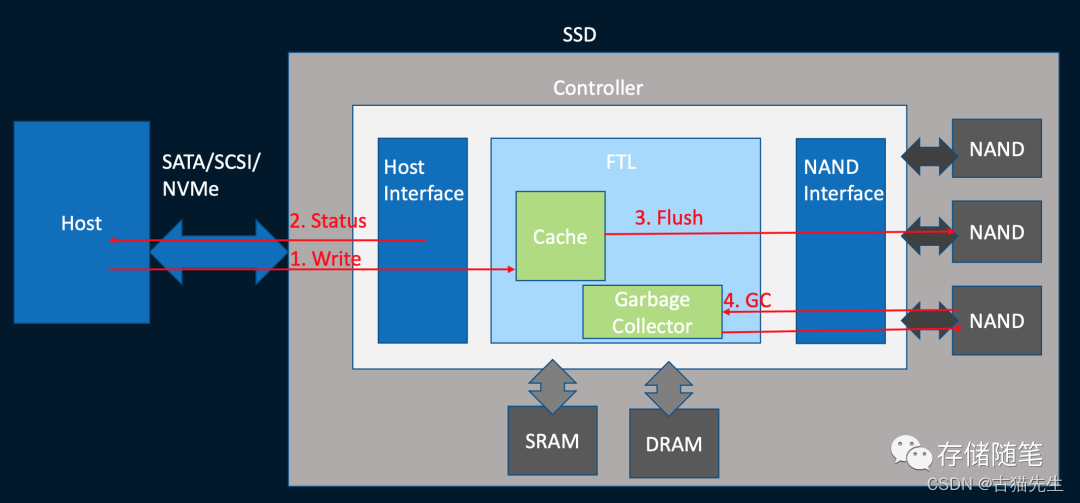

SSD IO数据写入的过程:

写入过程中,host写入数据给到缓存,再由缓存下刷到NAND存储,需要注意的是写入数据后的垃圾回收GC。

SSD IO数据读取的过程:

读取过程中,host发送数据读取请求,数据从NAND读取,这个过程可能会有因为NAND读取异常发送Read Retry。

三、SSD QoS性能优化

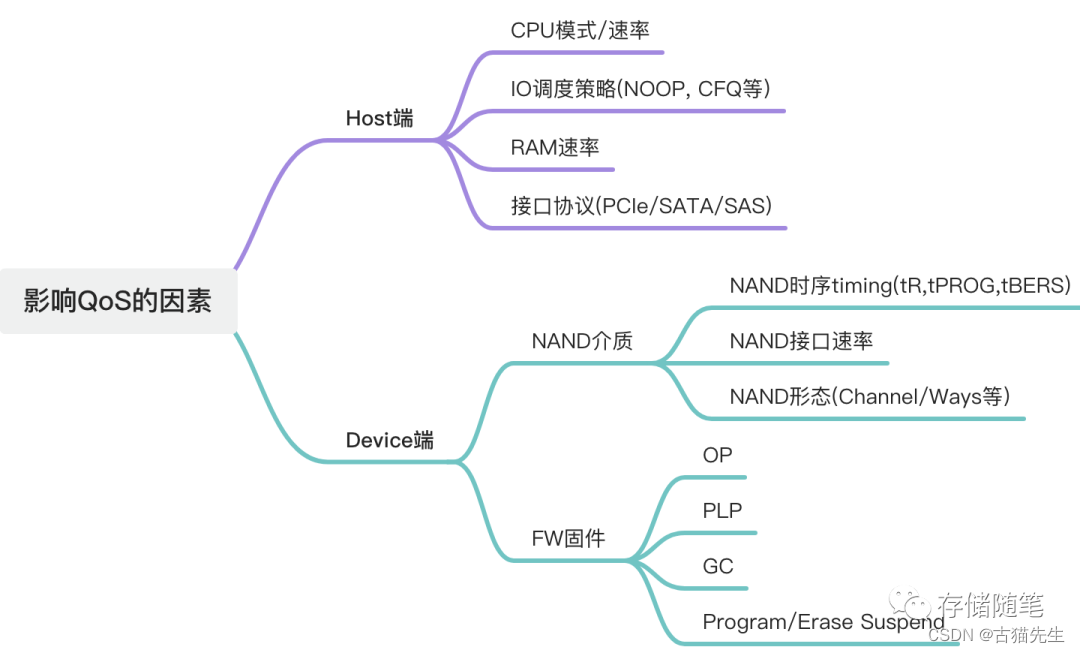

SSD性能评估中,QoS(Quality of Service, 服务质量)是重中之重,代表SSD性能的稳定性的指标。QoS评价参数中,有平均延迟、99% QoS,99.9% QoS,99.99% QoS,99.999% QoS等,9越多,说明对延迟的稳定性要求就越高。影响QoS的主要因素总结如下:

1.Host端的影响因素

Host端CPU/缓存的资源对IO质量QoS也有比较大的影响,这块通常不是瓶颈,在部分特殊场景,比如CPU soft lockup,内存资源溢出OOM等,系统的IO响应也会出现很大的波动。

同时内核block层的IO调度器的设定,决定IO的响应策略差异:

-

NOOP算法,是内核IO调度算法中最简单的一种,也被称作电梯算法,这些 FIFO先进先出策略,这个过程会适当对连续的IO进行简单的合并。

-

CFQ算法,全称Completely Fair Queuing,最大的特点就是尽可能把每个IO进程响应做到公平。从内核2.6.18也成为了linux默认的算法。

-

Deadline算法,主要的特别是确保每个IO进程在一段时间内被处理完,防止单个IO被等待太久没有影响。

本文全面解析SSD的NAND基本原理、SSD工作原理及QoS性能优化。讨论了Host端和Device端的影响因素,如NAND读写时间、ECC纠错、3D-NAND工艺等,强调了QoS在衡量SSD性能稳定性中的重要性,并探讨了优化策略。

本文全面解析SSD的NAND基本原理、SSD工作原理及QoS性能优化。讨论了Host端和Device端的影响因素,如NAND读写时间、ECC纠错、3D-NAND工艺等,强调了QoS在衡量SSD性能稳定性中的重要性,并探讨了优化策略。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4261

4261

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?